# Hybrid Amorphous-Selenium/CMOS Low-Light Imager

by

## Yunzhe Li

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical & Computer Engineering

Waterloo, Ontario, Canada, 2018

© Yunzhe Li 2018

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

This thesis aims to demonstrate a low-light imager capable of moonlight-level imaging by combining a custom-designed complementary-metal-oxide-semiconductor (CMOS) pixel array with amorphous selenium (a-Se) as its photosensor. Because of the low dark current of a-Se compared to standard silicon photodiodes, this hybrid structure could enable imagers fabricated in standard mixed-signal CMOS processes to achieve lowlight imaging. Such hybrid imagers could have low-light performances comparable to other low-light imagers fabricated in specialized CMOS image-sensor processes.

The 320 (H) x 240 (V) imager contains four different pixel designs arranged in four quadrants, with pixel pitches of 7.76  $\mu$ m x 7.76  $\mu$ m in quadrants 1 to 3 and 7.76  $\mu$ m x 8.66  $\mu$ m in quadrant 4 (Q4). The different quadrants are built to examine various performance-enhancing circuit designs and techniques, including series-stacked devices for leakage suppression, charge-injection suppression that uses dummy transistors, and a programmable dual-capacity design for extended pixel dynamic range. The imager-performance parameters, such as noise, dynamic range, conversion gain, linearity, and full-well capacity were simulated and experimentally verified. This work will also describe the external hardware and software designs used to operate the imager. This thesis summarizes and reports the overall electrical and optical performance of pixels in quadrant 1. The observed signal-to-noise ratio (SNR) of above 20 dB at an illuminance of 0.267 lux demonstrates that the imager can produce excellent images under moonlight-imaging conditions. This was achieved mainly through utilization of the long integration time enabled by circuit techniques implemented at the pixel level, as well as the low dark current of a-Se.

#### Acknowledgements

I would like to thank my parents Cindy and James, my sister Yudi, my loyal friend Leo, and my girlfriend Tong, for their love and support.

I would also like to thank professor Karim S. Karim and professor Peter M. Levine for the guidance, patience and their trust they've given me throughout my studies. A special thanks to professor John R. Long and professor Slim Boumaiza for reading my thesis and providing valuable feedbacks.

Lastly, I would like to thank my friends and colleagues at the University of Waterloo who made my time there so memorable. I offer a special thanks to the members of the STAR research group: Ahmet Camlica, Celal Con, Abdallah El-Falou, Jerry Liang, Sebastian Maurino, Alireza Parsafar, and the future Dr. Chris Scott, for their ongoing help and support. Another special thanks goes to my friends, Ben Chang, Sakib Imtiaz, Stanley Ituah, Adam Gomes, Aman Muthreja, Takin Tadayon Yiling Xu, and Lily Zheng for the fun memories and their companionship.

#### Dedication

This thesis is dedicated to the ones I love.

# **Table of Contents**

| Li | ist of Tables xi    |         |                                                              |  |    |  |

|----|---------------------|---------|--------------------------------------------------------------|--|----|--|

| Li | List of Figures xii |         |                                                              |  |    |  |

| 1  | Intr                | oductio | n                                                            |  | 1  |  |

|    | 1.1                 | Low-I   | ight Imaging                                                 |  | 2  |  |

|    | 1.2                 | Digita  | l-Imaging Technology Overview                                |  | 4  |  |

|    |                     | 1.2.1   | Photosensors                                                 |  | 4  |  |

|    |                     |         | 1.2.1.1 Silicon Photodiodes                                  |  | 5  |  |

|    |                     |         | 1.2.1.2 Amorphous Selenium Photoconductors                   |  | 6  |  |

|    |                     | 1.2.2   | CMOS Readout Electronics                                     |  | 8  |  |

|    |                     |         | 1.2.2.1 Imaging Technology Overview                          |  | 8  |  |

|    |                     |         | 1.2.2.2 Silicon-Photosensor CMOS Imager vs Hybrid CMOS agers |  | 8  |  |

|    | 1.3                 | Perfor  | mance Metrics                                                |  | 10 |  |

|    |                     | 1.3.1   | Conversion Gain                                              |  | 10 |  |

|    |                     | 1.3.2   | Noise                                                        |  | 11 |  |

|    |                     | 1.3.3   | Photon Transfer Curve                                        |  | 11 |  |

|    |                     | 1.3.4   | Signal-to-Noise Ratio                                        |  | 12 |  |

|    |                     | 1.3.5   | Full-Well Capacity and Dynamic Range                         |  | 13 |  |

|    |                     | 1.3.6   | Quantum Efficiency                                           |  | 14 |  |

|   | 1.4 | Motiv  | ation and   | Objectiv          | e             |           |       | <br> | • • | <br>• | 15 |

|---|-----|--------|-------------|-------------------|---------------|-----------|-------|------|-----|-------|----|

|   | 1.5 | Thesis | organiza    | tion              |               |           |       | <br> |     |       | 16 |

| 2 | Bac | kgroun | d and Fea   | sibility <b>S</b> | Study         |           |       |      |     |       | 17 |

|   | 2.1 | CMOS   | 5 Pixel Arc | chitectur         | <b>e</b>      |           |       | <br> |     |       | 17 |

|   |     | 2.1.1  | Passive I   | Pixel Sen         | sors          |           |       | <br> |     |       | 17 |

|   |     | 2.1.2  | Active P    | ixel Sens         | ors           |           |       | <br> |     |       | 18 |

|   |     |        | 2.1.2.1     | Three Tr          | ransistor (3- | T) APS .  |       | <br> |     |       | 19 |

|   |     |        | 2.1.2.2     | Four Tra          | ansistor (4-7 | Г) APS    |       | <br> |     |       | 20 |

|   | 2.2 | Noise  |             |                   |               |           |       | <br> |     |       | 21 |

|   |     | 2.2.1  | Tempora     | l Noise           |               |           |       | <br> |     |       | 22 |

|   |     |        | 2.2.1.1     | Photon            | Shot Noise    |           |       | <br> |     |       | 22 |

|   |     |        | 2.2.1.2     | Dark Cu           | urrent Shot   | Noise (DO | CSN). | <br> |     |       | 22 |

|   |     |        | 2.2.1.3     | Therma            | l Noise       |           |       | <br> |     |       | 22 |

|   |     |        | 2.2.1.4     | Flicker I         | Noise         |           |       | <br> |     |       | 24 |

|   |     | 2.2.2  | Spatial N   | Joise .           |               |           |       | <br> |     |       | 25 |

|   |     |        | 2.2.2.1     | Under I           | Dark Condit   | tion      |       | <br> |     |       | 25 |

|   |     |        | 2.2.2.2     | Under I           | llumination   | ι         |       | <br> |     |       | 25 |

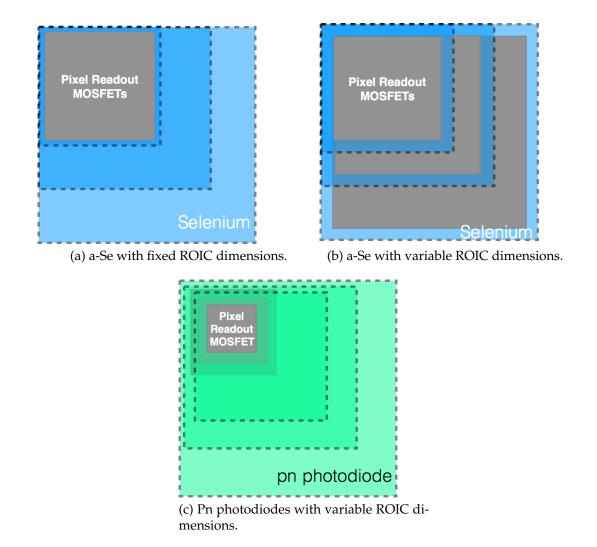

|   | 2.3 | Feasib | ility Study | <b>y</b>          |               |           |       | <br> |     |       | 26 |

|   |     | 2.3.1  | Pixel Arc   | chitectur         | e Setup       |           |       | <br> |     |       | 26 |

|   |     |        | 2.3.1.1     | A-Se Ph           | otosensors    |           |       | <br> |     |       | 28 |

|   |     |        | 2.3.1.2     | Silicon I         | Photodiode    |           |       | <br> |     |       | 29 |

|   |     | 2.3.2  | Simulate    | ed Image          | r Performar   | nce       |       | <br> |     |       | 29 |

|   |     |        | 2.3.2.1     |                   | ion Setup .   |           |       |      |     |       | 29 |

|   |     |        | 2.3.2.2     |                   | and Discuss   |           |       |      |     |       | 31 |

|   |     |        |             | 3.2.2.1           | Effect of Ir  |           |       |      |     |       | 31 |

|   |     |        |             | 3.2.2.2           | Effect of Ir  | U         | •     |      |     |       |    |

|   |     |        |             |                   |               | U         |       |      |     |       |    |

| 3 | Des | ign   |                                                           | 37 |

|---|-----|-------|-----------------------------------------------------------|----|

|   | 3.1 | CMOS  | S Imager Design                                           | 37 |

|   |     | 3.1.1 | Pixel Array                                               | 39 |

|   |     | 3.1.2 | Pixel Design                                              | 39 |

|   |     |       | 3.1.2.1 Quadrant 1 (Q1)                                   | 39 |

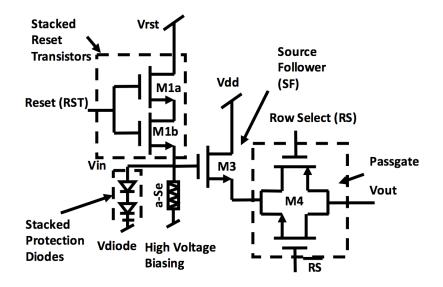

|   |     |       | 3.1.2.1.1 Series Stacked Reset and Protection Diode       | 42 |

|   |     |       | 3.1.2.1.2 Separate diode trace to reduce leakage          | 42 |

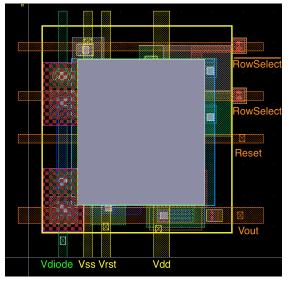

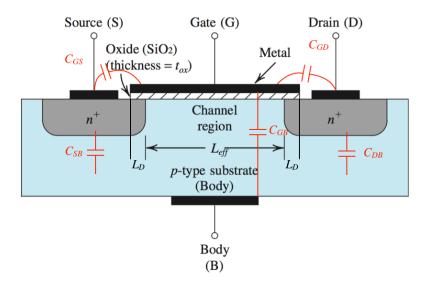

|   |     |       | 3.1.2.1.3 Parasitic Capacitance at the Integration Node 4 | 43 |

|   |     |       | 3.1.2.1.4 Timing Operation                                | 44 |

|   |     |       | 3.1.2.1.5 Pixel Gain                                      | 45 |

|   |     |       | 3.1.2.1.6 Noise                                           | 46 |

|   |     |       | 3.1.2.1.7 Full Well Capacity, Dynamic Range & Conver-     |    |

|   |     |       |                                                           | 46 |

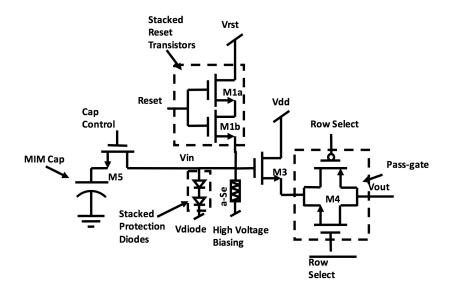

|   |     |       | 3.1.2.2 Quadrant 2 (Q2)                                   |    |

|   |     |       |                                                           | 50 |

|   |     |       | 3.1.2.4 Quadrant 4 (Q4)                                   | 52 |

|   |     | 3.1.3 | Digital Control                                           | 54 |

|   |     |       | 3.1.3.1 Scan Chain Configuration                          | 57 |

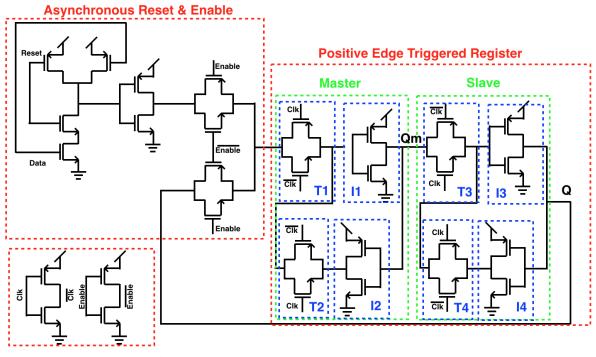

|   |     |       | 3.1.3.2 D Flip-Flop                                       | 57 |

|   |     |       | 3.1.3.2.1 Driving Strength                                | 59 |

|   |     |       | 3.1.3.2.2 Testability                                     | 60 |

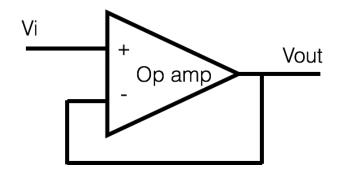

|   |     | 3.1.4 | On Chip Voltage Buffer                                    | 60 |

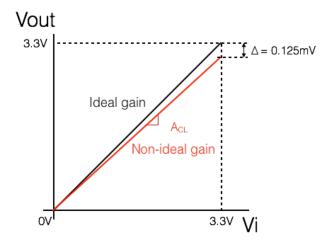

|   |     |       | 3.1.4.1 DC Gain                                           | 60 |

|   |     |       | 3.1.4.2 Slew-Rate                                         | 62 |

|   |     |       | 3.1.4.3 Input Common Mode Range                           | 63 |

|   |     |       | 3.1.4.4 Frequency Response and Stability                  | 68 |

|   |     |       | 3.1.4.5 Step Response                                     | 71 |

|   |     |       | 3.1.4.6 Layout Consideration                              | 72 |

|   |     |       |                                                           |    |

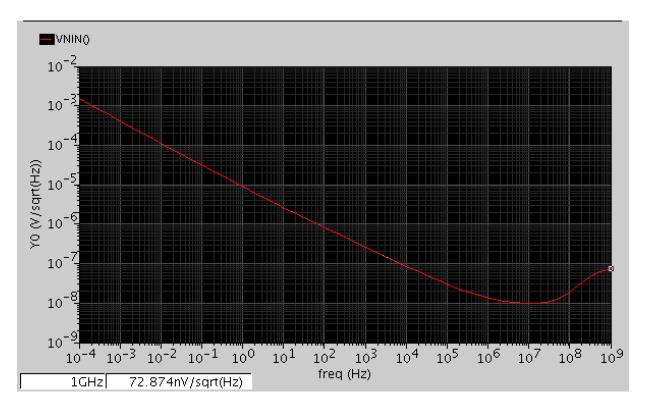

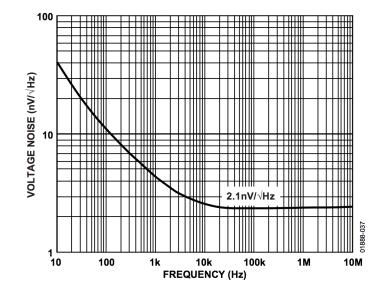

|   |                   |                                  | 3.1.4.7                                                                      | Noise                                                                                                                                                                                                            | 72                                           |

|---|-------------------|----------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

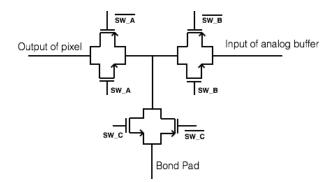

|   |                   |                                  | 3.1.4.8                                                                      | Testability                                                                                                                                                                                                      | 72                                           |

|   |                   | 3.1.5                            | I/O Pro                                                                      | tection                                                                                                                                                                                                          | 74                                           |

|   |                   | 3.1.6                            | Fabricat                                                                     | ed CMOS Imager                                                                                                                                                                                                   | 74                                           |

|   |                   |                                  | 3.1.6.1                                                                      | A-Se and Gold Deposition 7                                                                                                                                                                                       | 74                                           |

|   |                   |                                  | 3.1.6.2                                                                      | High Voltage Biasing and Epoxy Sealing                                                                                                                                                                           | 75                                           |

|   | 3.2               | Exterr                           | al Hardv                                                                     | vare                                                                                                                                                                                                             | 77                                           |

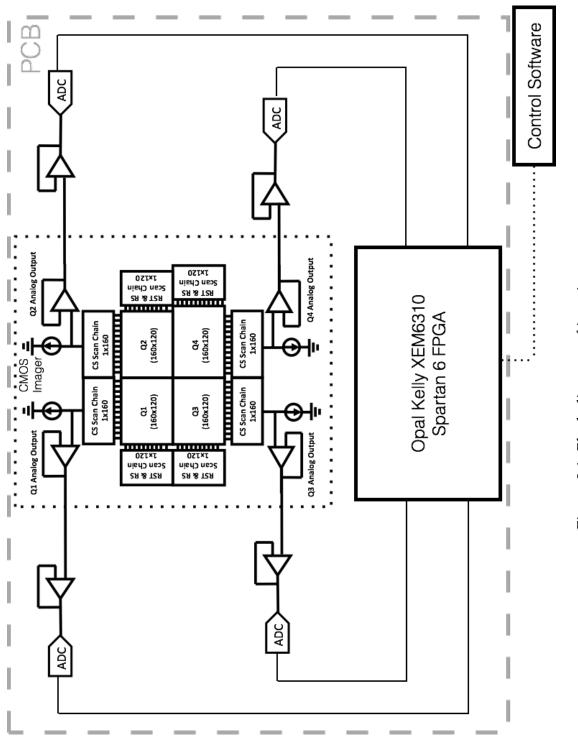

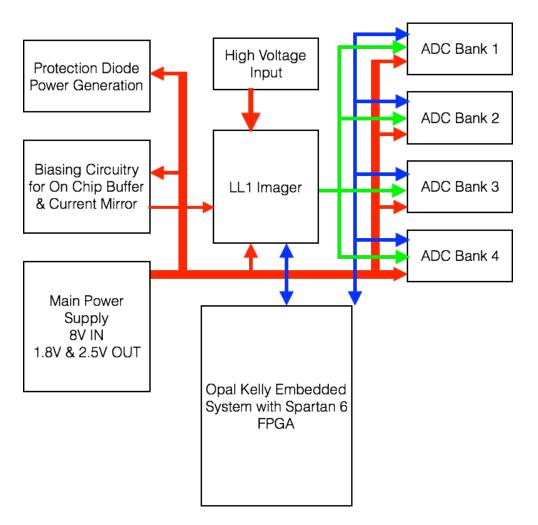

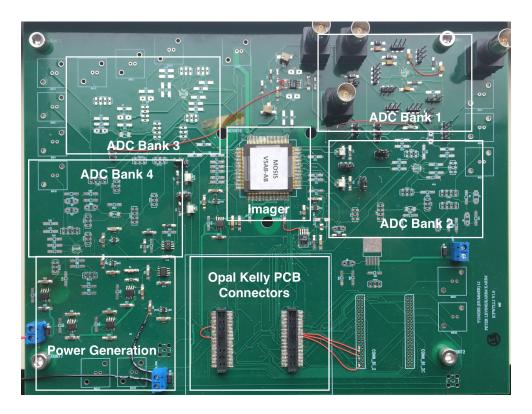

|   |                   | 3.2.1                            | PCB blo                                                                      | ck diagram                                                                                                                                                                                                       | 77                                           |

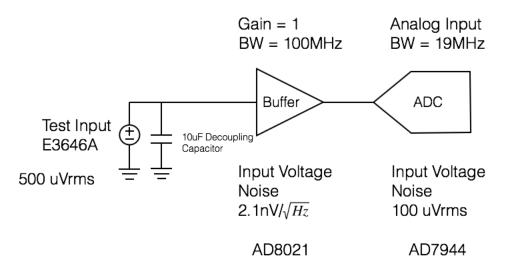

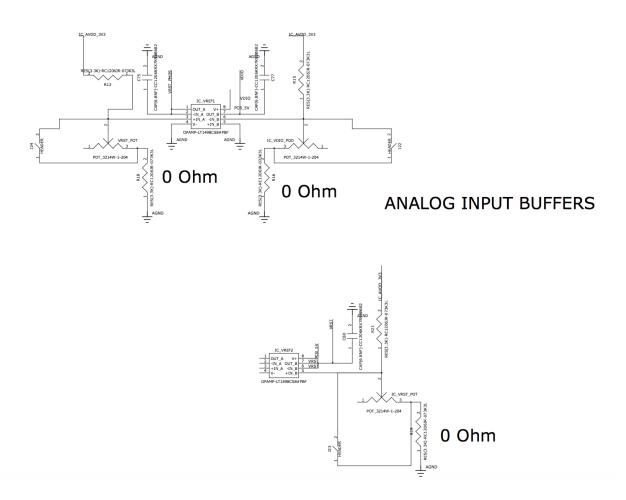

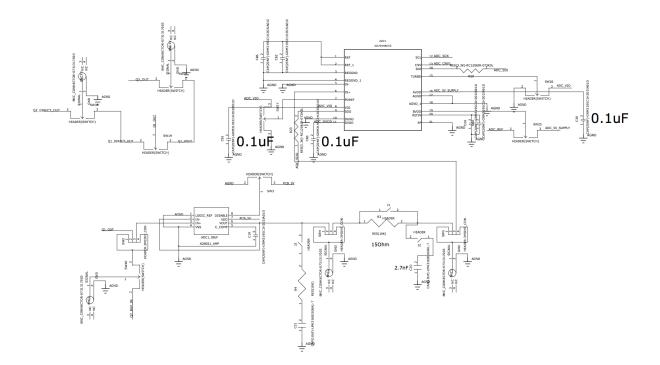

|   |                   |                                  | 3.2.1.1                                                                      | Pre-ADC Buffer                                                                                                                                                                                                   | 78                                           |

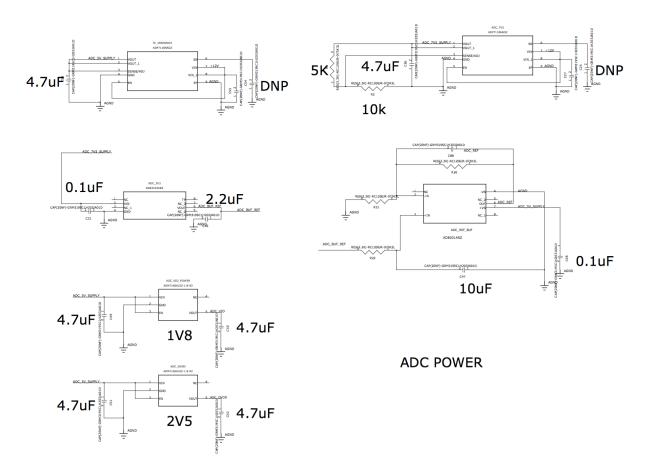

|   |                   |                                  | 3.2.1.2                                                                      | ADC                                                                                                                                                                                                              | 79                                           |

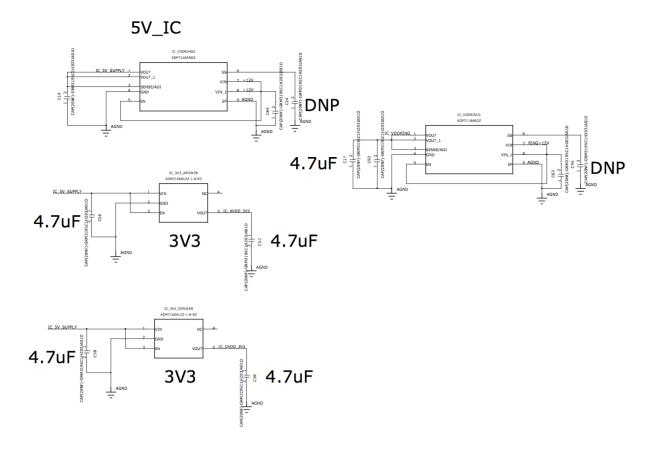

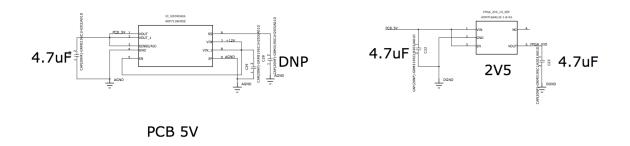

|   |                   |                                  | 3.2.1.3                                                                      | Power and Grounding Scheme                                                                                                                                                                                       | 30                                           |

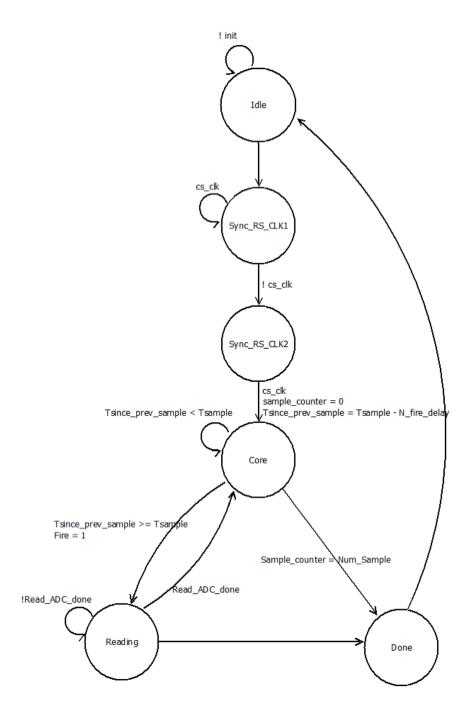

|   | 3.3               | Contro                           | ol Softwa                                                                    | re                                                                                                                                                                                                               | 31                                           |

|   |                   | 3.3.1                            | Divisior                                                                     | $\alpha$ of tasks between Verilog and C++ $\ldots$ $\ldots$ $\ldots$ 8                                                                                                                                           | 31                                           |

|   |                   | 3.3.2                            | Verilog                                                                      | Hardware Description Language 8                                                                                                                                                                                  | 32                                           |

|   |                   |                                  | 3.3.2.1                                                                      | System State Machine                                                                                                                                                                                             | 32                                           |

|   |                   |                                  |                                                                              |                                                                                                                                                                                                                  |                                              |

| 4 | Exp               | erimen                           | tal Resul                                                                    | ts 8                                                                                                                                                                                                             | 34                                           |

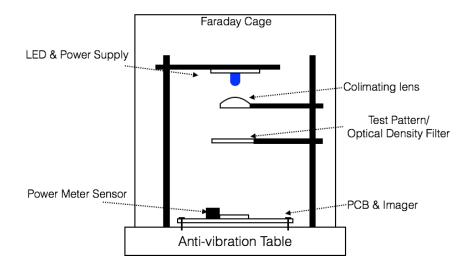

| 4 | <b>Exp</b><br>4.1 |                                  |                                                                              |                                                                                                                                                                                                                  | <b>34</b><br>34                              |

| 4 | -                 |                                  |                                                                              |                                                                                                                                                                                                                  |                                              |

| 4 | -                 | Setup<br>4.1.1                   | LED Lu                                                                       | minance Conversion                                                                                                                                                                                               | 34                                           |

| 4 | 4.1               | Setup<br>4.1.1                   | LED Lu<br>Ired Imag                                                          | minance Conversion    ٤      ger Performance    ٤                                                                                                                                                                | 34<br>35                                     |

| 4 | 4.1               | Setup<br>4.1.1<br>Measu          | LED Lu<br>Ired Imag                                                          | minance Conversion       8         ger Performance       8         ics Characterization       8                                                                                                                  | 34<br>35<br>39                               |

| 4 | 4.1               | Setup<br>4.1.1<br>Measu          | LED Lu<br>ured Imag<br>Electron                                              | minance Conversion       8         ger Performance       8         ics Characterization       8                                                                                                                  | 34<br>35<br>39<br>39                         |

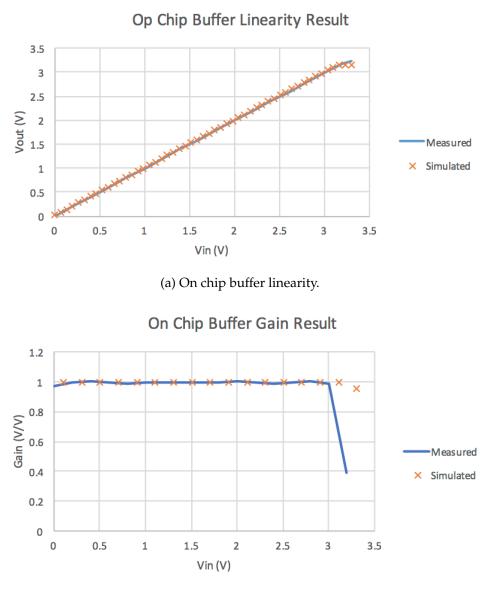

| 4 | 4.1               | Setup<br>4.1.1<br>Measu<br>4.2.1 | LED Lui<br>ured Imag<br>Electron<br>4.2.1.1<br>4.2.1.2                       | minance Conversion       8         ger Performance       8         ics Characterization       8         Noise Performance of Off-Chip Buffer and ADC       9                                                     | 34<br>35<br>39<br>39<br>90                   |

| 4 | 4.1               | Setup<br>4.1.1<br>Measu<br>4.2.1 | LED Lui<br>ured Imag<br>Electron<br>4.2.1.1<br>4.2.1.2                       | minance Conversion8ger Performance8dics Characterization8Noise Performance of Off-Chip Buffer and ADC9On Chip Buffer9Response Characterization9Pixel Linearity, Full Well Capacity and Effective Conver-         | 34<br>35<br>39<br>39<br>90                   |

| 4 | 4.1               | Setup<br>4.1.1<br>Measu<br>4.2.1 | LED Lui<br>tred Imag<br>Electron<br>4.2.1.1<br>4.2.1.2<br>Optical            | minance Conversion8ger Performance8ics Characterization8Noise Performance of Off-Chip Buffer and ADC9On Chip Buffer9Response Characterization9Pixel Linearity, Full Well Capacity and Effective Conversion Gain9 | 34<br>35<br>39<br>39<br>90<br>92<br>94       |

| 4 | 4.1               | Setup<br>4.1.1<br>Measu<br>4.2.1 | LED Lu:<br>ured Imag<br>Electron<br>4.2.1.1<br>4.2.1.2<br>Optical<br>4.2.2.1 | minance Conversion8ger Performance8ics Characterization8Noise Performance of Off-Chip Buffer and ADC9On Chip Buffer9Response Characterization9Pixel Linearity, Full Well Capacity and Effective Conversion Gain9 | 34<br>35<br>39<br>39<br>90<br>92<br>94<br>94 |

| 5  | Conclusion          |     |  |

|----|---------------------|-----|--|

|    | 5.1 Future Work     | 110 |  |

| Re | ferences            | 111 |  |

| A  | LL1 Pin Out Summary | 117 |  |

| B  | LL1 PCB Schematics  | 123 |  |

# List of Tables

| 1.1 | Common illuminance conditions                                    |

|-----|------------------------------------------------------------------|

| 2.1 | Simulation control parameters                                    |

| 2.2 | Equations used in performance simulation                         |

| 3.1 | Q1 pixel device sizing summary                                   |

| 3.2 | Gate capacitive effect in different regions. [40]                |

| 3.3 | Q1 pixel parameters comparison                                   |

| 3.4 | Q2 pixel device sizing summary                                   |

| 3.5 | Q3 pixel device sizing summary                                   |

| 3.6 | Q4 pixel device sizing summary                                   |

| 3.7 | Summary of all quadrants                                         |

| 3.8 | Op amp transistor sizing                                         |

| 4.1 | Calculated vs measured noise across integration period           |

| 5.1 | Imager performance summary and comparison with previous work 109 |

| A.1 | LL1 IC pin out summary                                           |

# **List of Figures**

| 1.1  | AM2 imager with an amorphous selenium photosensor on a CMOS read-<br>out integrated circuit (ROIC). | 2  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 1.2  | Luminance table for the human visual system.                                                        | 3  |

| 1.3  | A depletion region is formed when a PN junction is reverse biased                                   | 5  |

| 1.4  | Planar diffused p-i-n photodiode                                                                    | 6  |

| 1.5  | a-Se vertically stacked on a CMOS-readout IC                                                        | 7  |

| 1.6  | 3T pixel layout [17]                                                                                | 9  |

| 1.7  | Backside illumination cross section schematic [21]                                                  | 10 |

| 1.8  | Typical photon-transfer curve                                                                       | 12 |

| 1.9  | Images with ranging SNR                                                                             | 13 |

| 1.10 | Measured a-Se EQE across various electrical fields                                                  | 15 |

| 2.1  | PPS with charge amplifier readout circuit [29].                                                     | 18 |

| 2.2  | Schematic of voltage and current mode APS                                                           | 19 |

| 2.3  | Timing diagram of 3T voltage-mode APS                                                               | 20 |

| 2.4  | Schematic of a 4-T pinned APS [23]                                                                  | 21 |

| 2.5  | Thermal noise schematic for reset operation in 3-T pixel                                            | 23 |

| 2.6  | Simulated pixel structures                                                                          | 28 |

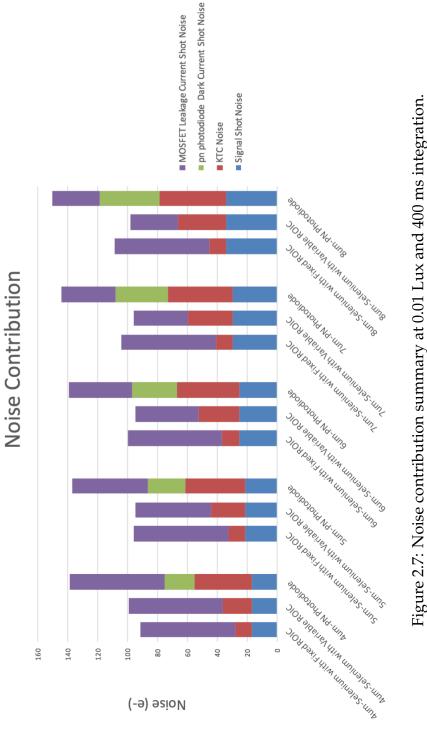

| 2.7  | Noise contribution summary at 0.01 Lux and 400 ms integration                                       | 32 |

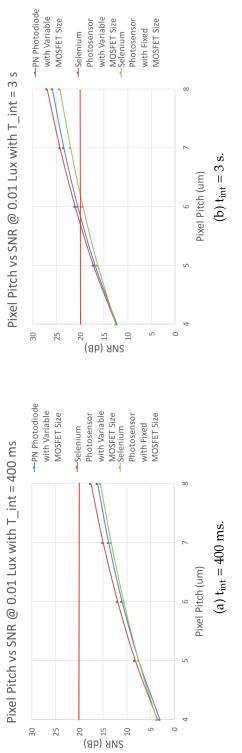

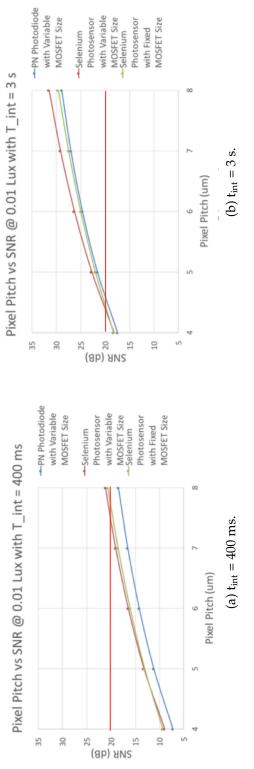

| 2.8  | Pixel pitch vs SNR at 0.01 Lux with $I_{leak} = 4fA$ , with red line indicating the target SNR.     | 35 |

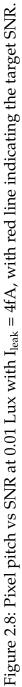

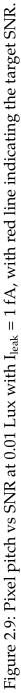

| 2.9  | Pixel pitch vs SNR at 0.01 Lux with $I_{leak} = 1$ fA, with red line indicating the target SNR. | 36 |

|------|-------------------------------------------------------------------------------------------------|----|

| 3.1  | Block diagram of imaging system.                                                                | 38 |

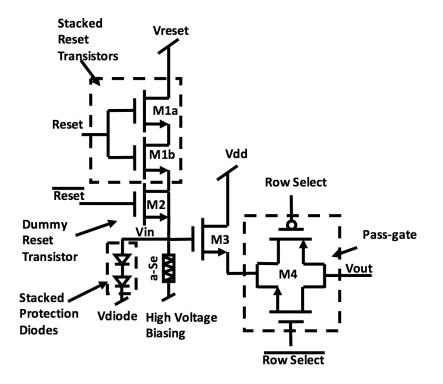

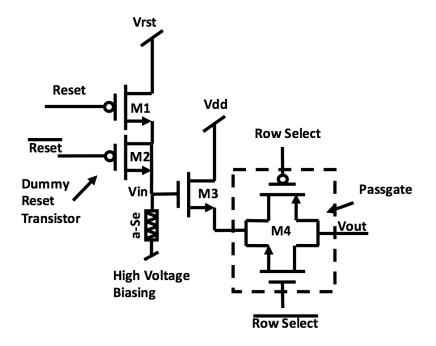

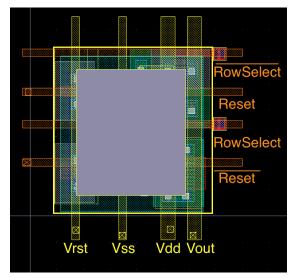

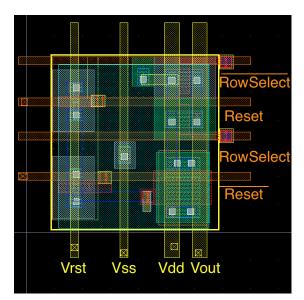

| 3.2  | Schematic of pixel design in Q1                                                                 | 40 |

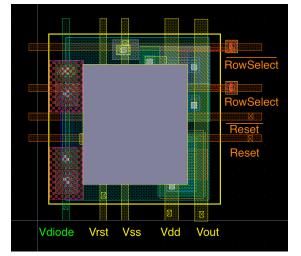

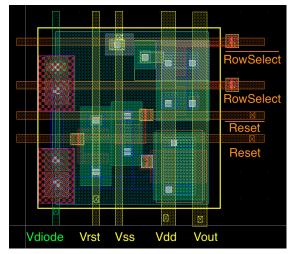

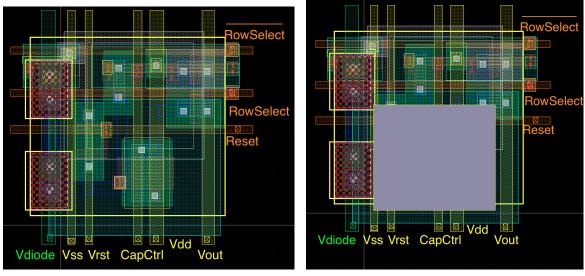

| 3.3  | Layout of pixel in Q1                                                                           | 41 |

| 3.4  | Parasitic capacitances of the MOSFET. [39]                                                      | 44 |

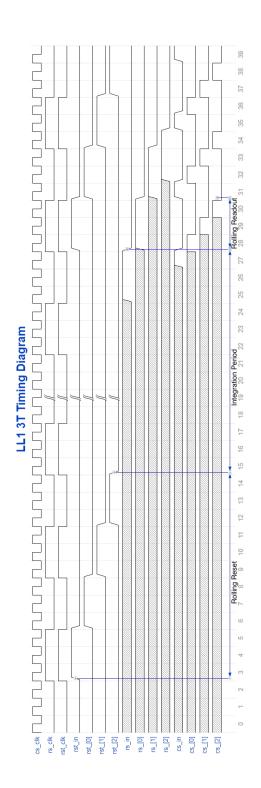

| 3.5  | Timing diagram of Q1                                                                            | 45 |

| 3.6  | Schematic of pixel design in Q2                                                                 | 49 |

| 3.7  | Layout of pixel in Q2                                                                           | 50 |

| 3.8  | Schematic of pixel design in Q3                                                                 | 51 |

| 3.9  | Layout of pixel in Q3                                                                           | 52 |

| 3.10 | Schematic of pixel design in Q4                                                                 | 53 |

| 3.11 | Layout of pixel in Q4                                                                           | 54 |

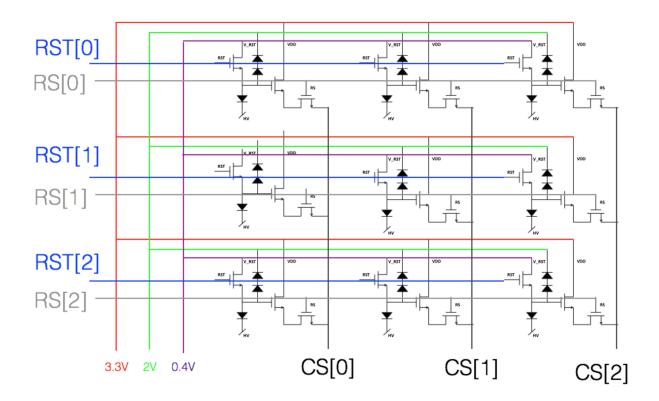

| 3.12 | 3x3 array connection illustration                                                               | 55 |

| 3.13 | Timing diagram of 3x3 array operation.                                                          | 56 |

| 3.14 | Scan chain schematic.                                                                           | 57 |

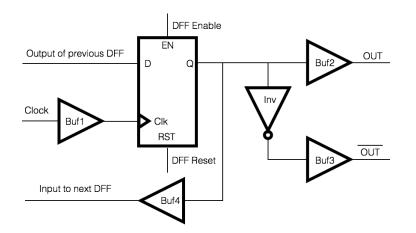

| 3.15 | D flip-flop schematic.                                                                          | 58 |

| 3.16 | Unity gain buffer created using high gain op amp                                                | 60 |

| 3.17 | Non ideal gain of unity gain buffer                                                             | 61 |

| 3.18 | Schematic of rail-to-rail op amp.                                                               | 63 |

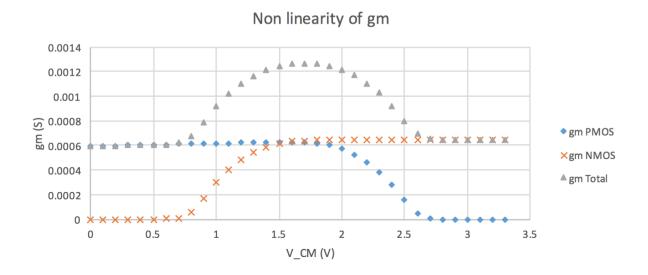

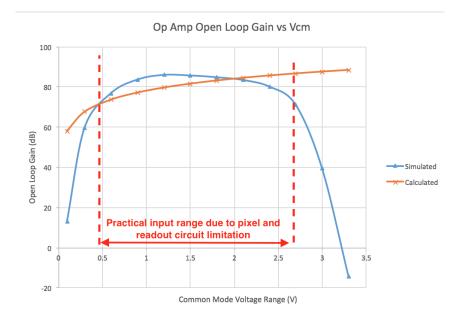

| 3.19 | Non-linearity of transconductance $g_m$                                                         | 66 |

| 3.20 | Non-linear op amp open loop gain across common mode voltage range                               | 67 |

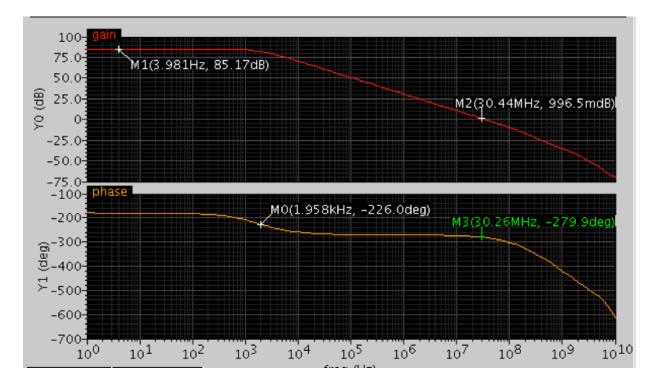

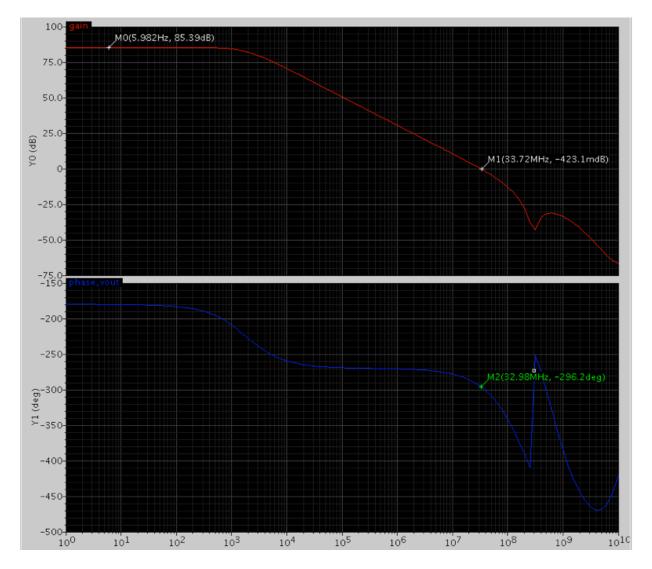

| 3.21 | Bode plot of rail-to-rail op amp open loop gain and phase at $V_{CM}$ = 1.65 V.                 | 68 |

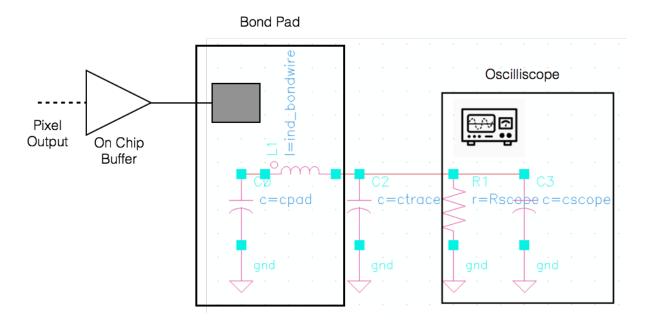

| 3.22 | Op amp realistic load.                                                                          | 69 |

| 3.23 | Bode plot of op amp with realistic load at $V_{CM}$ = 1.65 V                                    | 70 |

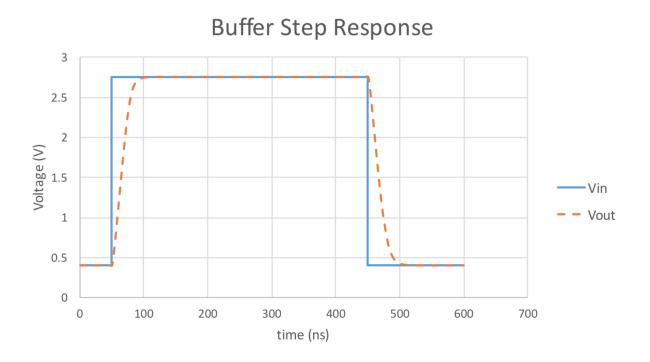

| 3.24 | Step response of on chip buffer in closed-loop configuration.                                   | 71 |

| 3.25 | Op amp simulated input noise power spectrum.                                                    | 73 |

|      |                                                                                                 |    |

| 3.26 | Three switches configuration for testability.                                                                            | 73  |

|------|--------------------------------------------------------------------------------------------------------------------------|-----|

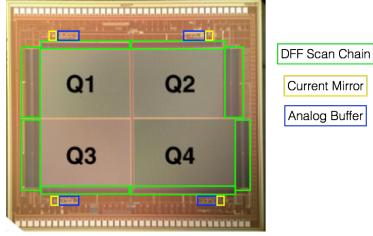

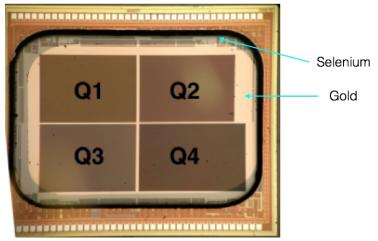

| 3.27 | Unprocessed and post processed CMOS imager                                                                               | 75  |

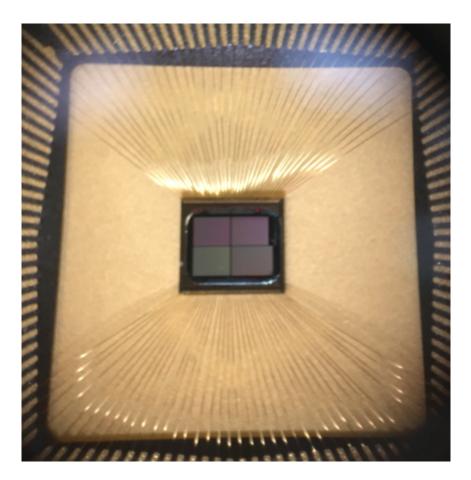

| 3.28 | Wire bonded CMOS imager                                                                                                  | 76  |

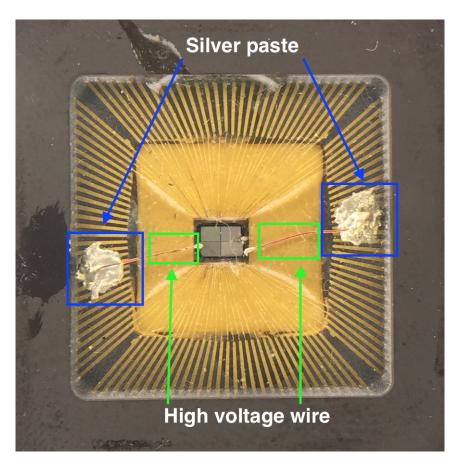

| 3.29 | High voltage connected with epoxy sealant                                                                                | 78  |

| 3.30 | External hardware block diagram.                                                                                         | 79  |

| 3.31 | Rev0 PCB used for testing                                                                                                | 80  |

| 3.32 | State machine of HDL                                                                                                     | 83  |

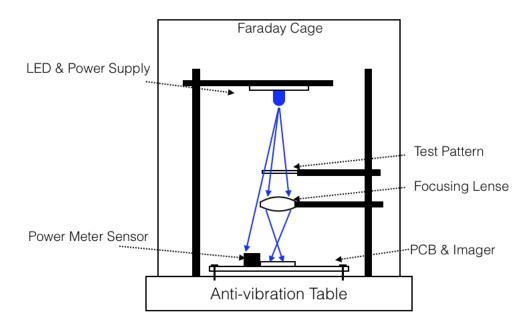

| 4.1  | Optical experiment setup.                                                                                                | 85  |

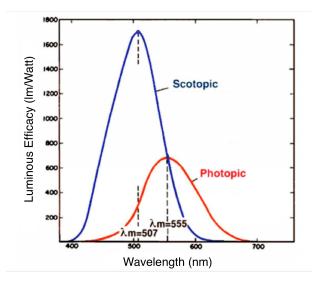

| 4.2  | Scotopic and photopic vision. [45]                                                                                       | 86  |

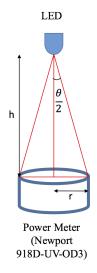

| 4.3  | Illuminance calculation setup                                                                                            | 87  |

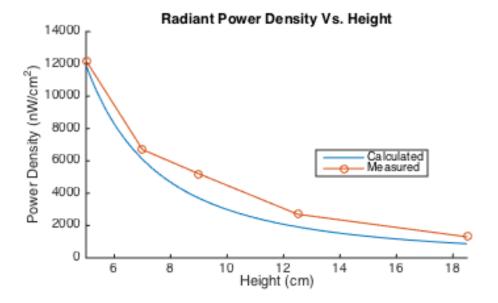

| 4.4  | Comparison between measured and calculated radiant power density across different height.                                | 89  |

| 4.5  | Off-chip readout path measurement setup                                                                                  | 90  |

| 4.6  | Noise power spectral density of AD8021. [48]                                                                             | 91  |

| 4.7  | On chip buffer linearity and gain measurement vs simulation results                                                      | 93  |

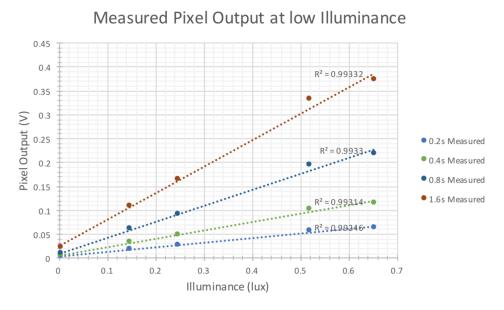

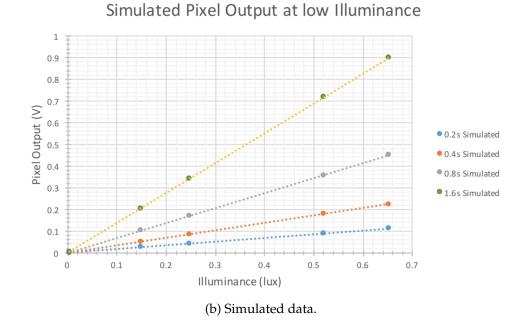

| 4.8  | Pixel output vs. low illuminance at various integration times with wave-<br>length of incident light peaking at 466 nm.  | 95  |

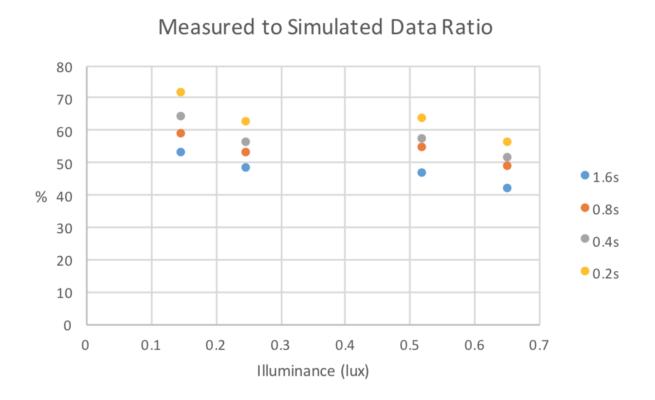

| 4.9  | Measured to simulated ratio.                                                                                             | 96  |

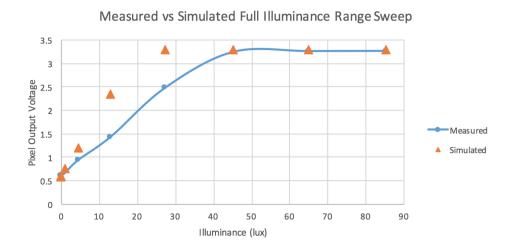

| 4.10 | Pixel output across wide illuminance range at 0.4s integration with wave-<br>length of incident light peaking at 550 nm. | 98  |

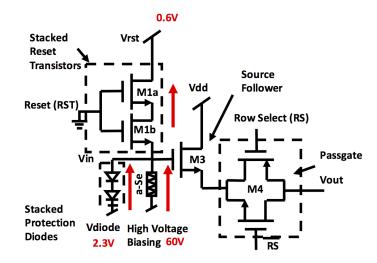

| 4.11 | Q1 pixel schematic in the integration phase with leakage current direc-<br>tions shown with arrows.                      | 99  |

| 4.12 | Averaged pixel output vs integration time                                                                                | 100 |

| 4.13 | Signal and SNR vs illuminance for various integration periods, with red line indicating target SNR.                      | 102 |

| 4.14 | Imager SNR vs T <sub>int</sub> in low-light conditions.                                                                  |     |

|      | Array noise measurements across integration time.                                                                        |     |

| 4.16 | Optical imaging setup.                                                                                                   | 105 |

| 4.17        | Imaging of line pair target at 0.1 lux                        |

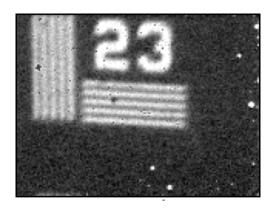

|-------------|---------------------------------------------------------------|

| 4.18        | Image target taken at 0.82 lux with 0.4 s of integration time |

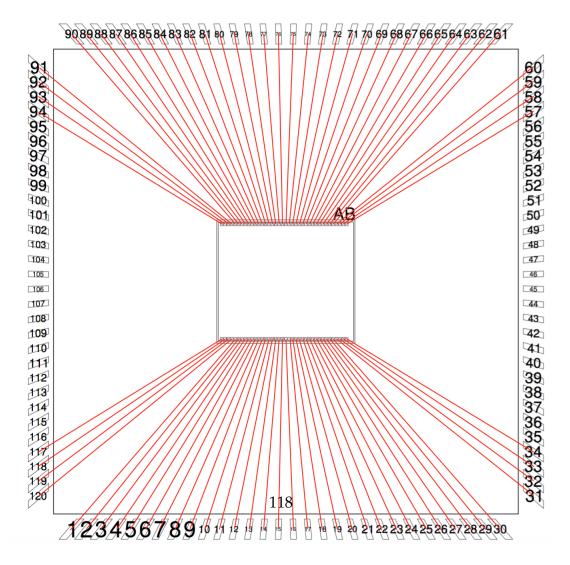

| A.1         | LL1 CMOS chip bonding diagram                                 |

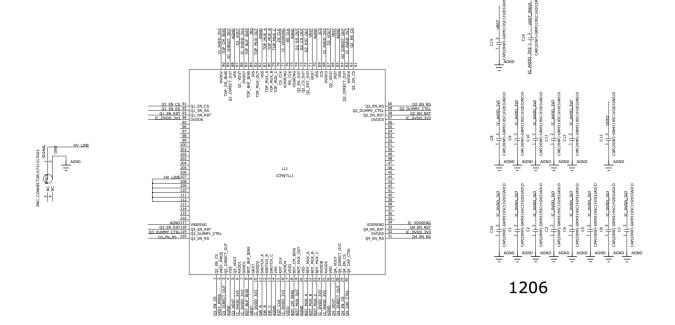

| <b>B.</b> 1 | PCB schematic of CMOS chip with decoupling capacitors         |

| B.2         | PCB schematic of analog biasing and signal buffers            |

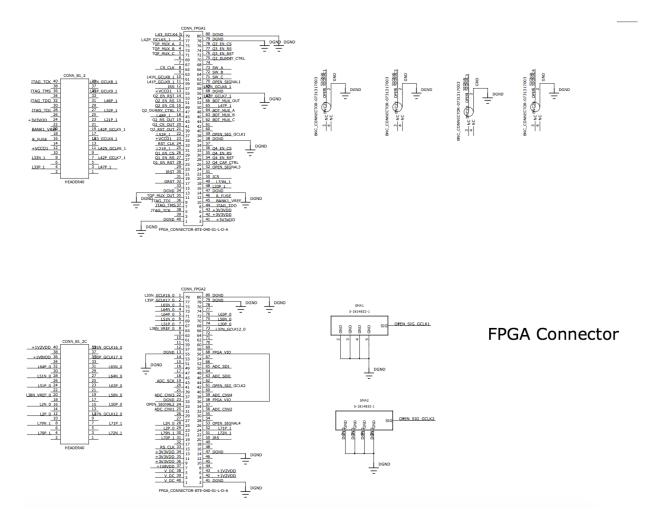

| <b>B.3</b>  | PCB schematic of Opal Kelly FPGA connectors                   |

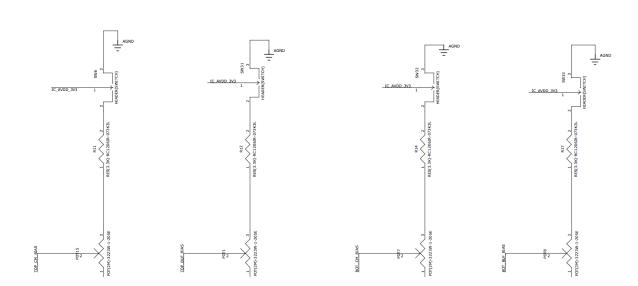

| <b>B.4</b>  | PCB schematic of CMOS current biasing circuits                |

| B.5         | PCB schematic of an ADC with pre-amp buffer                   |

| B.6         | PCB schematic of ADC power generation circuits                |

| B.7         | PCB schematic of CMOS power generation circuits               |

| <b>B.8</b>  | PCB schematic of PCB main power generation circuits           |

## Chapter 1

## Introduction

Modern digital-imaging technology has come a long way since Steven Sasson introduced the first digital camera at Kodak in 1975 [1]. Digital cameras have benefited greatly from Moore's law. Charge-coupled devices (CCDs) and complementary metaloxide semiconductors (CMOS) have been used to build smaller, more compact, and faster imagers. Still, however, few digital cameras can compete with the human visual system's performance under low-light conditions. This is chiefly because digital camera systems are affected by the noise generated in readout electronics that set practical limits on the lower detection boundary in low-light conditions. The few imagers that have exceptional low-light performance are expensive and usually require either a large form factor to house a cooling unit or a more sophisticated fabrication process to reduce the imager's electrical noise.

Improving the low-light imaging capability of cameras built with standard CMOS processes could improve many product systems, including low-cost, high-volume consumer electronics, such as smartphone cameras and computer vision systems. The low-light performance improvement can come from either the photosensor or the readout electronics.

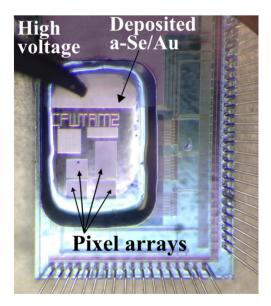

This thesis presents a new design for building low-light image sensors that combines amorphous selenium (a-Se) as the photoconductor material with a readout circuit built using a standard mixed-signal CMOS process. With unconventional vertical stacking architecture that greatly improves the imager fill factor, coupled with the a-Se low dark current, this low-light imager's performance could be comparable to the other specialized low-light imagers already mentioned. The Silicon Thin-film Advanced Research (STAR) group at the University of Waterloo has previously shown the X-ray-imaging potential of the a-Se/CMOS hybrid-imager structure with the AM2 imager, as Figure 1.1 shows [2]. This thesis explores the static low-light imaging capability of the same architecture with a newly designed CMOS chip by focusing on better noise performance and achieving higher SNR under low-light conditions.

Figure 1.1: AM2 imager with an amorphous selenium photosensor on a CMOS readout integrated circuit (ROIC).

## 1.1 Low-Light Imaging

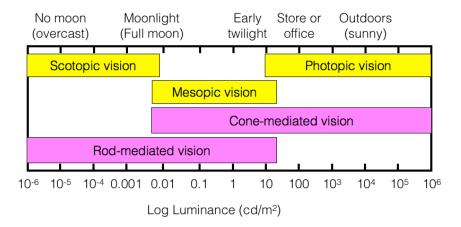

The human visual system contains two types of sensory cells: cones, which are responsible for detecting colors, and rods, which are sensitive to brightness. Together, they operate in 3 regions across the visible-light spectrum at different luminances (i.e., surface brightness), as Figure 1.2 shows [3]. The chart covers the luminance of common natural light sources people experience daily, from a no-moon sky to a sunny day. Luminance is the luminous flux per unit solid angle per unit projected source area in a given direction, with the units of cd (candela)/m<sup>2</sup>. Luminous intensity, a measure of light (with the unit of cd) leaving a surface, is independent of the distance between the light source and the observer. By definition, candela is the luminous intensity, in a given direction, of a source that emits monochromatic radiation of frequency  $540 \times 10^{12}$

Hz and that has a radiant intensity, in a given direction, of 1/683 Watts per steradian [44].

Photopic vision occurs under well-lit conditions in which both cones and rods are active but also in which cones are the dominating sensory cells and allow good color recognition and acuity. Mesopic vision occurs under dim conditions in which cones are less sensitive but rods work alongside them, enabling color detection. Scotopic vision occurs under dark conditions in which rods are the dominating sensory cells and color sensitivity drops but brightness awareness peaks.

Figure 1.2: Luminance table for the human visual system.

Since luminance is used to describe the brightness of a light-emitting surface, such as the sun, the moon, LEDs, or computer monitors. It cannot be used to characterize the amount of light an imager sees. Illuminance must be used to accurately describe the amount of light an imager sees. Illuminance takes the distance between the source and the observer, as well as the size of the observer, into account. Lux is the unit of illuminance, with the unit of lumen (lm)  $/m^2$ . Lumen is the SI unit of luminous flux, for which one lumen is defined as the luminous flux of light produced by a light source emitting one candela of luminous intensity over a solid angle of one steradian. Section 4.1.1 includes a detailed conversion between luminous intensity at a given distance and illuminance (lux). Table 1.1 [4] summarizes the common illuminance levels from natural light sources. Note that moonlight will typically provide between 0.05 and 0.267 lux of illumination [5]. This thesis will focus on imaging in the scotopic-vision region with the aim to build an imager that can produce recognizable images with illuminance of less than 0.05 lux, which is the lower boundary of moonlight illuminance, making the system moonlight-imaging capable.

|                                   | Lux         |

|-----------------------------------|-------------|

| Sun overhead                      | 130000      |

| Full daylight (not direct sun)    | 10000-25000 |

| Overcast day                      | 1000        |

| Very dark overcast day            | 100         |

| Twilight                          | 10          |

| Deep twilight                     | 1           |

| 1 candela at 1-meter distance     | 1           |

| Full moon overhead                | 0.267       |

| Total starlight + airglow         | 2.00E-03    |

| Total starlight only              | 2.00E-04    |

| Venus at brightest                | 1.40E-04    |

| Total starlight at overcast night | 1.00E-04    |

| Venus at brightest                | 1.40E-4     |

| Total starlight at overcast night | 1.00E-4     |

Table 1.1: Common illuminance conditions.

## 1.2 Digital-Imaging Technology Overview

A digital-imaging system consists of two major blocks: the photosensor, which is responsible for converting incoming optical photons into electron-hole pairs (charge), and the readout electronics, which processes the converted charge and facilitates digitization. This section will provide a brief overview of common architectures used for both components.

#### 1.2.1 Photosensors

The most common photosensors in consumer electronics are photodiodes formed with doped silicon-junction diodes. More specialized photosensing material can be deposited onto a CMOS-imager chip via post-processing for advanced applications, thus forming a hybrid imager. Amorphous selenium deposited on CMOS [2] is such a hybrid structure. With its low dark current, as compared to standard silicon photodiodes, a-Se can provide superior imaging performance under low-light conditions if readout electronics for both photosensors have similar noise performance. This section will discuss both types of photosensors.

Figure 1.3: A depletion region is formed when a PN junction is reverse biased.

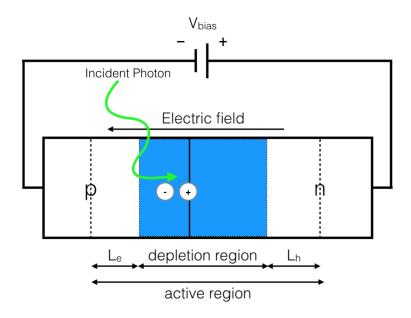

#### 1.2.1.1 Silicon Photodiodes

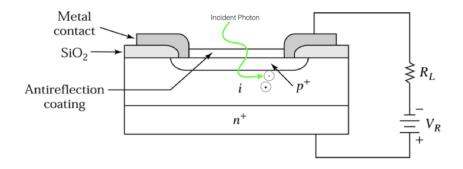

The most commonly used photosensors in the current consumer market are the p-n, pintrinsic-n (p-i-n), and pinned photodiodes. These photosensors share the same belowoperational principles: doping adjacent regions on a silicon wafer causes a pn junction to form. When the junction is reverse biased, a depletion region forms between the doped sections, preventing the flow of electrons, as Figure 1.3 shows [6]. A photon landing in the depletion region will generate electron-hole pairs. The generated electrons and holes will drift towards the oppositely doped regions because of the reversebiasing field and will be collected before they can recombine. However, the incoming light photons will only generate electron-hole pairs if they land in the depletion region. With current technology, typical biasing conditions will only create a depletion depth of 1 to 2  $\mu$ m, which is insufficient to absorb all incoming photons. Photons landing in the doped regions will immediately recombine and, therefore, cannot be collected. Hence, to increase the area for which a photon can strike and free electron-hole pairs, an intrinsic undoped layer must be added between the 2 doped sections, which is the origin of the p-i-n (pin) photodetectors, as Figure 1.4 shows [7].

Both p-n and p-i-n photodiodes suffer from high dark current and have difficulty

Figure 1.4: Planar diffused p-i-n photodiode.

transferring out all charges collected inside the photodiodes during each reset operation, which is the process of discharging collected charges from photodiodes and readying them to receive more charges. This incomplete charge transfer causes some charges from a previous sampling period to show in the current sample period, creating a laglike effect. The pinned photodiode, introduced to improve these properties, [8] is a photodiode with an extra-thin p-type implant placed on the other side of the n-type substrate and pinned to a fixed voltage. With this implant in place, two back-to-back diodes are formed when a sufficiently large voltage is applied across the diode. When the depletion region of the two diodes meet, all charges in the photodiode are completely removed, assuming the biasing voltage is high enough.

The dark current in silicon photodiodes is the photodiodes' reverse-biased leakage current. It arises from the mobile charge carriers in both p-type and n-type doped regions tunnelling through the depletion junction region. Therefore, by introducing an intrinsic layer between the two doped areas, p-i-n photodiodes will have lower dark current than traditional p-n photodiodes, but the dark current is still higher than that of a-Se.

#### 1.2.1.2 Amorphous Selenium Photoconductors

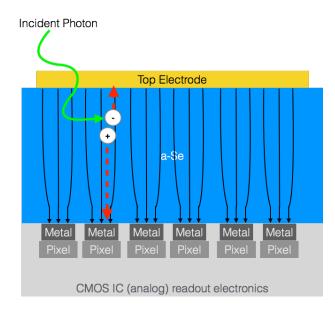

Figure 1.5 shows the operational principle of a-Se deposited on a CMOS pixel-array readout IC. When incoming photons strike, they are absorbed within a few tens of µms and will generate a cloud of electron-hole pairs. The cloud size depends on the incident photon energy. With the a-Se biased, the electrons and holes will, following the electrical field within the a-Se, travel to the biased top and bottom electrodes. The top electrode usually provides a positive biasing high voltage, and the bottom electrodes

Figure 1.5: a-Se vertically stacked on a CMOS-readout IC

are the exposed metal pads from individual pixels at a lower voltage potential. The metal opening in individual pixels creates a low resistance path to the integration capacitor that allows the photon-generated electrons to be collected at the high-voltage top electrode. The holes will then travel to the closest pixel metal pad and be stored in the integration capacitor. This process is called hole collection. When an incoming photon is absorbed into a-Se, a positive voltage response will result in the corresponding pixel below. Because of the potential difference between the top electrode and the pixel reset voltage, the electrical field inside the a-Se will bend towards each pixel opening, effectively collecting all charges generated inside the photosensor. Holes have higher mobility than electrons in a-Se; therefore, using hole collection will improve the lag performance.

The photosensor's dark current is an important parameter for low-light imaging. Dark current is the photosensor's leakage current under normal operational bias without exposure to any incoming signal. Lower dark current allows a photosensor to produce a recognizable signal from a weaker incoming source. With the silicon bandgap at 1.12 eV and a-Se at 2 eV [12], electrons in silicon photodiodes require less energy than in a-Se to jump from the valence band into the conduction band. With the same thermal energy present, silicon exhibits a higher leakage current, ranging from 1 to 10 nA/cm<sup>2</sup> [9], while a-Se detectors exhibit leakage current less than 0.02 nA/cm<sup>2</sup> [13]. Low dark

current also allows the imager to collect incidental signals (i.e., integrate) for a longer period, thereby collecting a stronger signal (assuming constant incidental flux).

#### **1.2.2 CMOS Readout Electronics**

This section will describe some common pixel-electronics designs, as well as the designed imager's basic architecture.

#### 1.2.2.1 Imaging Technology Overview

Low-light performance of standard CMOS imagers has always suffered in comparison to other imaging sensors, including CCD and vacuum-tube imagers [16]. In an ideal imager, the minimum detectible signal should be limited by the photon shot noise generated from the light source. However, the low-light performance in current CMOS imagers featuring p-n, p-i-n, and pinned photodiodes is fundamentally limited by the electronic noise collected during integration.

Alternative low-light imaging systems, such as the high-gain avalanche rushing amorphous photoconductor (HARP), commonly use a-Se as photosensing material. To minimize electronic readout noise, vacuum tubes pick up the signal converted within a-Se [16]. While these imagers perform superbly in the dark, the cost to build and operate them is extremely high.

#### 1.2.2.2 Silicon-Photosensor CMOS Imager vs Hybrid CMOS Imagers

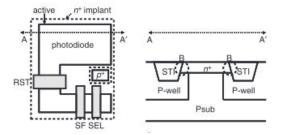

Figure 1.6 shows a standard CMOS-imager layout that incorporates a silicon photodiode and that includes a 3-transistor (3-T) active pixel sensor (APS). Later sections will explain the 3-T APS operation.

Although this APS design is compact, it suffers from a few imperfections. Because the photosensors are coplanar to the readout circuitry, part of the pixel must be dedicated to the readout transistors, meaning the pixel's fill factor is limited. Fill factor is the area of the photosensor divided by the total pixel area. As Figure 1.6 shows, a typical layout with silicon photodiodes can only utilize about 60% of the pixel area. Moreover, since the photodiode sits in the substrate, the routing above the photosensitive area must be minimal, making it difficult to route traces within the pixel array. Since light often needs to penetrate a few nanometers of metals in the routing layer above

Figure 1.6: 3T pixel layout [17]

the pixel area, the optical tunnels can create a host of undesired optical effects for low-fnumber optical systems, including light scattering, vignetting, crosstalk, and diffraction problems [19]. Micro-lenses can be used to guide light onto the photodiodes, but they also add uncertainty and complication during fabrication and operation, including nonuniformity and reflection.

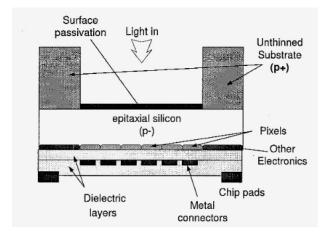

The fill factor is especially important for low-light imaging where the signal is small. This is because the fill factor is directly proportional to the percentage of incoming signals collected. Backside illumination is commonly used to overcome the fill-factor issue. During processing, the silicon wafer is flipped and thinned, allowing light to strike the photodiodes from the backside and thereby prevent signal loss to the routing-metal layers, as Figure 1.7 shows. This process, however, is expensive, and extensive tuning is needed to reduce non-uniformity in the array. Moreover, because of the extra processing steps, the wafer yield also suffers, resulting in a high manufacturing cost of BSI devices.

On the other hand, as Figure 1.5 shows, the performance of a hybrid imager, for which the CMOS-readout electronics are coated with a photosensor (a-Se) for light detection, could be improved under certain situations. This design can improve the imager's low-light performance, as compared to that of imagers using silicon photodiodes, because of the low dark current of a-Se. Moreover, since a-Se has served as a photosensor since the introduction of Xerox photocopiers, its optical properties have been well studied and characterized [20]. Lastly, by using the hybrid-imager structure, the read-out electronics and the photodiodes no longer need to be coplanar, which allows IC designers to shrink the pixel pitch or use the space to implement various performance-enhancing circuit designs.

Figure 1.7: Backside illumination cross section schematic [21]

### **1.3 Performance Metrics**

To characterize imager performance, this section will discuss a few characterization parameters commonly used for imagers. These parameters can be used to evaluate both the photosensor and the readout electronics, as well as the imaging system's performance.

#### 1.3.1 Conversion Gain

For all APS circuitries, each positive or negative charge converted from an incoming photon will cause a positive or negative shift in voltage at the integration node once the charge is transferred and stored onto the integration capacitor. The voltage magnitude  $V_{charge}$ , induced by the collected charge, is given by

$$V_{charge} = \frac{Q}{C_{int}} \tag{1.1}$$

where Q is the number of electrons or holes (in Coulombs) collected at the integration node and  $C_{int}$  is the integration node capacitance.

The conversion gain of imagers targeting low-light conditions should be as high as possible because the readout electronics will sample voltage change caused by incoming photons.

#### 1.3.2 Noise

The readout electronics' noise sets the practical limit on the lower detection boundary, so the noise sources must be identified. The electronics noise can be divided into two categories: temporal noise and spatial fixed-pattern noise. Temporal noise is the variation in a constant signal when taken across multiple points in time. The common types of temporal noise in a 3-T pixel design include

- thermal noise on the integrating capacitor,

- dark current shot noise from some photosensors,

- leakage current shot noise from transistors, and

- flicker noise from in-pixel amplifiers.

Moreover, because of the nature of light, the incoming signal will also have associated shot noise. The signal shot noise will be small compared to electronics noise at low-light levels, but it will become the dominant noise source when the signal is higher.

Fixed-pattern noise is mainly attributed to process-induced variation across the imaging array, such as threshold voltage and source-follower gain offset, as well as columnto-column variation resultant from impedance mismatch. The following chapter will discuss each noise source in detail.

#### **1.3.3** Photon Transfer Curve

The photon transfer curve (PTC) can be used to extract a few key parameters from an imaging system by contrasting the signal and noise at the imager's output. The only noise introduced at the input is the shot noise associated with the incidental signal. Any further discrepancy must be added by the imaging system. The photon shot noise  $n_{shot}$  (discussed further in later sections) is given by

$$n_{shot} = \sqrt{N_{sig}} \tag{1.2}$$

where  $N_{sig}$  is the number of charges in the incident signal.

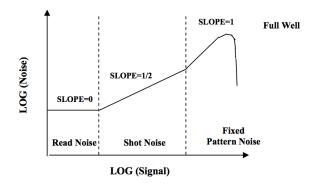

Figure 1.8 shows a typical PTC that can be broken down into 3 sections. The first plot section is when the slope is zero, indicating the imager's lower detection boundary.

Figure 1.8: Typical photon-transfer curve.

The temporal noise from the readout electronics and the subsequent analog-to-digital conversion circuitry is larger than the incoming signal, meaning signals in this region will be buried by the system noise.

The second section is when the slope is 1/2. Here, the dominating noise is the photon shot noise from the incoming signal. Given that light's shot noise can be modelled with Equation 1.2, when it is plotted on a log-log scale, it will show as a straight line with a slope of 1/2.

The last region can be further broken down into two parts: The first is when the pixel-gain non-uniformity and fixed-pattern noise dominate, and since this non-uniformity is linearly proportional to the incidental signal, the slope during this phase equals to unity. The second is when each pixel reaches its capacity and can, therefore, no longer hold additional charges. When this occurs, the charge will overflow to adjacent pixels, creating an averaging effect that reduces the fixed-pattern noise and photon shot noise. Normally, the fixed-pattern noise can be suppressed using gain and offset correction, therefore extending the shot-noise dominant range all the way to the imager's full-well capacity [25].

#### 1.3.4 Signal-to-Noise Ratio

Signal-to-noise ratio (SNR) is a chief metric for image-system characterization and provides the lowest detectable signal, as well as a figure of merit to define when an image is of acceptable quality. The *SNR* can be calculated by

Figure 1.9: Images with ranging SNR.

$$SNR = 10 \times \log_{10} \left( \frac{P_{sig}}{P_{noise}} \right)$$

(1.3)

where  $P_{sig}$  is the power of the incoming signal, and  $P_{noise}$  is the image system's noise power at the given signal level. The minimum detectable signal is defined where SNR = 0 dB, while a SNR of 13.97 dB will produce recognizable images based on the Rose criterion [10]. Moreover, based on the ISO 12232 standard [11], a SNR of 20 dB will generate clean and acceptable images, while an SNR of 32 dB will generate images with excellent quality. Figure 1.9 shows images with SNRs ranging from 0.4 dB to 27 dB.

In a digital imager, two major noise sources are the shot noise resultant from undesired leakage current from the photosensor and readout electronics. Since shot noise is the square root of incidental signal, the shot-noise-dominated SNR will grow in a square-root manner with an increasing integration period. Given the leakage shot noises are the dominant noise sources in a digital imager, a longer integration period could produce a higher SNR. Imagers using silicon photodiodes will suffer from the continuous leakage current through both the photosensor and the readout electronics, preventing the CMOS imagers from achieving long integration periods. The shot noise from the dark current of the photosensor and the leakage current of the readout electronics will set a practical lower bound on SNR for a 3-T APS design.

#### 1.3.5 Full-Well Capacity and Dynamic Range

An imager's dynamic range (DR) represents the range of incidental signal that the imager can observe before the pixel capacity is saturated. It can be calculated by

$$DR = 20\log_{10}\left(\frac{N_{sat}}{n_{dark}}\right) \tag{1.4}$$

where  $N_{sat}$  is the signal-charge saturation level in number of electrons (also referred to as the pixel full-well capacity) and  $n_{dark}$  is the pixel's noise level when no signal is present, usually expressed in root-mean-square (rms) number of electrons [23]. Since most optical-imaging scenarios contain both bright and dark information in a single frame, a high DR is crucial when designing an imager.

The number of electrons  $N_{sat}$  that an imager can hold can be calculated using

$$N_{sat} = C_{int} \times \frac{V_{max} - V_{min}}{q} \tag{1.5}$$

where  $C_{int}$  is the integration node's capacitance;  $V_{max}$  and  $V_{min}$  are the maximum and minimum voltages that the readout circuit could extract, respectively, from the pixel; and q is an electron's charge in Coulombs.

#### **1.3.6 Quantum Efficiency**

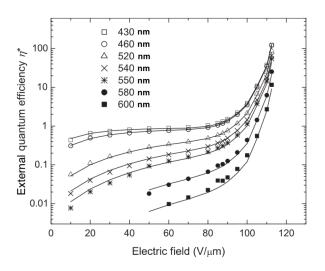

Quantum efficiency characterizes a photosensor's ability to convert incidental photons into electron-hole pairs and is usually expressed as a function of wavelength. An external quantum efficiency (EQE) is the quantum efficiency of an imaging system, accounting for that system's sensory components, including reflection by the top electrode, fill factor, and lenses. Figure 1.10 measures and characterizes the EQEs of a-Se at several wavelengths across various electrical fields, obtained with a HARP camera that employs vacuum pickup tubes as the readout technique, thus greatly limiting the readout electron noise [26]. Note that the EQE increases considerably across the applied electrical fields, possibly because of a stronger electrical field that reduced the energy gap between the valance band and the conduction band in a-Se. The plot also shows that a-Se will have an EQE close to 1 at shorter wavelengths, even with a relatively low bias, which is similar to a p-n photodiode.

When a strong field is present, usually above 80 V/ $\mu$ m, a-Se could enter avalanche mode. In avalanche mode, the initial electron-hole pairs, separated by the energy of incidental photons, will collide with adjacent electron-hole pairs. With a high field present, all the electron-hole pairs in a-Se are already partially energized, and the initial electron-hole pair will set off a chain reaction and create many more electron-hole pairs than normal. Each incoming photon can, therefore, result in an EQE much greater than 1. This is the low-light camera HARP's operational principle [16].

Figure 1.10: Measured a-Se EQE across various electrical fields.

### 1.4 Motivation and Objective

Most CMOS imagers require specially modified fabrication processes to lower the leakage currents already previously. This process modification, however, leads to high development and manufacture costs. Incorporating analog blocks onto a modified process while maintaining their performance is difficult. Designing a low-light imager that can be made using a standard mixed-signal CMOS process can potentially reduce the cost of such imagers and allow multiple blocks of analog and digital circuitries to be implemented on the same die, achieving a camera-on-chip system.

A-Se has been widely used as a photosensor in commercial products, including photocopiers [20] and high-performance cameras [16]. The STAR group at the University of Waterloo developed the a-Se-deposition process, enabling this work to build a hybrid imager by combining a-Se with a custom-designed CMOS imager. This research project aims to design a CMOS imager that is compatible with the a-Se deposition process and that can take advantage of the low dark current of a-Se photosensor to achieve low-light imaging through long integration.

### **1.5** Thesis Organization

Chapter 2 will cover more background information necessary to understand this project's design choices. It will focus on the CMOS-readout technologies. It will discuss different circuit structures, common noise sources, and the significance of each in the proposed system. It will then cover a study conducted to evaluate the low-light imaging capability of the proposed hybrid structure using simulated parameters, which are also used to extract the imager design's key-performance specifications.

Chapter 3 will cover the imager's circuit design and simulation results, focusing on the design and modifications made in each quadrant from the standard 3-T voltagemode APS, as well as other on-chip components, including the analog buffer and the bond pads. This chapter also describes the external software and hardware built to control the imager.

Chapter 4 will cover the electrical and optical experiment setups and the imaging system results. The results will be compared to the design targets and simulation results, with comments and discussions on the discrepancies between them.

Chapter 5 will discuss the conclusions drawn from the experiments and compares this work with a few other recent works that target low-light imaging. It will also discuss future works that could improve the imager's performance.

## **Chapter 2**

## **Background and Feasibility Study**

This chapter will cover necessary background information and the feasibility of achieving low-light imaging using the hybrid image structure. Topics discussed include common pixel structures, noise sources, and a performance-simulation study based on estimated imaging conditions. The simulation will explore the feasibility of designing an a-Se-CMOS-hybrid imager that can achieve the desired performance under low-light conditions.

## 2.1 CMOS Pixel Architecture

All CMOS pixel architectures can be split into 2 categories: passive and active pixel sensors (PPSs and APSs). This section will cover both designs, discussing, in detail, the advantages and disadvantages of each.

#### 2.1.1 Passive Pixel Sensors

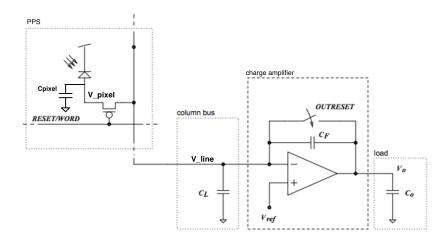

Figure 2.1 shows the schematic of a typical PPS with its readout circuit. Each PPS contains a photosensor (like the photodiode shown in Figure 2.1). Using the single transistor as an on-off switch, it will allow the charge integrated on the pixel capacitor  $C_{pixel}$ to be transferred to a column capacitor  $C_L$ . The charge amplifier will then sample the integrated signal and pass it down the readout path for digitization.

Figure 2.1: PPS with charge amplifier readout circuit [29].

The PPS's main advantage is its compactness, due to its simplicity. PPS can be used to implement an array with a high-fill factor and high resolution. However, it lacks performance in SNR because of its large-column capacitor-incurred kTC noise which cannot be kept small in a reasonably-sized imaging array. Moreover, the charge-sharing mechanism used between the pixel  $V_{pixel}$  and the column capacitor  $V_{line}$  in steady state is governed by

$$V_{line} = \frac{C_{pixel}}{C_{pixel} + C_L} \times V_{pixel}$$

(2.1)

where  $C_{pixel}$  is the capacitance of the photosensor and the integration capacitor in each pixel, and  $C_L$  is the column line capacitance. The column capacitance needs to be kept small small, as compared to the pixel capacitance, for an efficient readout. Therefore, PPS also lacks scalability. At the same time, the charge-sharing process's duration follows the column capacitor's RC-time constant and the pixel's output resistance, which limits the design's readout speed.

#### 2.1.2 Active Pixel Sensors

The key difference between the PPS and APS design is the use of an amplifier inside each pixel. This section will discuss two common APS designs.

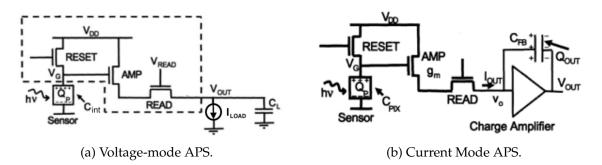

#### 2.1.2.1 Three Transistor (3-T) APS

APSs can be implemented with at least 3 transistors. Figure 2.2 shows the voltage-mode APS and the current-mode APS [22]. In both designs, the first transistor is a reset device that sets the integration node's voltage to a user-defined potential that will ready the pixel to integrate more incoming charges. The second device is an amplifier (AMP) MOSFET acting as either a source follower that buffers the integrated voltage in voltage mode or a transconductance amplifier that converts integrated charge into a current in current mode. The last transistor is a row-select read (READ) device that connects the pixel to a column bus. Later sections will explain the array structure and timing.

Figure 2.2: Schematic of voltage and current mode APS.

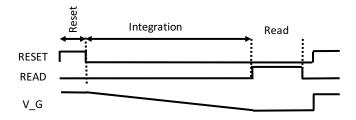

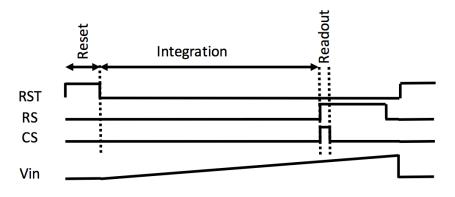

During normal mode of operation, both 3-T APSs will operate in 3 modes (as shown in the Figure 2.3 timing diagram):

- 1. Reset: The reset transistor is turned on, allowing the integration node to be reset to  $V_{DD}$ , assuming the pixel is performing electron collection.

- 2. Integration: The reset transistor is turned off, and the charge generated within the photosensor will be collected at the integration node.

- 3. Readout: Once the pixel has integrated for a user-defined period, the READ transistor will turn on, connecting the AMP device's source to a current load in voltagemode or a charge amplifier in current-mode.

Comparison of the two operational modes shows voltage mode has a clear speed advantage when implemented in a large array. Since current-mode APS requires the

Figure 2.3: Timing diagram of 3T voltage-mode APS.

AMP device to be biased in the linear region, the current-mode AMP will carry a smaller current for the same-sized AMP in voltage mode. In a large imager array, the columnbus capacitance will be large as well, meaning the voltage-mode APS will be able to charge the column capacitance faster than the current-mode APS and, thus, operate at a higher speed.

The APS design boasts another advantage, as compared to PPS: by isolating the pixel capacitance from the column line through an active device, the charge collected during integration does not need to be shared with the column capacitance. This means that the readout speed and the scalability can be greatly increased, and the pixel read operation becomes non-destructive. This importantly allows the collected data to be read multiple times as needed, enabling more advanced and sophisticated sampling methods, such as the correlated double-sampling technique. The 3-T design, however, often suffers from image lag, an effect caused by incomplete reset of the photodiode between adjacent integration periods, and thermal noise. Hence, the introduced 4-transistor (4-T) design minimizes noise and is commonly used with the pinned photodiode to eliminate lag.

#### 2.1.2.2 Four Transistor (4-T) APS

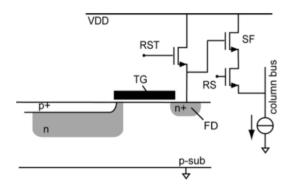

The 4-T APS design aims to remove most electrical noises produced in a 3-T design by introducing a transfer gate (TG) between the photodiode and the integration node, as Figure 2.4 shows. By adding the TG device, the 4-T design enables the correlated double-sampling technique (CDS), which can remove most reset thermal noise caused by each reset operation. Moreover, the extremely short time between the 2 samples, usually on the order of a few µs, significantly reduces the leakage-current shot noise's impact from other devices. An a-Se photosensor, however, operates differently from a typical silicon photodiode because the a-Se is unable to provide a large capacitance to hold the integrated charge. The imager must rely on an explicit capacitor inside

Figure 2.4: Schematic of a 4-T pinned APS [23]

the pixel, which would increase the pixel pitch's minimum size. Moreover, for CDS to occur, the time between the 2 samples must be sufficiently short so that the noise in both samples can be correlated. This timing cannot be achieved with the previous design and is difficult to achieve with the digital control circuitry considered for this design [2].

The other advantage of a 4-T design is the high conversion gain it provides. A floating diffusion (FD), as Figure 2.4 shows, can be made small. Hence, when the TG gate turns on, the charge-sharing action between the large photodiode capacitance and the FD results in a high conversion gain. A similar design can be created with a 3-T-a-Se hybrid pixel, since a-Se has a much lower capacitance than a photodiode.

### 2.2 Noise

As the previous chapter mentions, the low-light performance of CMOS imagers is fundamentally limited by noise in the readout system. In an ideal noise-free imager, the shot noise from the incoming light should be the dominant noise source. Improving the lower boundary of detection in an imaging system can be achieved by improving SNR at lower input levels. This can be done through a few methods, including by increasing the signal conversion gain and decreasing the readout electronic noise. In the case of static imaging, for which the frame rate is not a major concern, an extended integration period can improve SNR when the signal is low. The following section will discuss the mechanism and sources of common noise in imagers.

#### 2.2.1 Temporal Noise

Temporal noise is the variation and uncertainty of a constant signal when sampled at different times. It is a limiting factor of CMOS-imager performance and is contributed to by both photosensors and readout electronics. This section discusses the major temporal noise sources and their mechanisms.

#### 2.2.1.1 Photon Shot Noise

Photon shot noise is the fundamental noise generated by the light source. Assuming the light source's flux is perfectly uniform and constant, the incoming photons' arrival follows the Poisson distribution. This distribution's standard variation is simply the square root of the incoming photons, as Equation 1.2 shows.

#### 2.2.1.2 Dark Current Shot Noise (DCSN)

The same principle of photon shot noise also applies to the pixel's dark current and leakage current. The leakage current in a 3-T design comes from both the reset device operating in the subthreshold region during integration and the protection diodes that prevent the source follower's gate from over charging. The photosensor also produces dark current, which in some cases can produce shot noise. The dark-current shot noise  $n_{DCSN}$  in electrons rms is given by

$$n_{DCSN} = \sqrt{\frac{\frac{I_{sLeak} + I_{eLeak}}{q}}{FrameRate}}$$

(2.2)

where q is the charge of a single electron (1.602 x 10<sup>-19</sup> C),  $I_{sLeak}$  is the photonsensor's leakage,  $I_{eLeak}$  is the CMOS electronics' leakage current, and frame rate is the integration time's inverse, defined in frames per second (fps).

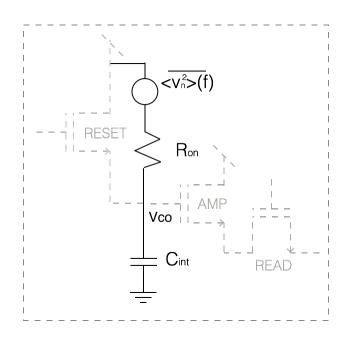

#### 2.2.1.3 Thermal Noise

In conventional resistive conductors, electrons will have randomness in their motion resultant from the ambient environment's thermal energy. In an APS pixel design, the reset transistor, which can be modelled as a resistor during reset, is responsible for setting the voltage on the integration capacitor. At the end of each integration, the number

Figure 2.5: Thermal noise schematic for reset operation in 3-T pixel.

of electrons stored on the integration capacitor could vary based on the capacitor's size and the ambient temperature. Figure 2.5 shows a simple schematic that represents the reset operation. The thermal noise, here, is modelled as a voltage source with the noisevoltage-power spectral density  $V_n^2$  in series with the reset transistor resistance  $R_{ON}$ .

The noise voltage power spectral density  $V_n^2(f)$  is defined by

$$V_n^2(f) = 4kTR_{ON} \tag{2.3}$$

where k is Boltzmann's constant and  $R_{ON}$  is the on resistance of the reset transistor in the linear region. The resistor's impedance and the capacitor form a voltage-divider network; therefore, the noise voltage  $V_{co}$  across the integration capacitor represents the noise seen by the pixel at the integration node.

To apply the transfer function to the noise power, the transfer function's magnitude square  $|H(f)|^2$  must be used. With the noise voltage across the capacitor given by

$$V_{c_o}^2(f) = V_n^2 \times |H(f)|^2 = \frac{1}{1 + 4\pi^2 R_{ON}^2 C_{int}^2 f^2} \times 4kTR_{ON}$$

(2.4)

the average noise power is given by

$$V_{c_o}^2 = \frac{kT}{C_{int}} \tag{2.5}$$

Notably, the result is not dependent on the resistance. Equation 2.6 shows the thermal noise  $n_e^-$  in terms of electrons rms

$$n_e^- = \frac{\sqrt{kTC_{int}}}{q} \tag{2.6}$$

As the equation shows, a smaller capacitor and a lower operating temperature will reduce thermal noise. Many existing low-light, high-performance imaging systems are often cooled to reduce thermal noise. However, since a-Se can delaminate at low temperatures, this method is not suitable for the proposed hybrid structure. As discussed and as Equation 1.1 states, an imager's conversion gain is inverse proportional to the integration capacitance. A smaller capacitor will, therefore, increase the amplification of incoming photons while the thermal noise increases by  $\sqrt{C_{int}}$ . Hence, in a thermalnoise-dominant system, the SNR will increase proportionally with  $\sqrt{C_{int}}$ .

#### 2.2.1.4 Flicker Noise

Two theories used to explain flicker noise are McWhorter's theory and Hooge's hypothesis. In McWhorter's theory, flicker noise is caused by the trapping and detrapping of charges in the oxide traps near the Si-O<sub>2</sub> interface [31] and is inversely proportional to  $C_{ox}^2$  (gate-oxide capacitance). In the bulk mobility fluctuation theory, based on Hooge's hypothesis, flicker noise is inversely proportional to  $C_{ox}$ . A unified model for flicker noise PSD  $V_{n_o}^2(f)$  was presented previously [32], but because of the model's complexity, the following simplified version, is often used [33]:

$$V_{n_o}^2(f) = \frac{K}{C_{OX}WL} \times \frac{1}{f}$$

(2.7)

where W and L are the width and length of the transistor, and K is a process-dependent technology parameter usually extracted from wafer measurements.

Given that flicker noise's upper and lower frequency boundaries are set by component characteristics inside the system, Equation 2.8 can be used to calculate the total flicker noise  $V_{n_o}^2$  in the system:

$$V_{n_o}^2 = \frac{K}{C_{OX}WL} \times \int_{f_{low}}^{f_{high}} \frac{1}{f} df = \frac{K}{C_{OX}WL} \times \ln\left(\frac{f_{high}}{f_{low}}\right)$$

(2.8)

$f_{low}$  represents the equivalent frequency of longest continuous operation and  $f_{high}$  is the device's upper cut-off frequency, usually defined by a low-pass filter on the readout path.

#### 2.2.2 Spatial Noise

Spatial noise is the variation across the imaging array at one time and will be discussed in this section.

#### 2.2.2.1 Under Dark Condition

When no signal is reaching the imaging array, the main variation across each pixel is caused by the device mismatch and fabrication-process imperfection. On the pixel level, the difference between device sizes could cause a mismatch in gate-source voltage, especially when all pixels are exposed to the same biasing current during readout. The difference in oxide thickness could affect the source follower's threshold voltage. The inconsistency in doping and temperature across the wafer could also affect the devices' leakage current. On the array level, since each pixel column shares a common readout-selection circuitry, the mismatch between the devices from column to column will generate a different output across the array. However, since the aforementioned variations have no temporal dependency, they are referred to as fixed-pattern noise.

#### 2.2.2.2 Under Illumination

When the imaging array is exposed to a light source, each pixel could respond differently even if the incoming signal is perfectly uniform across the entire array. Since the charge is converted into voltage and then buffered through the AMP device for readout, as Figure 2.2 shows, the conversion gain will differ across the array. Moreover, since the buffered signal through the AMP device is a function of the transconductance  $g_m$  in both the voltage and current modes, the difference in  $g_m$  will cause each pixel's gain to vary. Fortunately, digital processing can largely suppress fixed-pattern noise. A gain table can be created by exposing the imager to a known uniform flux, and an offset table can be obtained by taking an image in complete darkness then subtracting the dark frame from the actual image output.

### 2.3 Feasibility Study

Supported by previous noise discussion and key electrical measurements, including the subthreshold leakage current collected from previous works [2], we performed simulations to explore the performance limitations of an a-Se/CMOS low-light imaging system. This study will focus on the 3-T voltage-mode APS, which should provide better noise performance than a PPS design and faster readout than a current-mode APS.

The main electrical noise contributors in a 3-T voltage-mode APS are the reset operation's thermal noise, leakage-current shot noise from the reset transistor operating in subthreshold conduction during integration, and the source follower's flicker noise. An imager's SNR is calculated with different control parameters, including pixel capacitance, pixel pitch, and across low-light luminance levels.

An important advantage of using a hybrid-imager structure is that the pixel pitch is not limited by the photodiode in each pixel. Instead, various performance-enhancing circuits can be implemented to achieve better image quality while enabling the possibility of a high-resolution imager to be built.

To determine whether a standard mixed-signal CMOS process and a typical 3-T design could provide the performance needed to take advantage of a-Se, we performed calculations and simulations to quantify and to help us understand the impact of the parameters that can be controlled throughout the design process. To show a low-lightcapable imaging system, we chose a target SNR of 20 dB at 0.01 lux, which is starlightlevel illuminance, for this study to create design margins.

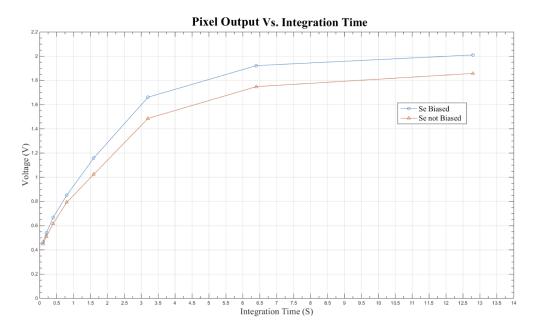

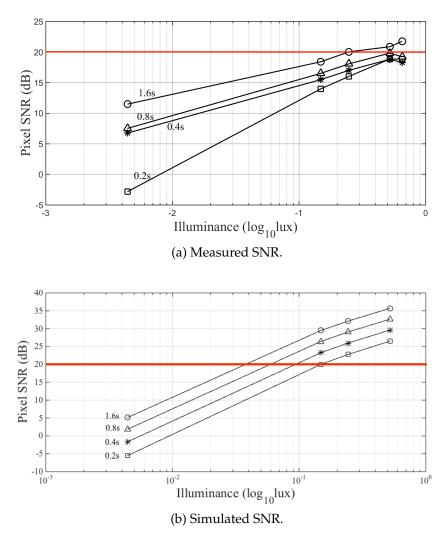

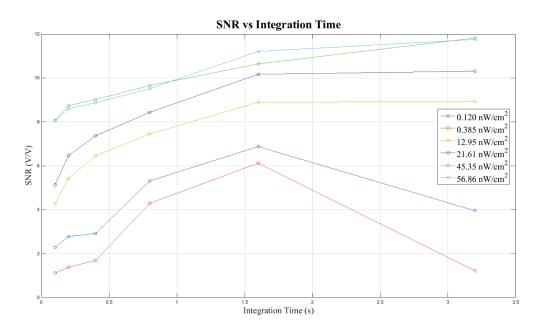

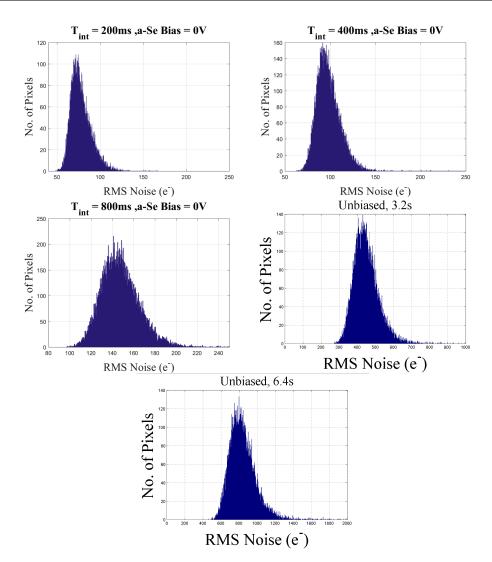

#### 2.3.1 Pixel Architecture Setup