# 0.42 THz Transmitter with Dielectric Resonator Array Antenna

by

#### Hamed Holisaz

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

**Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2019

©Hamed Holisaz 2019

### Examining Committee Membership

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner:        | Ehsan Afshari                             |  |  |

|---------------------------|-------------------------------------------|--|--|

|                           | Associate Professor                       |  |  |

|                           | Electrical Engineering & Computer Science |  |  |

|                           | University of Michigan                    |  |  |

| Supervisor:               | Safieddin Safavi-Naeini                   |  |  |

| Supervisor.               | Professor                                 |  |  |

|                           | Electrical and Computer Engineering       |  |  |

| Internal Members:         | Raafat Mansour                            |  |  |

|                           | Professor and Director                    |  |  |

|                           | Electrical and Computer Engineering       |  |  |

|                           | Vincent Gaudet                            |  |  |

|                           | Professor and Chair                       |  |  |

|                           | Electrical and Computer Engineering       |  |  |

|                           |                                           |  |  |

| Internal-External Member: | James Martin                              |  |  |

|                           | Associate Professor                       |  |  |

|                           | Physics and Astronomy                     |  |  |

## AUTHOR'S DECLARATION

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

## ABSTRACT

Off chip antennas do not occupy the expensive die area, as there is no limitation on their building material, and can be built in any size and shape to match the system requirements, which are all in contrast to on-chip antenna solutions. However, integration of off-chip antennas with Monolithic-Microwave-Integrated Chips (MMIC) and designing a low loss signal transmission from the signal source inside the MMIC to the antenna module is a major challenge and trade off. High resistivity silicon (HRS), is a low cost and extremely low loss material at sub-THz. It has become a prevailing material in fabrication of passive components for THz applications. This work makes use of HRS to build an off-chip Dielectric Resonator Antenna Array Module (DRAAM) to realize a highly efficient transmitter at 420 GHz. This work proposes novel techniques and solutions for design and integration of DRRAM with MMIC as the signal source. A proposed scalable 4×4 antenna structure aligns DRRAM on top of MMIC within 2 µm accuracy through an effortless assembly procedure. DRAAM shows 15.8 dB broadside gain and 0.85 efficiency.

DRAs in the DRAAM are differentially excited through aperture coupling. Differential excitation not only inherently provides a mechanism to deliver more power to the antenna, it also removes the additional loss of extra balluns when outputs are differential inside MMIC. In addition, this work proposes a technique to double the radiation power from each DRA. Same radiating mode at 0.42 THz inside every DRA is excited through two separate differential sources. This approach provides an almost loss-less power combining mechanism inside DRA. Two 140 GHz oscillators followed by triplers drive each DRA in the demonstrated 4×4 antenna array. Each oscillator generates 7.2 dBm output power at 140 GHz with -83 dBc/Hz phase noise at 100 KHz and consumes 25 mW of power. An oscillator is followed by a tripler that generates -8 dBm output power at 420 GHz. Oscillator and tripler circuits use a smart layer stack up arrangement for their passive elements where the top metal layer of the die is grounded to comply with the planned integration arrangement. This work shows a novel circuit topology for exciting the antenna element which creates the feed element part of the tuned load for the tripler circuit, therefore eliminates the loss of the transition component, and maximizes the output power delivered to the antenna. The final structure is composed of 32 injection locked oscillators and drives a 4×4 DRAAM achieves 22.8 dBm EIRP.

### ACKNOWLEDGEMENT

I would like to express my most profound gratitude to my supervisor, Professor Ali Safavi Naeini for giving me an opportunity to work in CIARS as his Ph.D. student. He has always encouraged me to explore new ideas, gave me complete freedom to work on whichever topic I am interested in, and showed me the right direction to go whenever I needed his advice. I can never thank him enough for his trust in me and his unlimited support.

I would like to especially thank Dr. Aidin Taeb for his invaluable help in fabrication and tremendous assistance during the measurement in the lab. His support during my research was incredible.

I must thank Dr. Anita Fadavi. She was always available to help me in the cleanroom and to have a discussion when needed. Without her technical input and insight, a successful micro fabrication of the antenna in this work has never been possible.

I must thank Dr. Arash Tabibiazar for his mentorship not just in this research, but in all aspects of my life. He helped me to come to Canada, introduced me to Professor Safavi-Naeini's group, and always guided me to make the right decisions in my life. I can not thank him enough for all his support.

I would like to thank Dr. Gholamreza Rafi for providing me with such excellent help with the lab instruments and preparing the measurement setup.

I would like to thank Chris Schroeder for her valuable time editing all of my publications and this thesis. Her meticulousness and perfectionism have always added value to my work.

I also thank my thesis committee and jury president for their valuable time for reviews and discussions: Professor Raafat Mansour, Professor Vincent Gaudet, Professor Ehsan Afshari and Professor James Martin.

I am thankful to my colleagues in CIARS: Dr. Suren Gigoyan, Dr. Nazi Ranjkesh, and Milad Mazi Esfahani for their support during my research at UW.

| To the loving memory of my grandpa, Hossein Holisa                           |   |

|------------------------------------------------------------------------------|---|

| To my parents, my beautiful wife, and my two sweet angels Parmida and Atrees | C |

|                                                                              |   |

|                                                                              |   |

|                                                                              |   |

|                                                                              |   |

|                                                                              |   |

|                                                                              |   |

# TABLE OF CONTENTS

| List | <b>Tables</b>                                           | ix  |

|------|---------------------------------------------------------|-----|

| List | f Figures                                               | X   |

| List | f Abbreviations                                         | xiv |

| 1    | troduction to THz Source                                | 1   |

| 1.   | Integrated Antenna Array Systems and Transceivers       | 3   |

| 1.2  | Sub-THz Frequency Synthesizers                          | 5   |

| 1    | Packaging and Antenna Module                            | 7   |

| 2    | requency Synthesizer                                    | 9   |

| 2.   | Oscillation Close To fmax                               | 9   |

| 2.   | Feedback Buffer Oscillator (FBO)                        | 11  |

| 3    | jection Locking Network                                 | 15  |

| 3.   | Reference Signal Distribution Network                   | 15  |

| 3.   | Microstrip Transmission Line (MTL)                      | 16  |

| 3    | Differential Co-Planar Waveguide Grounded (CPWG)        | 19  |

| 3.   | Tapered T-junction                                      | 20  |

| 3.   | H-Tree                                                  | 23  |

| 4    | ielectric Resonator Antenna Array                       | 26  |

| 4.   | Theoretical Derivations and Modal Analysis of DR        | 27  |

| 4.   | DRA Slot Excitation.                                    | 28  |

| 4    | DR Modal Field Simulation                               | 30  |

| 4.   | DRA on PEC Plane with an Ideal Magnetic Slot Excitation | 31  |

| 4.   | DRA with an Attached 30 µm Silicon Slab                 | 34  |

| 4.   | DRA with Differential Excitation                        | 37  |

| 4.   | Power Combining inside DRA                              | 39  |

| 4.   | DRA Array Tray (DRAAT)                                  | 43  |

| 4.9  | DRA Excitation with Microstrip Line                     | 47  |

| 4.   | 4×4 DRAAT                                               | 51  |

| 4.   | The 4×4 DRA Array Module (DRAAM)                        | 52  |

| 5 42   | 0 GHz Source with 4×4 DRA Array Module (DRAAM) | 55 |

|--------|------------------------------------------------|----|

| 5.1    | Tripler Circuit                                | 55 |

| 5.2    | Injection Locking Circuit                      | 61 |

| 5.3    | Thirty-two Injection Locked Oscillator Network | 62 |

| 6 Fa   | abrication and Test                            | 65 |

| 6.1    | DRAAM Fabrication                              | 65 |

| 6.2    | Assembly Methodology                           | 70 |

| 6.3    | Radiation Pattern Measurement                  | 74 |

| 7 C    | onclusions and Future Work                     | 76 |

| 7.1    | Future Work                                    | 78 |

| Refere | ences                                          | 80 |

# List Of Tables

| Table 1.1. A short comparison between the recent work                               | 5    |

|-------------------------------------------------------------------------------------|------|

| Table 4.1. Electric and Magnetic fields for first radiating modes of cylindrical DR | . 30 |

# List Of Figures

| Fig. 1.1. (a) LTCC package arrangement [50]. (b) Organic packing [51]                            |

|--------------------------------------------------------------------------------------------------|

| Fig. 2.1. Capacitor-less cross coupled LC-oscillator                                             |

| Fig. 2.2. Sources of loss in a cross-coupled oscillator                                          |

| Fig. 2.3. Proposed buffer-feedback 140 GHz oscillator with transmission-line inductors           |

| Fig. 2.4. A T-model for TL                                                                       |

| Fig. 2.5. Layout of 140 GHz oscillator passives and interconnects including the output           |

| transformer                                                                                      |

| Fig. 2.6. Oscillator output tone. Peak power includes the harmonic mixer insertion loss and 13   |

| Fig. 2.7. Oscillator output noise at 100 KHz offset                                              |

| Fig. 2.8. Test chip of 140 GHz oscillator. Top metal layer (AP) is covering the underneath       |

| circuits                                                                                         |

| Fig. 3.1. H-tree differential clock distribution network                                         |

| Fig. 3.2. Design of MTL in TSMC65nm. AP layer is used as MTL ground                              |

| Fig. 3.3. Simulated Zo and $\alpha$ of the proposed MTL vs. line width at 140 GHz                |

| Fig. 3.4. Simulated field of MTL in TSMC65nm with 9 metal layers. AP is the ground layer 18      |

| Fig. 3.5. Proposed differential CPWG. E-field of propagation of a 140 GHz differential signal 19 |

| Fig. 3.6. Insertion loss (S21) and return loss (S11) of 1 mm of the differential CPWG            |

| Fig. 3.7. T-junction implementation with differential CPWG                                       |

| Fig. 3.8. Simulated S21 and S31 shows -1.15 dB insertion loss                                    |

| Fig. 3.9. Reflection coefficient (S11) of all ports which is better than -9.6 dB                 |

| Fig. 3.10. 1-to-8 differential signal distribution network using CPWG                            |

| Fig. 3.11. Phase of S21, S31,, S91                                                               |

| Fig. 3.12. Reflection coefficient at all ports                                                   |

| Fig. 3.13. Insertion loss for all the end port.                                                  |

| Fig. 3.14. Differential pairs show 174° phase difference at the end ports                        |

| Fig. 4.1. DRA Model for modal analysis                                                           |

| Fig. 4.2. Slot counling to the magnetic field inside DR A                                        |

| Fig. 4.3. (a) A cylindrical DR is excited through a slot on PEC. DR and PEC are placed on a                     |

|-----------------------------------------------------------------------------------------------------------------|

| TSMC65nm die model. (b) The ground slot on the PEC is excited with a lump port across the                       |

| slot                                                                                                            |

| Fig. 4.4. Sweep of $H_d$ and $R_d$ of DRA. $H_d$ at 100 $\mu m$ and $R_d$ at 80 $\mu m$ gives maximum radiation |

| efficiency                                                                                                      |

| Fig. 4.5. (a) The Electric field inside the DRA at optimum dimention, (b) Total gain and                        |

| radiation pattern                                                                                               |

| Fig. 4.6. Sweeps of $H_d$ and radius $R_d$ of DRA. $H_d$ = 100 $\mu m$ and $R_d$ = 80 $\mu m$ gives maximum     |

| radiation efficiency of 0.94 and total maximum gain of 5.2 dB at broadside                                      |

| Fig. 4.7. (a)(b) Electric field inside the DRA structure with an attached HRS carrier layer, 36                 |

| Fig. 4.8. (a) DRA with silicon slab excited through two ground slots, (b) Ports 1 and 2 are driven              |

| differentially with 180° phase shift                                                                            |

| Fig. 4.9. (a) Electric field inside the DRA structure when excited with two differentially driven               |

| ground slots, (b) Total gain and radiation pattern                                                              |

| Fig. 4.10. Radiation efficiency of the DRA with differential port excitation                                    |

| Fig. 4.11. (a) DR with silicon slab is excited through four ground slots. (b) Two sets of                       |

| differentially driven ports excite the slots and excite a single DRA                                            |

| Fig. 4.12. The Electric field inside the DRA with differential ports                                            |

| Fig. 4.13. (a) Radiation efficiency of a DRA excited by two differentially driven ports,                        |

| Fig. 4.14. Variation of input port reactance with Ws and Ls                                                     |

| Fig. 4.15. The 4×4 DRAs connected through a 30 $\mu m$ silicon slab (DRAAT). DRAAT is                           |

| positioned on top of a TSMC65nm die model. Each DRA is excited through an ideal port across                     |

| a single ground slot                                                                                            |

| Fig. 4.16. Total gain of 4×4 DRA module with loss-less excitation. (b) Total gain pattern of array              |

| at 420 GHz                                                                                                      |

| Fig. 4.17. Radiation efficiency of 4×4 DRAAT. DRAs are excited through a single loss-less                       |

| ground slot                                                                                                     |

| Fig. 4.18. Implementation of antenna feed line in TSMC65nm technology. AP layer is used as                      |

| MTL ground. DRA module is placed on top of active die. Ground slots in AP layer excite the                      |

| DRA 47                                                                                                          |

| Fig. 4.19. (a)(b) DRAAT is placed on top a TSMC65nm die. (c) One DRA is excited trough four       |

|---------------------------------------------------------------------------------------------------|

| ground slots. Two sets of differentially driven MTLs excite the four ground slots                 |

| Fig. 4.20. (a) Radiation efficiency, (b) total radiating gain pattern of one DRA excited with 49  |

| Fig. 4.21. Input reactance of each of the four MS ports                                           |

| Fig. 4.22. Input resistance of each of the four MS ports                                          |

| Fig. 4.23. E-field vectors around differentially driven MTLs for each DRA                         |

| Fig. 4.24. Total gain radiation pattern of the 4×4 DARAAT                                         |

| Fig. 4.25. DRA Array Module (DRAAM). DRAAM is a DRAAT plus the added alignment                    |

| features for assembling on top of an active die                                                   |

| Fig. 4.26. DRAAM total gain radiation pattern                                                     |

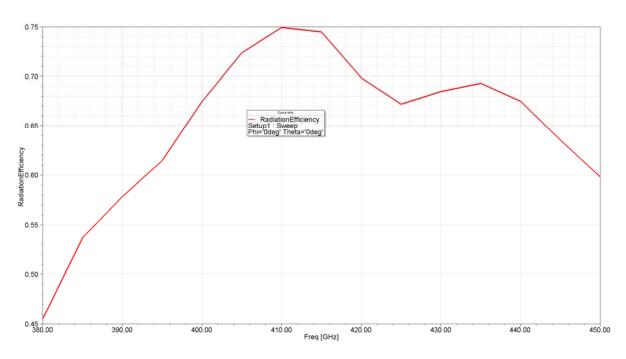

| Fig. 4.27. Radiation efficiency of DRAAM versus frequency                                         |

| Fig. 5.1. Input impedance of DRA ports is tunable by changing $W_s,L_s$ or $W_f$                  |

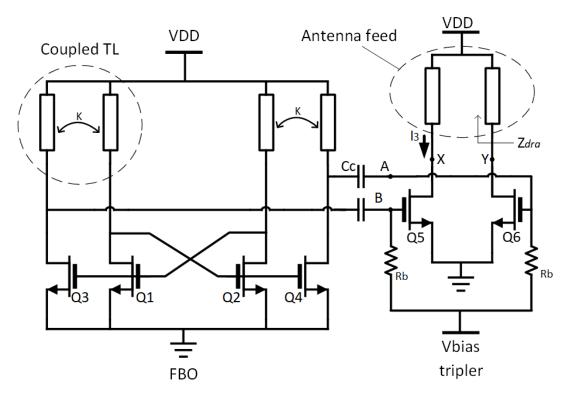

| Fig. 5.2. Tripler circuit follows the 140 GHz feedback oscillator                                 |

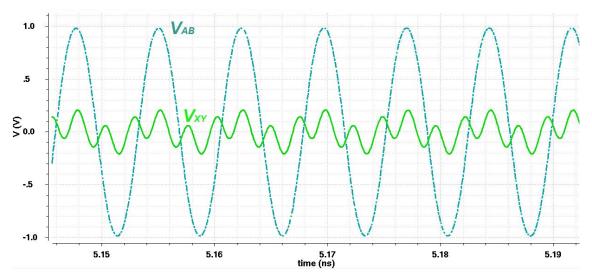

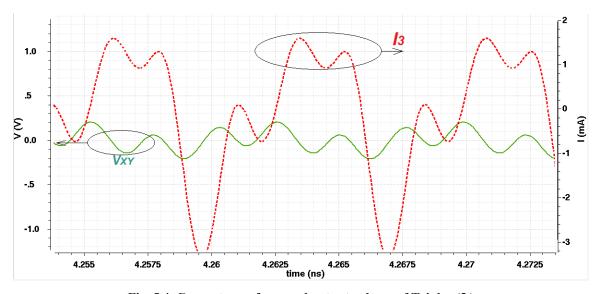

| Fig. 5.3. Input (V <sub>AB</sub> ) and output (V <sub>XY</sub> ) Voltage waveforms of tripler     |

| Fig. 5.4. Current wave of Tripler (I <sub>3</sub> )                                               |

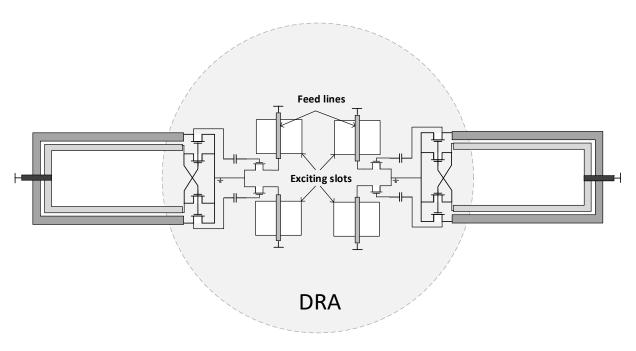

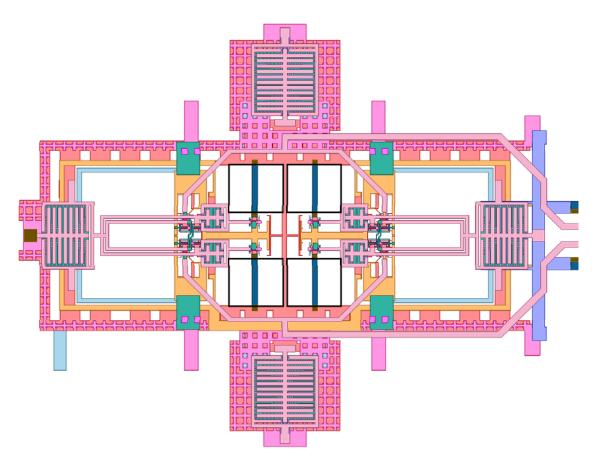

| Fig. 5.5. FBO-Cell is composed of two FBOs and two following triplers driving a single DRA 59     |

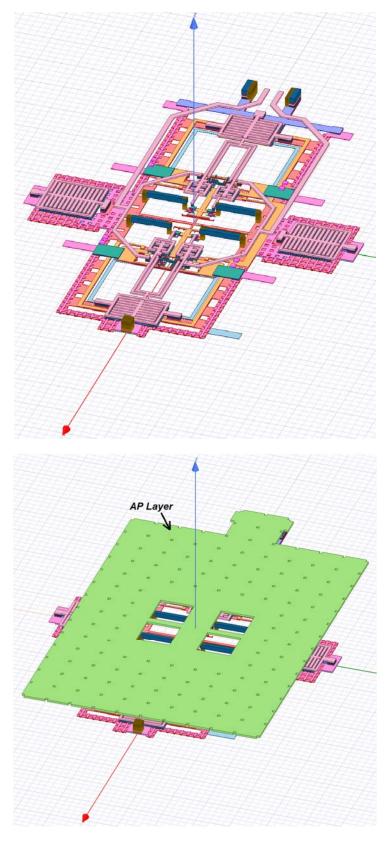

| Fig. 5.6. Layout of FBO-cell in TSMC65nm. Top AP (ground) layer that                              |

| Fig. 5.7. 3D view of FBO-cell layout                                                              |

| Fig. 5.8. Injection locking circuit added to FBO                                                  |

| Fig. 5.9. Block diagram of the transmitter chip where 32 injection locked oscillators driving the |

| 4×4 DRAAM                                                                                         |

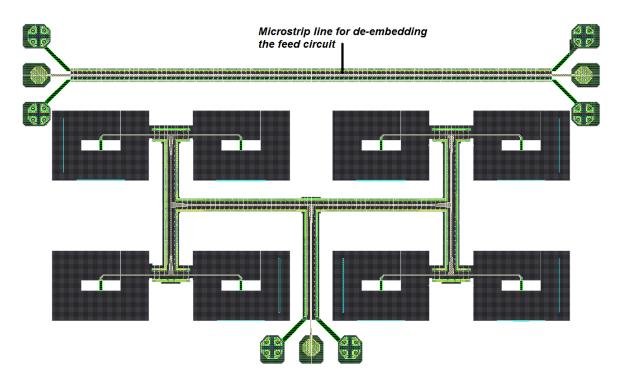

| Fig. 5.10. Layout of the transmitter chip                                                         |

| Fig. 5.11. Output waveforms of four injection locked oscillators                                  |

| Fig. 6.1. Result of lithography on top side of the wafer where the PR is patterned with           |

| Fig. 6.2. Silicon wafer is burned at the centre due to a long DRIE run                            |

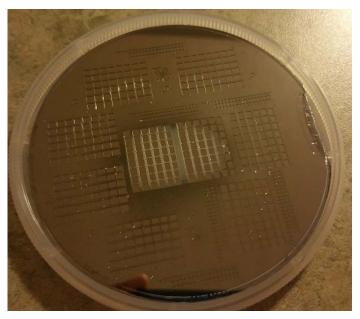

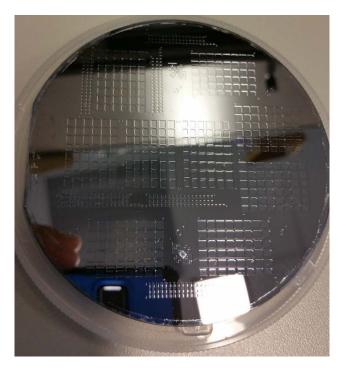

| Fig. 6.3. Si wafer after successfully finishing the DRIE on the bottom side                       |

| Fig. 6.4. laser cut leaves debris around the cut line                                             |

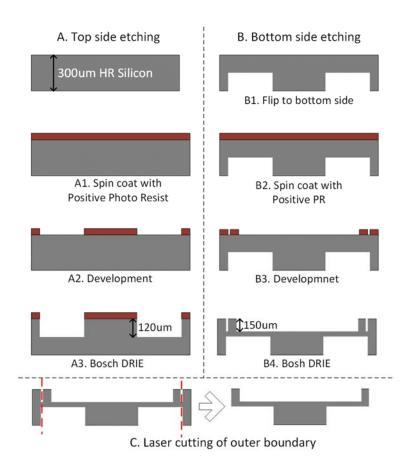

| Fig. 6.5. DRAAM fabrication process through two DRIE phases and one last phase of laser           |

| cutting                                                                                           |

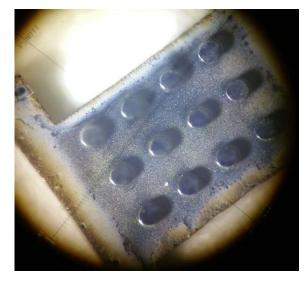

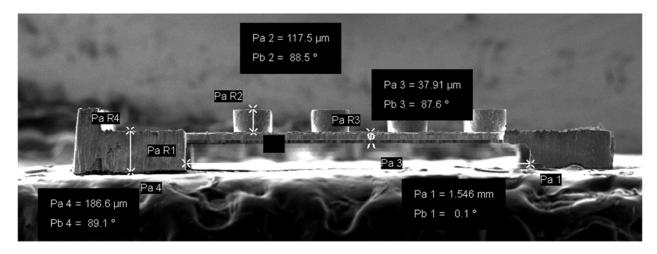

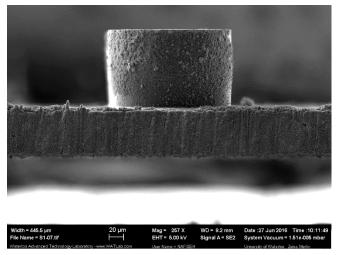

| Fig. 6.6. SEM photo of a prototyped sample. Dimensions shows better than 3 μm fabrication         |

| accuracy                                                                                          |

| Fig. 6.7. A cavity matched to the chip in dimensions                                            | 71 |

|-------------------------------------------------------------------------------------------------|----|

| Fig. 6.8. Analysis of the sensitivity of the antenna gain pattern to DRAAM-MMIC assembly        |    |

| misalignment                                                                                    | 7  |

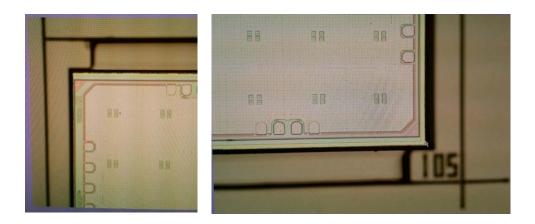

| Fig. 6.9. Wirebonded active die with the assembled DRAAM                                        | 72 |

| Fig. 6.10. Design under test: DC probing and power up the transmitter                           | 72 |

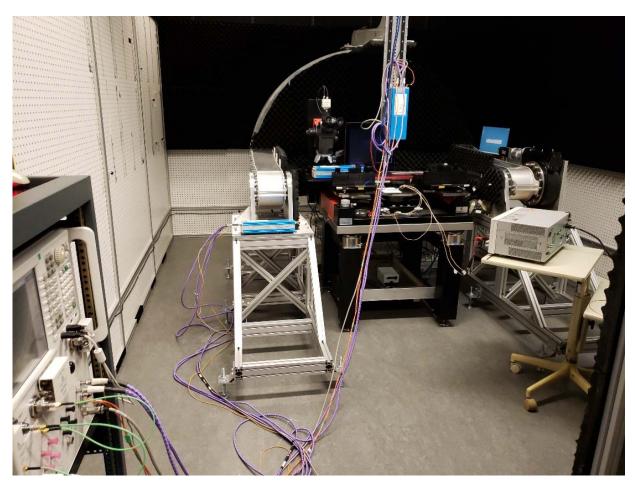

| Fig. 6.11. sub-THz probing station equipped with antenna radiation measurement system           | 73 |

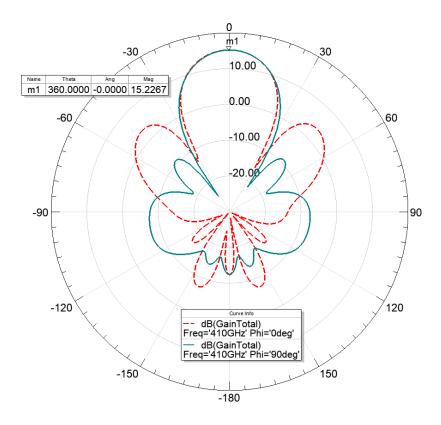

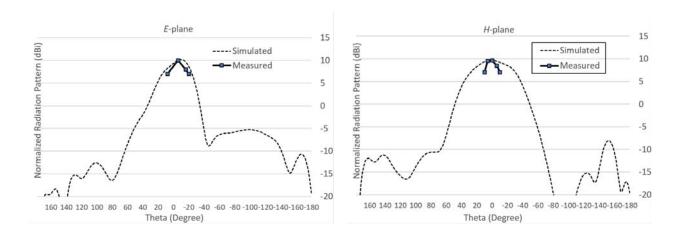

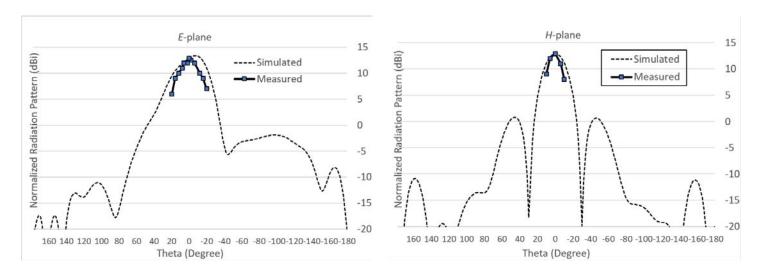

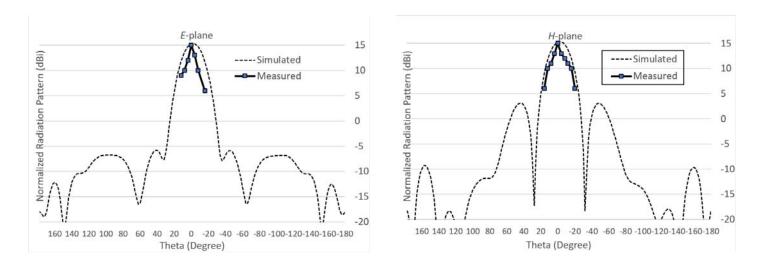

| Fig. 6.12. Quarter array radiation pattern. The 0.41 THz transmitter in 2×2 configuration       | 74 |

| Fig. 6.13. Half array radiation pattern. The 0.41 THz transmitter in 2×4 configuration          | 75 |

| Fig. 6.14. Full array radiation pattern. The 0.41 THz transmitter in the full 4×4 configuration | 75 |

### LIST OF ABBREVIATIONS

AiP: Antenna in Package

AoC: Antenna on-Chip

CIARS: Centre for Integrated Antenna and Systems

CPWG: Co-Planar Waveguide Grounded

DR: Dielectric Resonator

**DRA**: Dielectric Resonator Antenna

**DRAAT**: Dielectric Resonator Antenna Array Tray

DRAAM: Dielectric Resonator Antenna Array Module

**DRIE**: Deep Reactive Ion Etching

**EIRP**: Effective Isotropic Radiated Power

FBO: Feedback Buffer Oscillator

HTCC: High Temperature Co-fired Ceramic

**HRS**: High-Resistivity Silicon

LTCC: Low Temperature Co-fired Ceramic

MTL: Microstrip Transmission Line

**MS**: Microstrip

MMIC: Monolithic Microwave Integrated Circuit

OOK: On/Off Key

SOG: Silicon On Glass

TL: Transmission Line

TRX: Transceiver

# **Introduction to THz Source**

The Terahertz (THz) region of the electromagnetic spectrum is situated between infrared light and microwave radiation. Here, THz range is accepted as the range within 0.1-10 THz. THz technology is one of the emerging technologies that has applications in high-resolution THz imaging [1], spectroscopy of large bio-molecules like DNA [2], gas analysis [3], [4], and sub-μm-precision vibrometry based on the Doppler effect [5].

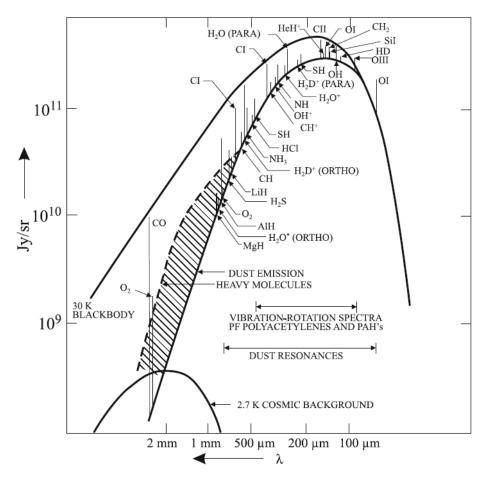

Half of the luminosity of the universe and 98% of all photons emitted since the Big Bang belong to THz radiation [6], containing information about the cosmic space, galaxies, stars and planets formation. The interstellar dust has a spectrum profile that ranges from  $\lambda$ =1 mm to 100  $\mu$ m (14 - 140 K below the ambient background on the earth). Historically, chemists and astronomers were the first who used THz spectroscopy for spectral characterization of the rotational and vibrational resonances and thermal-emission lines of molecules. Figure 1.1 shows the radiation spectrum of interstellar (dust, light and heavy molecules), a 30 K blackbody, and the 2.7 K cosmic background [7]. Through THz spectroscopy astrophysicists can probe into the early universe, star forming regions, and many other abundant molecules.

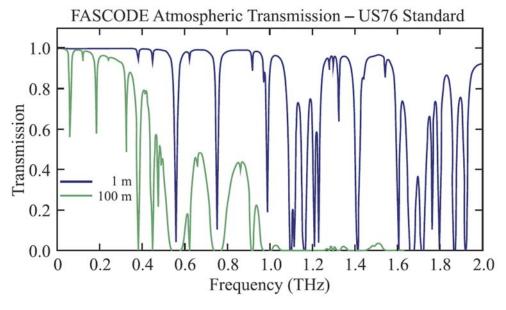

Air absorbs a THz signal power in wide spectral regions (except for narrow windows around f=35 GHz, 96 GHz, 140 GHz, and 220 GHz, and others shown in Fig. 1.2). Therefore, THz and millimeter waves are efficient at detecting the presence of water and therefore, are efficient to discriminate different objects on human body (water content of human body is about 60%) as clothing is transparent. In the longer wavelength region (f < 30 GHz) persons hiding behind a thin wall can be detected. In THz active imaging systems emission radiation frequencies should be inside an atmospheric transmission windows to avoid strong water vapor absorption.

Fig. 1.1. Radiation signature of 30 K blackbody. Dust and heavy molecules have emissions at THz frequencies [7]

Fig. 1.2. Transmission of THz signal in air at two different raining conditions

Due to strong absorption, the transmission spectra of a lot of materials can provide information about the physical properties of the materials investigated. An interesting application of THz radiation is the ability to penetrate and distinguish between non-metallic materials.

In many of these applications THz transmitter and receivers require sources with reasonable output power in the range of 25 to 50 mW. However, the realization of high efficiency signal generation is a challenge as THz frequencies are too high for conventional electronics and the photon energies are too small for optical methods. In other worlds, THz radiation is quite difficult to generate by the techniques commonly employed in the well-established neighbouring bands.

A high-efficiency THz source consists of two fundamental components. One is the electronic circuit that generates the THz signal source, another is the antenna that radiates the THz signal. Chapter 2 describes the high efficiency oscillator at 140 GHz proposed in this research. The MMIC is composed of 32 injection locked oscillators which are all connected to an on-chip central oscillator through an H-tree network. Chapter 3 describes the implementation of the H-tree network with the transmission line inside the MMIC. The design of antenna array which is realized with HRS dielectric resonator antennas is described in Chapter 4. This work targets a 420 GHz transmitter by 3<sup>rd</sup> harmonic signal generation from the 140 GHz oscillator. In Chapter 5 an active tripler circuit that follows the 140 GHz oscillator and its co-design with the dielectric resonator antenna is described. The top architecture of MMIC is described at the end of Chapter 5. Antenna array fabrication and its integration with the MMIC is described in Chapter 6. Measurement result of the integrated transmitter is described at the end of Chapter 6. We finally conclude this research in Chapter 7.

In the following of this chapter, we briefly review some important sub-THz phase array transceivers (TRX) reported in recent years. It begins by reviewing the work done on THz array transceivers, and then reports the most fundamental work previously completed on critical components such as frequency synthesis, antenna and the interconnect aspect of THz chips.

#### 1.1 Integrated Antenna Array Systems and Transceivers

In order to generate sufficient THz radiation power for practical applications, a multiantenna/element source with free-space power combining is preferred. Many of the published transceiver designs above 200 GHz utilize integrated on-chip antenna arrays due to the propagation loss of the signals at THz. However, antenna on-chip (AoC) hardly provides the best in class efficiency. One of the pioneer works, published in [8] reports a 0.38 THz single transceiver in SiGe BiCMOS, using two patch antennas with simulated gain of 6.6 dBi and radiation efficiency of  $\eta_{rad} = 46\%$ . In 32nm SOI CMOS process, [9] demonstrates a 210 GHz TRX incorporating a 2×2 on-chip dipole TX antenna. A 260 GHz fully integrated non-coherent OOK transceiver is presented in [10] in 65nm CMOS using a half-width leaky-wave on-chip antenna. A distributed array radiator (DAR) is introduced in [11]. The authors have developed a 4×4 on-chip radiating array in 45nm SOI CMOS, with an EIRP of 9.4 dBm at 0.28 THz. A 110 GHz 4×4 transmitter in SiGe BiCMOS is reported in [12]. It uses on-chip quartz antennas with 45% simulated efficiency. The on-chip antennas are implemented using a 100  $\mu$ m thick quartz substrate which is attached to the silicon RFIC with epoxy.

IBM researchers have shown an Antenna-in-Package (AiP) that uses a folded dipole antenna suspended in a metal cavity using plastic mold injection technology with 90% efficiency for 60 GHz radio [13]. Toshiba engineers have demonstrated another AiP, with bonding wires, forming a three-dimensional triangular loop which has some distance from the chip [14]. A 245 GHz transmitter (TX) with an on-chip antenna has been realized in [15] in SiGe BiCMOS, which consists of a push-push VCO followed by a frequency doubler and a transformer coupled one-stage power amplifier. With localized backside etching for the on-chip antenna, the authors have been able to achieve 75% gain and more than 7 dBi in simulation. A 4×4 element I-Q W-band (85–95 GHz) transceiver is implemented in [16] in 45nm SOI CMOS.

A less complex way of beam forming can be achieved through beam-switching. [17] presents a 220–240 GHz four-element Butler matrix beam switching chip in SiGe BiCMOS technology with 2 dB insertion loss at 220 GHz. From the same authors, [18] reports a 220–250 GHz phased-array circuits in BiCMOS. This is one of the few articles that employs a fully RF phase shifting architecture at this range of frequencies. Each channel exhibits 360° phase control with 18 dB of amplitude control.

In [19] and [20], THz phased arrays based on inter-coupled harmonic oscillators were proposed in a 130nm SiGe technology and a 65nm CMOS technology, respectively. In [21], a phased array based on amplifier–multiplier chains was implemented at 0.4 THz using a 40nm CMOS technology. A short comparison between the discussed work is shown in Table 1-1.

#### 1.2 Sub-THz Frequency Synthesizers

A significant challenge in building a low-cost sub-THz system is the design and development of a low-phase noise and efficient signal source. This is due to high DC power consumption and low efficiency of the solid-state frequency synthesizers. The so-called Mason's invariant, or the unilateral power gain of a transistor decreases by a slope of 20 dB/dec beyond  $f_{max}$  /2 and becomes unity at  $f_{max}$  [22]. The  $f_{max}$  of today's silicon technologies has not been improved enough by scaling down the device sizes to cover the THz gap. In addition, three main factors which are: the loss of passive elements, skin effect, and EM coupling to lossy substrate reduce the realizable fundamental frequency of an oscillator much lower than  $f_{max}$  of the technology.

Table 1.1. A short comparison between the recent work

|              | Freq. | Prad  | PDC   | DC-to-THz | EIRP  | Antenna Type                                          | Config.                            | Tech.          |

|--------------|-------|-------|-------|-----------|-------|-------------------------------------------------------|------------------------------------|----------------|

|              | (GHz) | (dBm) | (W)   | Eff. (%)  | (dBm) |                                                       |                                    |                |

| [19]         | 344   | -6.8  | 0.64  | N/A       | 4.9   | 2×2 Patch                                             | Inter-Coupled Osc.                 | 130nm SiGe     |

| [20]         | 338   | -0.9  | 1.54  | 0.53      | 17    | 4×4 Patch                                             | Inter-Coupled Osc.                 | 65nm Bulk CMOS |

| [21]         | 390   | -7    | 1.5   | 0.13      | 8     | 1×8 Patch on Quartz                                   | Multiplier                         | 45nm SOI CMOS  |

| [23]         | 530   | -12   | 0.156 | 0.4       | 25    | 4×4 Ring with Silicon Lens                            | Non-Coherent Osc.                  | 130nm SiGe     |

| [24]         | 553   | -27   | 0.172 | 0.01      | N/A   | Ring with<br>Silicon Lens                             | No Array<br>PLL                    | 65nm Bulk CMOS |

| [25]         | 546   | -9    | 1.3   | 0.1       | 24.4  | 2×4 Ring with<br>Silicon Lens                         | Inter-Coupled Osc.                 | 65nm Bulk CMOS |

| [26]         | 428   | -6.8  | 0.164 | 1.42      | 15    | Slot with<br>Silicon Lens                             | No Array<br>Osc.+Multiplier        | 130nm SiGe     |

| [27]         | 1010  | -10.9 | 1.1   | 0.074     | 13.1  | 6×7 Slot with<br>Silicon Lens                         | Inter-Coupled Osc.                 | 130nm SiGe     |

| [28]         | 528   | -22   | 0.019 | 0.332     | -7.4  | Slot with<br>Dielectric Lens                          | No Array<br>Osc. + Multiplier      | 28nm Bulk CMOS |

| [29]         | 342   | -10.5 | 0.425 | 0.21      | 1.2   | 1×4 Patch                                             | Inter-Coupled Osc.                 | 130 nm SiGe    |

| [8]          | 380   | -13   | 0.364 | NA        | -13   | 2×2 Patch                                             | Harmonic Osc.                      | SiGe BiCMOS    |

| [30]         | 160   | 5.5   | 2.2   | NA        | 18.8  | 4×4 Patch-In-Package                                  | I-Q Array<br>Active Multiplier     | 65nm CMOS      |

| [31]         | 144   | 10.1  | 0.457 | NA        | NA    | Bondwire dipole<br>Dielectric Lense                   | No Array<br>Active Multiplier      | 65nm CMOS      |

| [10]         | 260   | 13    | 1.17  | NA        | 5     | 2×2 On-Chip Leaky-<br>wave                            | Osc. +<br>Active Multiplier        | 65nm CMOS      |

| [11]         | 280   | 9.4   | 0.820 | NA        | -9    | 4×4 On-Chip<br>Loop                                   | Dist. Osc. +<br>Active Mult. chain | 45 nm SOI CMOS |

| [12]         | 110   | 1     | 3.4   | NA        | 23    | 4×4 On-chip Dipole +<br>Off-chip Dielectric<br>Quarts | Single Osc. +<br>power-divider     | SiGe BiCMOS    |

| [15]         | 245   | 1     | 0.380 | NA        | 7     | On-chip<br>Dipole                                     | No Array                           | SiGe BiCMOS    |

| This<br>Work | 420   | 7     | 0.7   | 0.7       | 22.8  | 4×4 Off-Chip DRA                                      | 32 Injection locked Osc.           | 65nm CMOS      |

In order to generate THz frequencies beyond the  $f_{max}$  of the technology, two approaches have been followed in literature. The first approach is the use of harmonic oscillators, the second is through multipliers. Harmonic oscillators [32], occupy less chip real estate and consume less

DC power, but generally at the cost of a higher phase noise level when compared with the multiplier chain solution driven by ultra-stable low-frequency sources. In Harmonic oscillators, odd-harmonic or even harmonic of the fundamental frequency is extracted from a differential or common point of the oscillator circuit, respectively. Examples of the harmonic oscillators include "push-push" topologies (where the second harmonic is sensed) or "edge-combining" arrangements [33], also known as "linear superposition" [34] or "N-push" oscillators [35] [32]. Super-harmonic oscillators, typically provide only a single-ended output. If the application requires a differential output, they require Baluns, 90° couplers and buffers. In addition, the finite lower harmonics that leak to the output of a super harmonic topology may down-convert unwanted signals in a receiver. Creative signal source designs beyond 0.5 THz, based on harmonic oscillators, have been proposed in [28] [23] [24] [27]. A systematic approach applied for the design of CMOS N-push oscillators achieved an output power of -17 dBm at 256 GHz and -7.9 dBm at 482 GHz employing 3-stage single-ended ring topologies in a 130nm and a 65nm CMOS process node, respectively [36]. In [32], a triple push oscillator is designed using an optimal bias point proposed by the same researchers in their previous work. Harmonic oscillators are also implemented to realize tunable VCOs [37]. A high output power tunable VCO, utilizing eight pairs of oscillator-phase shifter/coupler and extracting the fourth harmonic to create an output at 256 GHz is shown in [38]. Signal sources at 220-330 GHz using SiGe HBT technology, have been demonstrated in [39], using a Colpitts-Clapp push-push topology.

In the second approach for generating frequencies above  $f_{max}$ , an active [40] or passive [37] multiplier is driven by a fundamental oscillator. An output power of -6.6 dBm at 244 GHz using a travelling-wave doubler in 65nm CMOS is shown in [40] [41]. Authors in [42] and [43] reported multiplier circuits in 0.13 $\mu$ m SiGe HBT with output power of -3 dBm at 325 GHz and -29 dBm at 825 GHz, respectively.

Another approach which vastly effects the performance of the oscillator circuit is the use of III–V technologies, such as InP [44], InAs [45], InGaAs [46], versus silicon-based Si/SiGe technologies. III-V devices in general offer better power and  $f_{max}$ . State-of-the-art fundamental frequency oscillators at 573 GHz with an output power of -19 dBm have been reported using InP DHBT device ( $f_{max} = 850$ GHz) [47]. Multiplier circuits in III-V MMICs at 300 GHz and 195 GHz are demonstrated in [48] to have an output power of -6 dBm and 0 dBm, respectively. The circuit topologies and integration solution proposed in this project is not limited to silicon-based or III-V

technologies for the MMIC and can be applied in both technology flows. However, our choice of TSMC65nm was due to the accessibility and lower fabrication costs of this technology.

#### 1.3 Packaging and Antenna Module

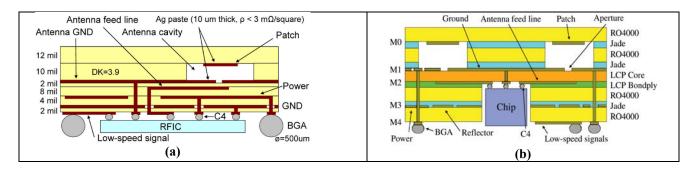

The integration of THz phased arrays systems, [49] [50] at sub-THz frequencies requires low-loss transmission lines to distribute high frequency signals efficiently between the transceiver IC and other off-chip system components, such as antenna. Use of low or high temperature co-fired ceramic (LTCC/HTCC) substrates [51] [52], or organic packages and PCBs such as Liquid Crystal Polymer (LCP) [53] [54] [55] [56] have been tried before for system integration at sub 150 GHz. Fig. 1.3 shows typical layer stacking arrangements with these two approaches. A 2×2 160 GHz pulse transceiver in CMOS is reported in [57] using FR4 for the antenna substrate which shows 18 dBi directivity in simulation.

Fig. 1.3 (a) LTCC package arrangement [52]. (b) Organic packaging [53]

This work does not repeat any of the aforementioned and conventional integration techniques. Instead, it is based on a new idea of using a much superior material HRS. The HRS has been used to implement dielectric waveguides in photonic applications. A high field confinement inside silicon waveguides is well suited for creating low-loss transmission lines at THz frequencies. Realization of fully dielectric waveguide interconnects with IC-compatible processes has not been shown yet. The most pertinent work that has been done in this field is published in [58], where authors have developed a HRS-filled metallic-waveguide. They have shown how the metal on the top face of the waveguide can be patterned to implement slots for integrating antennas. Their work is essentially a metallic waveguide that will still suffer from the metallic losses at higher frequencies. Researchers at the Centre for Intelligent Antenna and Radio Systems (CIARS) at the university of Waterloo, have fabricated and measured many types of HRS

passive structures, e.g. dielectric waveguides [59] and antennas [60] [61] with exceptional performances at THz frequency. [61] shows a fully silicon five-beam annular grating antenna at 77 GHz with a remarkable radiation efficiency of 91% and a bandwidth of 5 GHz. This antenna has the advantages of low-cost, planar structure, ease of fabrication and integration in a silicon-platform. The work reported in [60] shows another high efficiency antenna on high resistivity silicon (HRS) at 60 GHz. The same antenna has been fabricated on a new integrated technology platform called silicon-on-glass (SOG), using photo-lithography and dry etching of the Si layer of the SOG wafer [59]. This work is going to use the same superior methodologies and technologies developed at CIARS over the past few years, to utilize HRS for implementation of dielectric resonator antennas. In addition, this work proposes a novel solution to directly couple a MMIC to an off-chip HRS antenna module.

# CHAPTER 2

### 2 Frequency Synthesizer

A high efficiency continuous-wave (CW) signal generator at 420 GHz, beyond  $f_{max}$  of the TSMC65nm technology node, is implemented in this work. In our design, a frequency multiplier which is a tripler circuit, follows an oscillator at 140 GHz. The oscillator uses a transmission line for the inductor of the resonator tank. This high Q implementation of the tank has achieved a record phase noise. A new topology called "buffer-feedback oscillator", in which the peaking inductors of the VCO buffer couples to the VCO tank is implemented in [62]. Our circuit uses a similar buffer feedback mechanism, but uses transmission line which reduces the total circuit loss.

#### 2.1 Oscillation Close To $f_{max}$

$f_{max}$  is defined as the frequency at which the unilateral power gain of an active device falls to unity. Therefore, it is believed that  $f_{max}$  set the upper limit on the oscillation frequency. Based on the small signal model of a MOSFET, and ignoring the effect of drain-bulk junction capacitance,  $C_{DB}$ , it can be shown that for a MOSFET:

$$\omega_{max}^2 = \frac{g_m^2 r_o}{4R_G (C_{GS} + C_{GD})[C_{GS} + (1 + g_m r_o)C_{GD}]}$$

(2.1)

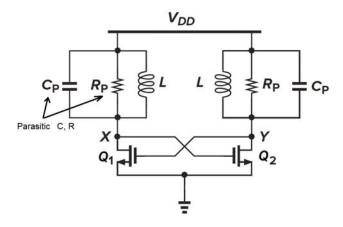

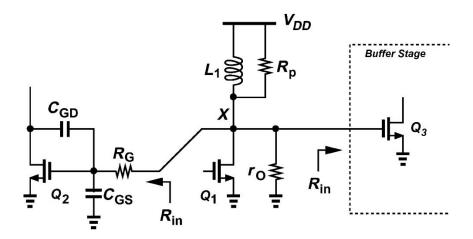

$R_G$  denotes the lumped equivalent value of the gate resistance [16]. The effect of drain-bulk junction capacitance ( $C_{DB}$ ) is ignored, as the transistor is assumed to be a unilateral device and embedded within a lossless network. A unilateral device nulls the effect of  $C_{DB}$ , as the input and output ports of the device are matched for maximum power transfer. Achieving an oscillation frequency near  $f_{max}$  from an actual design is almost impossible because of the loss of on-chip interconnects and passive network. My simulations predicted an  $f_{max}$  of roughly 280 GHz for 65nm nMOS devices (using lumped BSIM4 model) with a drain current density of 0.8 mA/ $\mu$ m. This current density differs from the value of 0.3–0.4 mA/ $\mu$ m recommended in [63] for maximum  $f_T$ . Gate resistance could be a cause of this discrepancy which directly impacts  $f_{max}$  but not the  $f_T$  [64]. A capacitor-less cross-coupled LC oscillator topology is used in this work, due to its robust operation when implemented using MOS devices. Fig. 2.1 shows a simplified version of this topology.

Fig. 2.1. Capacitor-less cross coupled LC-oscillator

$C_p$  denotes the total parasitic capacitance seen at the output node and  $R_p$  the equivalent parasitic parallel resistance of the tank at the resonance frequency which is equivalent to  $R_p = QL_I\omega$ . To design this circuit at frequencies above 100 GHz, the loss mechanisms in the circuit need to be understood properly. As shown in Fig. 2.2, the oscillating signal within the oscillator positive feedback loop is affected by: (1)  $R_p$ ; (2)  $r_o$  of  $Q_I$  and  $Q_2$ ; (3)  $R_G$  of  $Q_I$  and  $Q_2$ ; and (4) the input resistance of the following stage, the buffer. If  $R_o$  represents all these losses at the node X, shown in figure Fig. 2.2, then  $Re\{Y_{in}\}$  at resonance becomes (2.2):

$$Re\{Y_{in}\} = \frac{(1 + g_m R_0) R_0 C_{GD}^2 \omega^2}{1 + R_0^2 C_{GD}^2 \omega^2}$$

(2.2)

Fig. 2.2. Sources of loss in a cross-coupled oscillator

#### 2.2 Feedback Buffer Oscillator (FBO)

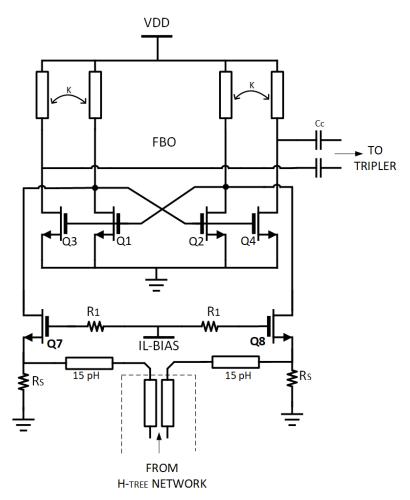

The cross-coupled oscillator implanted in this work uses a buffer feedback configuration as shown in Fig. 2.3. In this configuration, the peaking inductors of the buffer couple some of their energy back to the oscillator tank inductors and consequently decrease the loss of the tank. This will result in an increase in the obtainable oscillation frequency.

Fig. 2.3. Proposed buffer-feedback 140 GHz oscillator with transmission-line inductors

The tank inductors and buffer peaking inductors are implemented with 50  $\mu$ m length and 4  $\mu$ m thick transmission lines, each having 45 pH inductance and shown as  $TL_{1,2,3}$  & 4 in Fig. 2.3. Transmission lines of cross-coupled and buffer, at each side of the differential pair, are routed adjacent to each other in the layout with 1.5  $\mu$ m space between them. This results in mutual inductance (M) of 37 pH between the adjacent transmission lines. As shown in [65], this topology lowers the effect of tank parasitic capacitance by a factor of two. Total intrinsic and parasitic capacitance looking into the cross-coupled drains become (2.3):

$$C_{CC} \cong (1 + g_m R_G) C_{GS}/2 + C_{DB}/2 + 2 C_{GD}$$

(2.3)

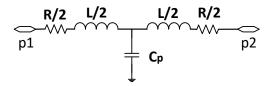

where R<sub>G</sub> is the base resistance of C<sub>C</sub> transistors;  $g_m$  is transconductance of  $Q_I$ . The  $C_{GS}$ ,  $C_{DB}$ , and  $C_{GD}$  are gate-source, drain-bulk, and gate-drain parasitic capacitances, respectively. Oscillation frequency can be calculated from  $\omega_{osc}^2 = 1 / [2 (L_t + M) C_D]$ , where C<sub>D</sub> denotes the total parasitic

capacitance across the tank:  $C_D \cong C_{CC} + C_{t/4}$ , and  $C_t$  and  $L_t$  represent capacitance and inductance of each identical TL, obtained from T-section equivalent circuit. For circuit analysis, a T-section of lump components as shown in Fig. 2.4 used to model the TL. In this model,  $C_p$ , R, and L were obtained from ABCD parameters from EM simulation of the TL line as:  $C_p = Im\{C^{-1}\}/\omega$ ,  $R/2 = Re\{(A-1) C\}$ , and  $L/2 = Im\{(A-1) C\}/\omega$ .

Fig. 2.4. A T-model for TL

Current density of 0.8 mA/ $\mu$ m is found to be an optimum value to maximize transistors transconductance at 140 GHz. To obtain oscillation, cross-coupled and buffer transistors,  $Q_{1, 2, 3}$  & 4, are scaled with the same size and number of fingers to 8×0.8  $\mu$ m. Therefore, each of the transistors in Fig. 2.5 has a total width of 6.4  $\mu$ m.

An output transformer is designed for measurement of oscillator differential output. It uses two turns of metal-8 (M8) as the primary coil and one turn of metal-7 (M7) as the secondary coil. One port of secondary coil is connected to the output pad as shown in Fig. 2.5. Primary and secondary layout routes are staggered to reduce coupling capacitance between the two coils. The transformer shows an insertion loss of 3.6 dB at 140 GHz in simulation.

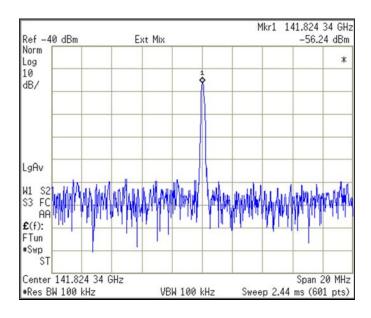

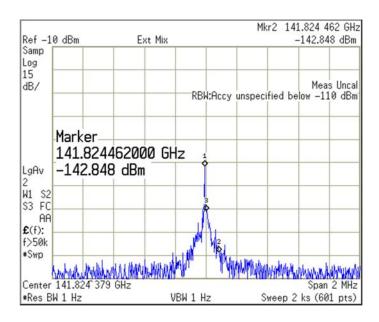

A D-band (110-170 GHz) OML harmonic mixer in conjunction with a Keysight Technologies spectrum analyzer is used in our measurement setup. The external harmonic mixer has an average loss of -60 dB across its 60 GHz band. In addition, we measured 3.4 dB of signal path loss for the combination of a Cascade waveguide Infinity probe, S-shape waveguide interconnect, and die pad using a pad-to-pad through-structure implemented on another test die. As shown in Fig. 2.6, the measured output tone has a power of -56.2 dBm at 141.824 GHz. Taking into account all the aforementioned path losses, this indicates a better than 7.2 dBm output power from the oscillator under test. The existence of the external harmonic mixer does not allow us to use the spectrum analyzer to directly measure the phase noise. However, setting the resolution and video bandwidth of the spectrum analyzer to 1 Hz, we measured better than -83 dBc/Hz signal

noise at 100 KHz offset as shown in Fig. 2.7. This noise is the combination of oscillator phase noise and that of the harmonic mixer. The oscillator core consumes 23.38 mW DC power from a 1.1 V supply. This translates to 22 % DC-to-RF efficiency.

Fig. 2.5. Layout of 140 GHz oscillator passives and interconnects including the output transformer. *AP* layer (TSMC65nm top metal layer) is not shown.

Fig. 2.6. Oscillator output tone. Peak power includes the harmonic mixer insertion loss and the path loss of measurement

Fig. 2.7. Oscillator output noise at 100 KHz offset

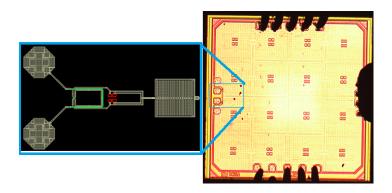

The micrograph of the oscillator is shown in Fig. 2.8. However, as the entire chip is covered by the top metal AP layer, none of the underneath circuits are visible. The oscillator core occupies only  $50\times50\mu\text{m}^2$  of the chip area.

Fig. 2.8. Test chip of 140 GHz oscillator. Top metal layer (AP) is covering the underneath circuits

# CHAPTER

## Injection Locking Network

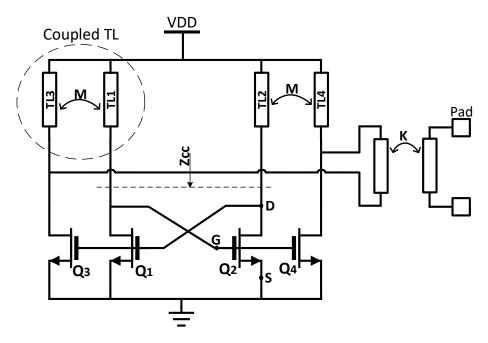

A fundamental coherency requirement of any antenna array dictates that each antenna element is driven with a signal source which is phase locked to those of the other elements. In a case where each antenna element is driven by a separate local oscillator, a coherence mechanism needs to be implemented to phase lock the independent local oscillators.

An oscillator phase can be controlled by injecting a signal from outside of the circuit into the feedback loop. This adds energy to the circuit at the injection frequency, making it easier for the circuit to sustain oscillation in-phase with the input signal. If the injected signal is strong enough, the oscillator will follow the injected signal phase instead of oscillating at in a free running mode. In this case, the oscillator is said to be "injection locked" in this condition. If many oscillators are injection locked by providing a reference signal paths to them, they will oscillate as a synchronized ensemble which is the scheme pursued in this work. In this chapter the injection locking transmission line network that carries the reference signal to the individual oscillators across the chip is explained. Planar on-chip transmission lines suffer from losses on the order of 1–3 dB/mm (or more) at THz. Furthermore, coupling to neighbouring structures can generate unwanted parasitic modes (e.g., parallel-plate modes and surface waves). The co-planar microstrip line implemented in this work has the smallest insertion loss reported to the best of our knowledge.

#### 3.1 Reference Signal Distribution Network

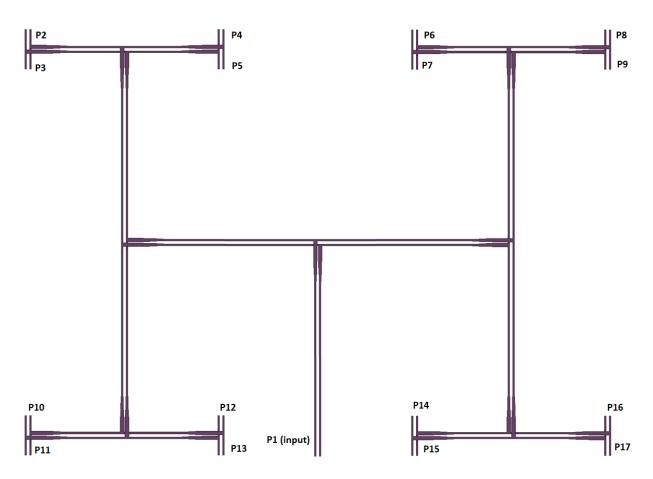

A balanced H-tree clock distribution topology exhibits identical delay to the end nodes, due to its structural symmetry from the root of the distribution to all branches. If the termination impedance at the end nodes are matched to the characteristic impedance of the network, the reflection loss and clock skew can be zero. A passive balanced tree distribution network also exhibits a good tracking across Process-Voltage-Temperature (PVT) variations. T-junctions in the H-tree split the input signal into two branches, and must provide similar impedances at all ports in order to create the transmission line segments identical in the H-tree. This scheme also avoids incremental increase in the characteristic impedance of the transmission lines toward the root of

the distribution. In this work, an H-Tree composed of  $100~\Omega$  differential co-planar waveguide-grounded is designed and implemented as shown in Fig. 3.1. Design of the H-tree starts with designing a  $50~\Omega$  transmission line which is described in 3.2. Subsequently, the design of the differential  $100~\Omega$  CPWG is covered in 3.3. Modeling and simulation results of the proposed differential tapered T-junction are described in 3.4.

Fig. 3.1. H-tree differential clock distribution network

#### 3.2 Microstrip Transmission Line (MTL)

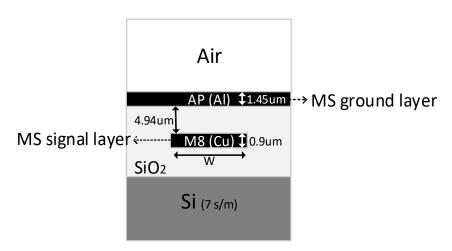

TSMC65nm technology with 9 metal layer stack-up configuration is used in this project to design a MTL structure. The line is using 0.9  $\mu$ m thick M8 for the signal and topmost 1.45  $\mu$ m thick aluminum layer (AP) as the ground with 4.95  $\mu$ m spacing between the two layers as shown in Fig. 3.2. All the stack up dielectric layers of TSMC65nm die are simplified and modeled with just two dielectric layers. The first layer from top is SiO2 with  $\varepsilon_r$  of 4.0 and loss-tangent = 0.002 and thickness of 11.025  $\mu$ m which represent all the intermediate dielectric layers between metal

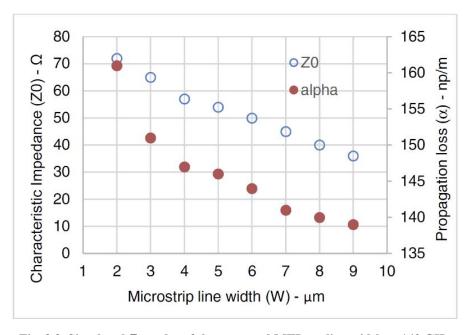

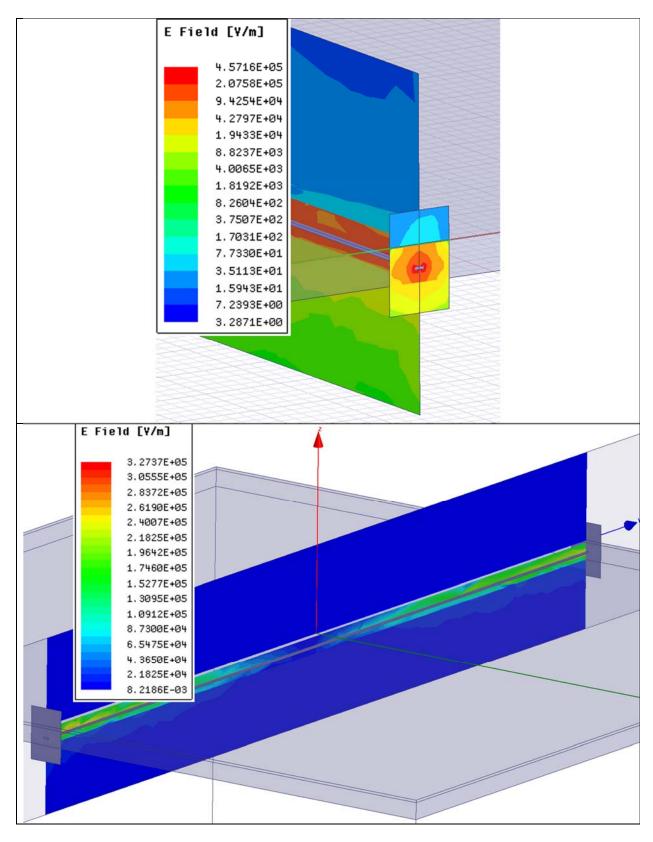

layers of TSMC65nm. The bottom layer is a 300  $\mu$ m lossy bulk silicon with  $\varepsilon_r$  of 11.9 and conductivity of 7 S/cm. The proposed MTL design is rigorously analyzed by the full-wave HFSS electromagnetic simulator. Fig. 3.4 shows E-field plot of the line when propagating a 140 GHz signal. Propagation loss ( $\alpha$ ), and characteristic impedance ( $Z_0$ ) are calculated for different widths (W) of the MTL as shown in Fig. 3.3. The propagation loss,  $\alpha$ , has the same range of values as achieved in conventional implementations of MTL in the same technology [4] [5], which use 3.4  $\mu$ m thick M9 as signal line over M1, M2 or M3 ground layers. However, the proposed arrangement (Fig. 3.2) offers better isolation from the top of the die space.

Fig. 3.2. Design of MTL in TSMC65nm. AP layer is used as MTL ground

Fig. 3.3. Simulated Zo and α of the proposed MTL vs. line width at 140 GHz

Fig. 3.4. Simulated field of MTL in TSMC65nm with 9 metal layers. AP is the ground layer.

#### 3.3 Differential Co-Planar Waveguide Grounded (CPWG)

A differential CPWG is designed based on the basic MTL line described in the previous section. The CPWG uses M8 layer for differential signal pair and AP for top ground. The space between the negative and positive lines of the differential pair is set to 6  $\mu$ m. The gap between the signal line and the siding ground (M8) at both sides of the pair is 5  $\mu$ m. M8 and AP grounds are connected through M9 layer and M8 /M9 VIAs, forming two ground shielding walls at both sides of the pair. Fig. 3.5 shows E field of the proposed CPWG when propagating a differential signal at 140 GHz. Fig. 3.6 shows the performance of this line.

Fig. 3.5. Proposed differential CPWG. E-field of propagation of a 140 GHz differential signal

Fig. 3.6. Insertion loss (S21) and return loss (S11) of 1 mm of the differential CPWG

#### 3.4 Tapered T-junction

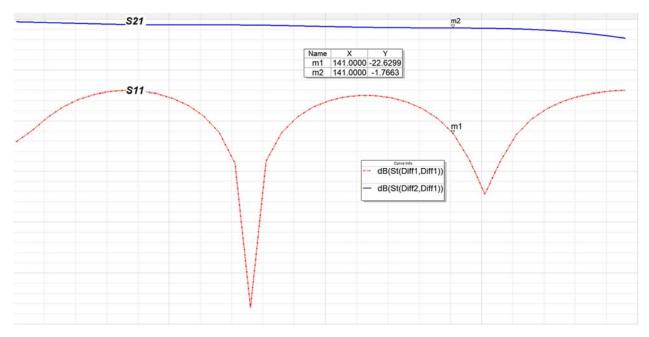

The most critical component in the proposed differential H-tree clock distribution network is T-junction. The layout of the differential T-junction can not have a symmetrical design, since one of the signals must overlay the other, which will disturb the propagation mode. Changes in the propagating mode, cause phase offset between the positive and negative signals traveling in the differential pair after passing through a T-junction. The differential CPWG T-junction which is designed in this work have  $Z_0$  of 50  $\Omega$  at each port. When the two 50  $\Omega$  lines merge at the intersection, the resulting impedance will be 25  $\Omega$ . There is a tapered transitional section that converts the  $Z_0$  of 25  $\Omega$  back to 50  $\Omega$ . In order to cross pass two signal routes, one of the signals transits to the M7 layer which is routed underneath another signal line, as shown in Fig. 3.7. An optimum number and arrangement of VIAs between M7 and M8 is found through EM simulations, which resulted in the least amount of field perturbation due to this transition. Simulation shows -1.1 dB insertion loss for this design as shown in Fig. 3.8. Reflection loss is shown in Fig. 3.9.

Fig. 3.7. T-junction implementation with differential CPWG

Fig. 3.8. Simulated S21 and S31 shows -1.15 dB insertion loss

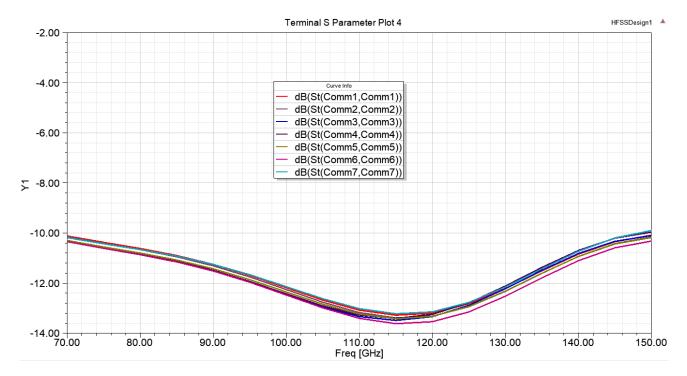

Fig. 3.9. Reflection coefficient (S11) of all ports which is better than -9.6 dB

#### 3.5 H-Tree

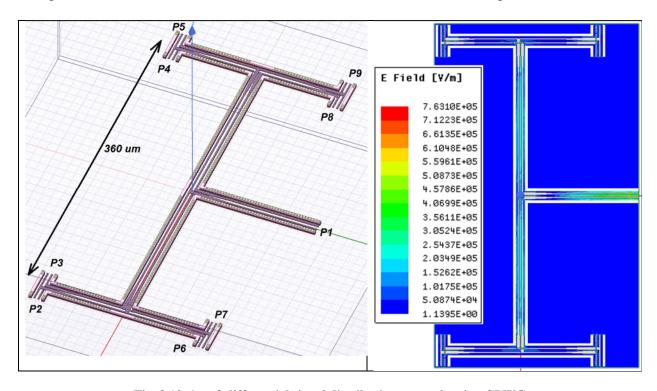

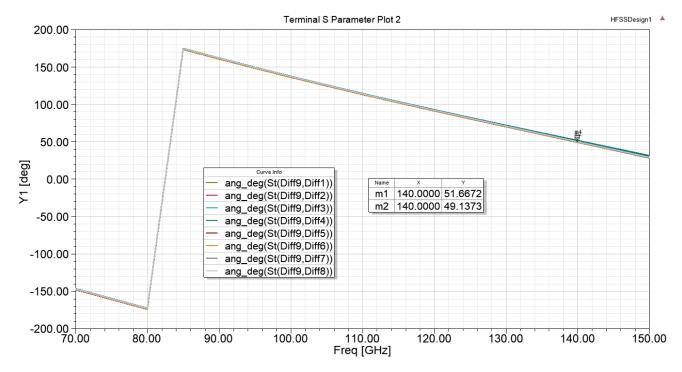

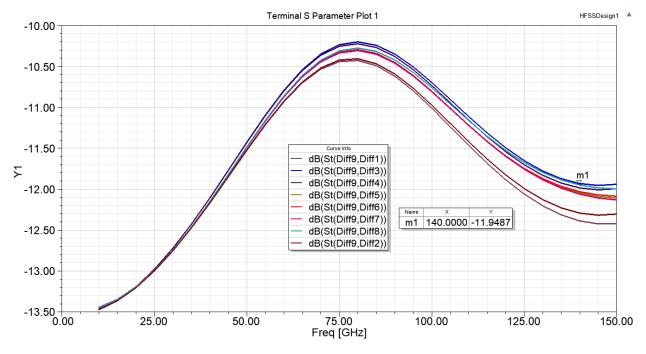

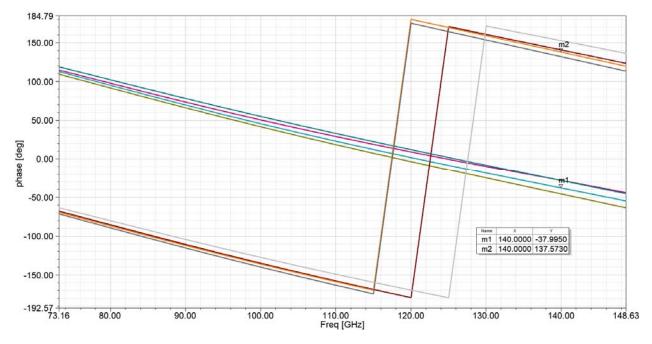

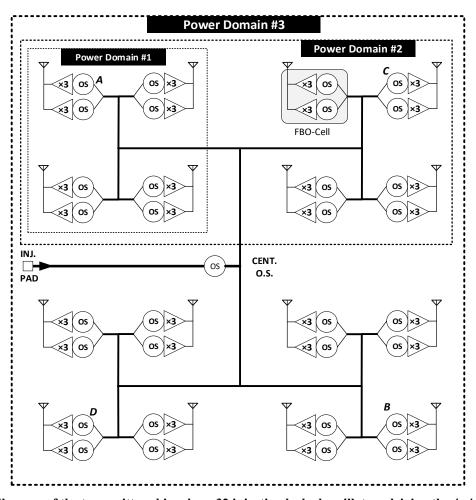

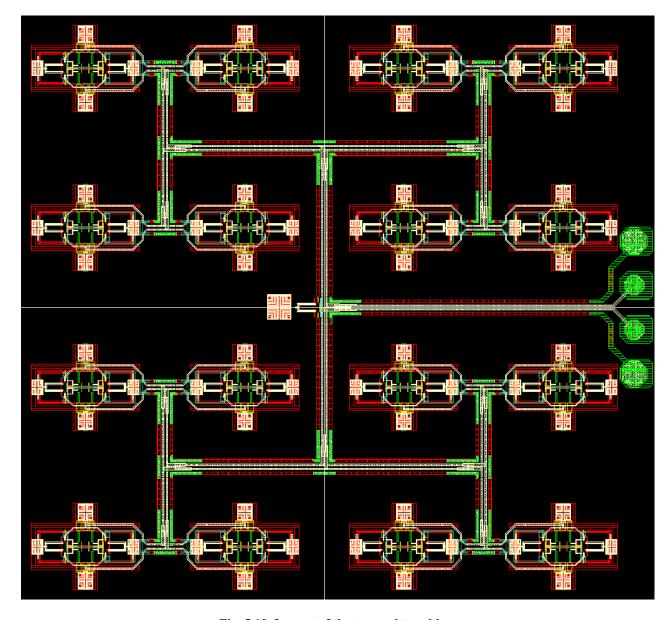

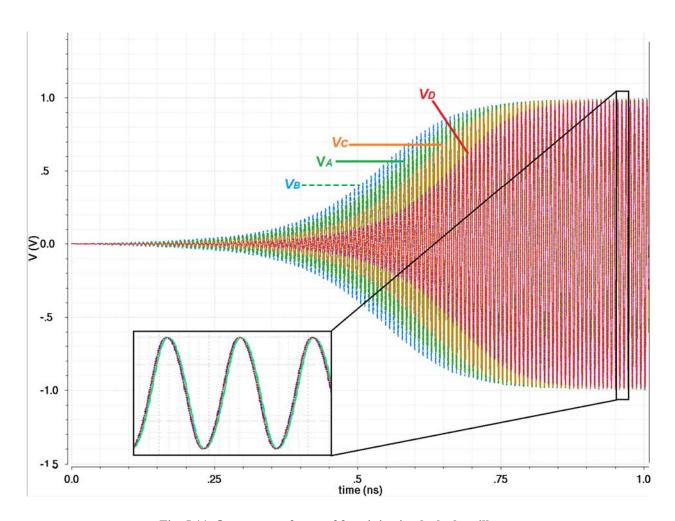

An H-tree network forming a uniform 1-to-8 signal distribution grid, which is composed of differential CPWG and T-junctions, is modeled and simulated as shown in Fig. 3.10. As shown in Chapter 5, the layout of the branches are designed based on the 4×4 array structure. It is in accordance with that the distance between adjacent elements and therefore local oscillators in the final transmitter chip layout, therefore set to  $\lambda \theta/2 = 360 \mu m$ . Clock skew of the network is calculated by comparing the phases of signals at end nodes and overlaying the phases of S21, S31, ... S91, as shown in Fig. 3.11. Clock skew is simulated to be better than 2.5° across the network. All ports are impedance matched to  $100 \Omega$  differential load. Reflection loss of all ports are depicted in Fig. 3.12. Insertion loss at end nodes are better than 2 dB as shown in Fig. 3.13.

Fig. 3.10. 1-to-8 differential signal distribution network using CPWG

Fig. 3.11. Phase of S21, S31, ..., S91

Fig. 3.12. Reflection coefficient at all ports

Fig. 3.13. Insertion loss for all the end port.

Plotting the phases of each individual signal when driven in differential mode, with 180 phase shift, is the best indicator for testing the performance of H-tree. Ideally, signals at each port must show the same 180° phase difference after propagating through the tree which indicates the differential symmetry mode has been preserved. This is shown in Fig. 3.14.

Fig. 3.14. Differential pairs show 174° phase difference at the end ports

# CHAPTER

### Dielectric Resonator Antenna Array

High conduction loss in metallic structures at sub-THz frequencies (100 GHz to 1 THz) severely limits their efficient usage over this range of frequencies. Besides, excessive size reduction and required higher precision, will considerably increase the cost and fabrication complexity of high gain, high performance metallic antennas such as open waveguide and horn antennas. An attractive alternative is antennas fully made of low loss dielectric materials. The Dielectric Resonator Antenna (DRA), introduced in early 1980's (see [66] for example). Various modes can be excited in dielectric resonator antennas, using proper type of excitation mechanism. During the 90's, emphasis was placed on applying analytical or numerical techniques for determining input impedance, fields inside the resonator and Q-factor [67] [68] [69] [70]. Current DRA literature focuses on compact designs to address portable wireless applications. Among them, new DRA shapes or hybrid antennas are developed for enhancing the antenna impedance bandwidth [71] [72] [73] or multiband antenna applications [74].

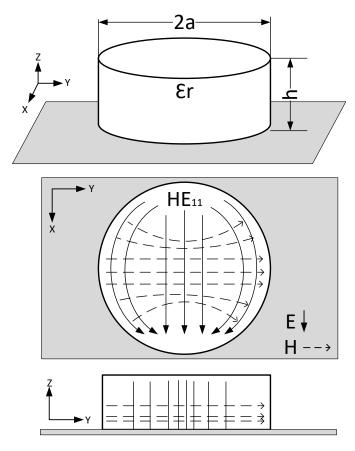

DRA has multiple electromagnetic modes at different frequencies. Different modes create radiating patterns with distinct profiles (number and position of lobs and nulls). In this work a broadside radiation pattern with a single main lobe is desired. A DRA that operates in its fundamental mode creates a broadside pattern.

DRA geometry must meet various requirements including: the resonant frequency, the impedance bandwidth, and the modal field distribution inside the resonator and its corresponding radiation pattern. Cylindrical shaped DRAs are used in this work as they offer great design flexibility. Both resonant frequency and Q-factor are dependent on the ratio of radius to height of the cylinder, noted as a/h in this research. As the first step towards designing a 420 GHz DRA antenna, analytical modal analysis of a cylindrical DRA will be performed to obtain initial optimal design parameters quickly and with reasonable accuracy. Then the design will be rigorously analyzed by a 3D EM simulator. Differential excitation and a novel loss-less power combining technique inside DRA is then scaled into a  $4\times4$  array.

#### 4.1 Theoretical Derivations and Modal Analysis of DR

For radiation pattern and resonant frequency calculation, a simple theory utilizing the magnetic wall boundary condition has been shown to correlate well with rigorous simulation and measurements. The geometry of the problem is shown in Fig. 4.1 using standard cylindrical coordinates. Consider a uniform DR, with the height value of (h) and radius (a), is placed on a perfect ground plane (PEC). The effect of the feed probe is temporarily ignored. Image theory is suitably applied, and the ground plane is replaced by an imaged portion of the cylinder extending to z = -h. The isolated cylinder is then analyzed with an implied boundary condition of  $E_{\rho} = 0$  and  $E_{\phi} = 0$  at z = 0. An approximate solution for the fields inside the cylindrical cavity is obtained by assuming that the surfaces are perfect magnetic conductors. This technique has been previously justified in [75]. It is shown in [66] that for such a cavity, wave functions  $TE_z$  and  $TH_z$ , can be written as:

$$\psi_{TE_{npm}} = J_n \left( \frac{X_{np}}{a} \rho \right) \begin{Bmatrix} \sin n\emptyset \\ \cos n\emptyset \end{Bmatrix} \sin \left[ \frac{(2m+1)\pi}{2h} \right] \tag{4.1}$$

$$\psi_{TM_{npm}} = J_n \left( \frac{X'_{np}}{a} \rho \right) \begin{Bmatrix} \sin n\emptyset \\ \cos n\emptyset \end{Bmatrix} \cos \left[ \frac{(2m+1)\pi z}{2h} \right]$$

(4.2)

where the mode indices n, p and m identify field variations in  $\varphi$  (azimuth), r (radial) and z (axial) directions, respectively.  $J_n$  is the Bessel function of the first kind, and  $X_{np}$  and  $X'_{np}$  are the roots of the Bessel's functions and their derivatives:

$$J_n(X_{np}) = 0$$

,  $J'_n(X'_{np}) = 0$ , for  $n = 1, 2, 3, \dots, p = 1, 2, 3, \dots, m = 0, 1, 2, 3, \dots$

The separation equation  $K_z^2 + K_\rho^2 = K^2 = \omega^2 \mu \varepsilon$ , leads to the expression that is used for calculating the resonant frequency of the *npm* mode as follows:

$$f_{npm} = \frac{1}{2\pi a \sqrt{\mu \varepsilon}} \sqrt{\begin{cases} X_{np}^2 \\ X_{np}'^2 \end{cases}} + \left[ \frac{\pi a}{2h} (2m+1) \right]^2$$

(4.3)

For the mode with smallest resonant frequency (dominant mode, TM<sub>110</sub>) n = 1, p = 1, m = 0, and  $X'_{11} = 1.841$ . For lowest order mode resonant frequency of 0.42 THz for HRS with  $\mathcal{E}_r = 11.9$ , the initial values of h and a can be obtained from (4.3).

Fig. 4.1. DR Model for modal analysis

The wave function of the dominant mode is:

$$\psi_{TM_{110}} = J_1 \left( \frac{X'_{11}}{a} \rho \right) \cos \emptyset \cos \left( \frac{2\pi}{2h} \right) \tag{4.4}$$

Far field radiation pattern associated with this mode is calculated by finding the equivalent surface currents. Surface currents are calculated from,  $\vec{M} = \vec{E} \times \hat{n}$ , using tangential electric fields which are obtained from:

$$E_{\emptyset} = \frac{1}{j\omega\varepsilon\rho} \frac{\partial^{2}\psi}{\partial\emptyset\partial z}, E_{z} = \frac{1}{j\omega\varepsilon} \left(\frac{\partial^{2}}{\partial z^{2}} + k^{2}\right) \psi, E_{\rho} = \frac{1}{j\omega\varepsilon} \frac{\partial^{2}\psi}{\partial\rho\partial z}$$

(4.5)

#### 4.2 DRA Slot Excitation

Due to the planned integration of DRA with an active source, the DRA is exited through the rectangular slot. Slot coupling is also referred to as aperture coupling in literature. By keeping the slot dimensions electrically small, the amount of radiation spilling beneath the ground plane can be minimized. Aperture coupling offers the advantage of having the feed network located below

the ground plane, isolating the radiating aperture from any unwanted coupling or spurious radiation from the feed line. The slot can be considered as an equivalent magnetic current  $(M_s)$  whose direction is parallel to the slot length. When exciting the DRA with a magnetic current source, the source (slot) should be located close to an area of strong magnetic fields inside DRA in order to achieve strong coupling  $(\chi)$ , as shown in Fig. 4.2. Based on reciprocity theorem, coupling strength is calculated by the equation:  $\chi \propto \int_{v} (H_{DRA} \cdot M_s) dV$

Fig. 4.2. Slot coupling to the magnetic field inside DRA

In [76] the method of moments has been applied to a DRA above PEC when excited through a magnetic source and provided an empirical formula to calculate resonance frequency of a cylindrical DRA in  $\text{HEM}_{11\delta}$  mode:

$$f_r = \frac{c}{2\pi a\sqrt{\varepsilon_r}} \left[ 1.71 + \frac{a}{h} + 0.1578 \left(\frac{a}{h}\right)^2 \right]$$

(4.6)

HEM<sub>118</sub> is more accurate expression of the fundamental as compared to TM<sub>110</sub> in the previous Section. It uses an accurate set of boundary conditions between dielectric and air, instead of simple PMC surfaces. The formula (4.6) is useful for quick calculation of DRA resonant frequencies.

#### 4.3 DR Modal Field Simulation

HFSS simulation is performed to verify the resonance frequencies of a cylindrical DR obtained from analytical method in Section 4.1. A cylindrical DR with a height of 100 μm and radius of 75 μm was modeled. PMC boundary condition was applied to the top and side surface of the cylinder. A PEC was assumed as the bottom surface of the DR. HFSS solver was set to find eigenmode solutions for the first 5 resonance modes. Table 4.1 shows the electric and magnetic fields of these first 5 resonance modes along with their resonance frequency. Since these not-radiating modes are similar to radiating modes, the DR dimensions obtained from this simulation are used to model the preliminary DRA structure in radiating mode.

Table 4.1. Electric and Magnetic fields for first radiating modes of cylindrical DR

| Mode                      | F<br>(GHz) | H Field Vector Plot | E Field Vector Plot |

|---------------------------|------------|---------------------|---------------------|

| 1 & 2<br>TM <sub>11</sub> | 406.8      |                     |                     |

| 2<br>TE <sub>11</sub>     | 499.2      |                     |                     |

| 3 & 4<br>HE <sub>21</sub> | 610.9      |                     |                     |

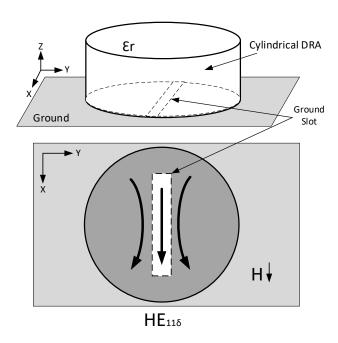

#### 4.4 DRA on PEC Plane with an Ideal Magnetic Slot Excitation

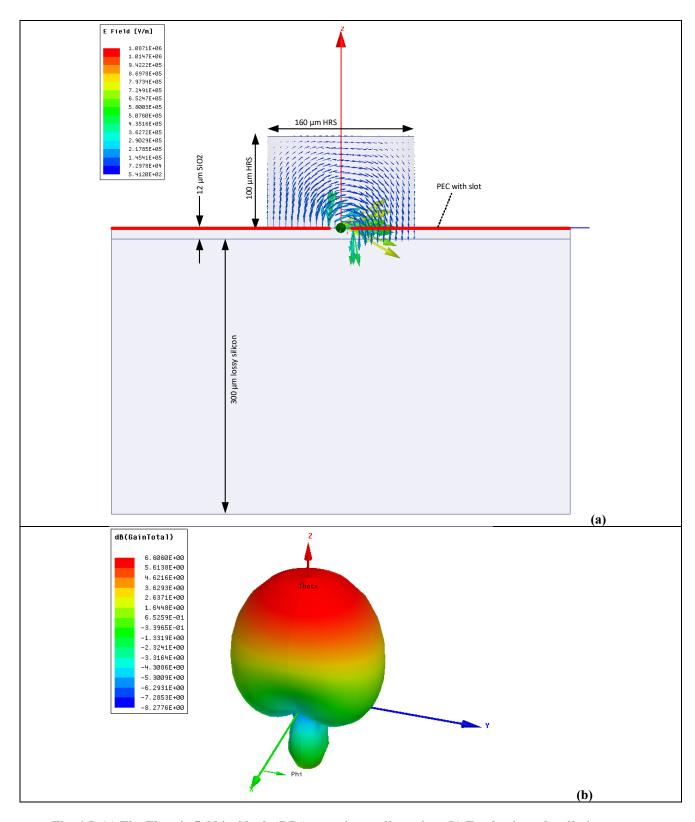

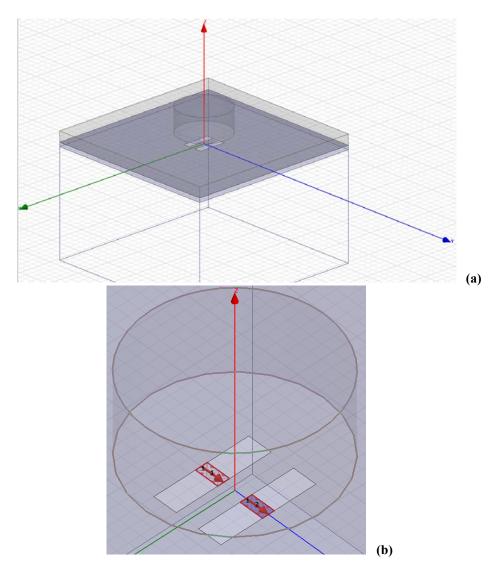

A HRS DRA with height of 100  $\mu$ m, and radius of 80  $\mu$ m is put on a PEC. The PEC contains an aperture slot as shown in Fig. 4.3. A voltage source across the slot is exciting the DRA. This structure is placed on top of a two-layer cubical structure with the size of  $300\times300\mu$ m. This cube represents an active die in TSMC65nm technology. The first top layer of the cube which is underneath the PEC, is a 12  $\mu$ m SiO2. This layer is representing all the interconnecting layers in the TSMC65nm technology with 9 metal layers and modeled as a loss-less material. The bottom layer is a 300  $\mu$ m thick conductive silicon with  $\sigma = 7$  S/m³ representing the bulk silicon of the die. The whole structure is enclosed inside a box with radiation boundaries.

Fig. 4.3. (a) A cylindrical DRA is excited through a slot on PEC. DRA and PEC are placed on a TSMC65nm die model. (b) The ground slot on the PEC is excited with a lump port across the slot.

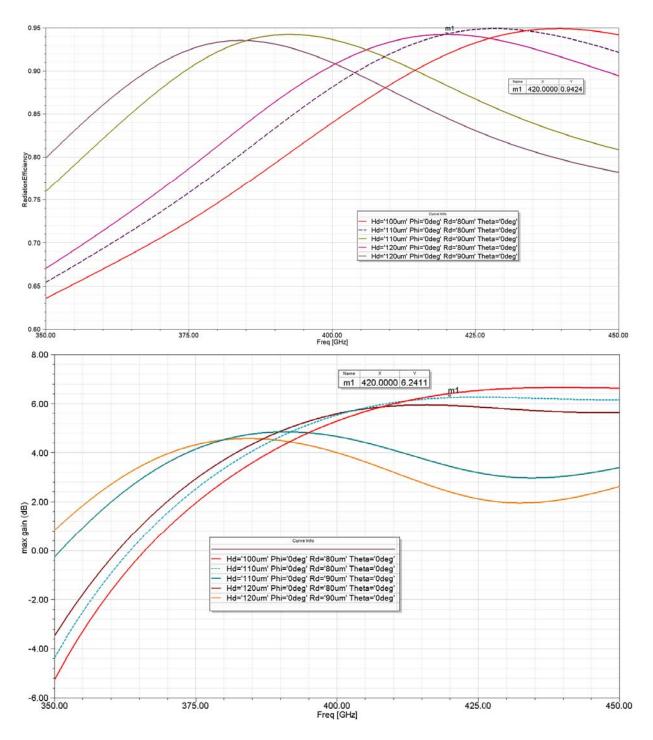

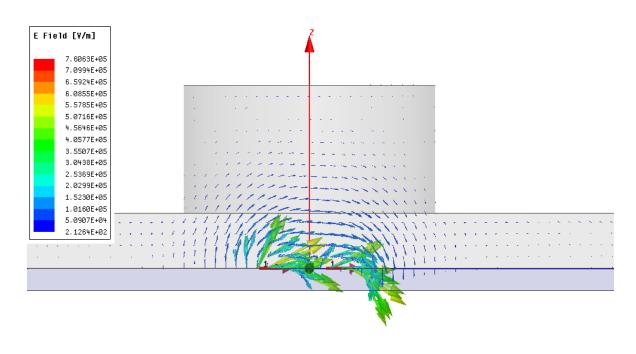

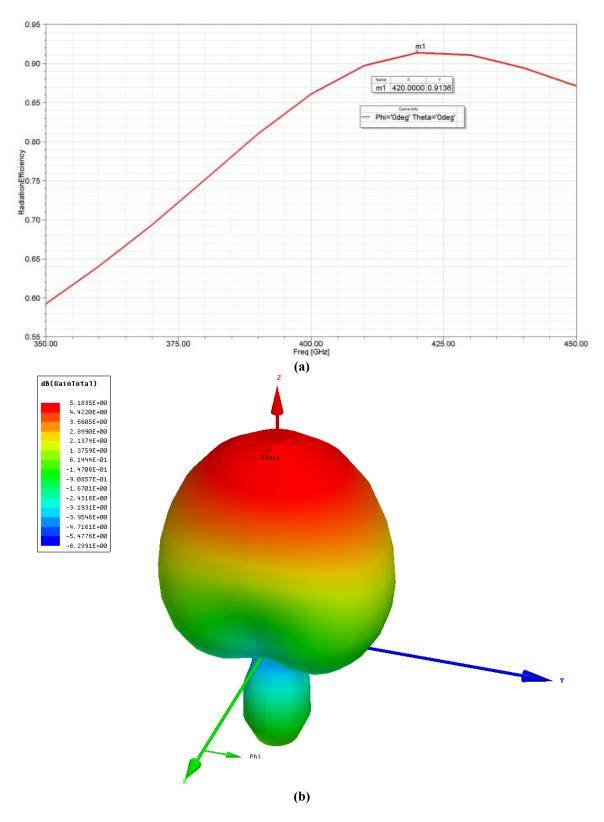

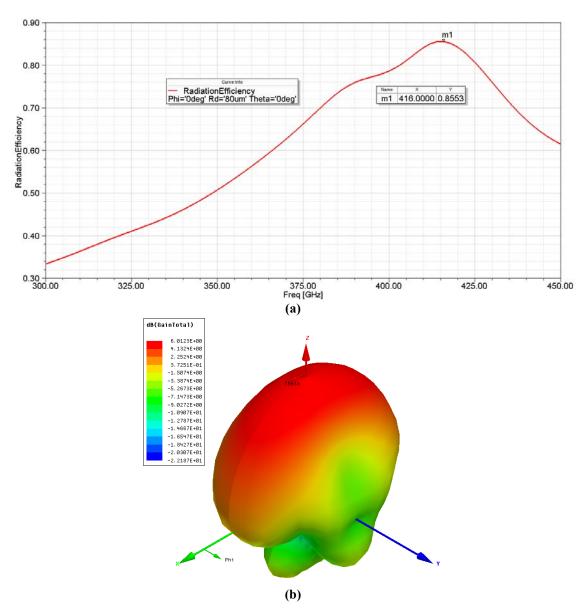

Since the perfect magnetic boundry conditions around the DRA is removed in comparism with eigenmode solutions model, height ( $H_d$ ) and diameter ( $R_d$ ) of the DRA are optimized around the values estimated in Section 4.3 to achieve maximum radiation efficiency at 420 GHz. Sweep of  $H_d$  and  $R_d$  of DRA versus radiation efficiency and maximum gain is shown in Fig. 4.4.  $H_d$  of 100  $\mu$ m and  $R_d$  of 80  $\mu$ m found to give maximum radiation efficiency of 0.94 and total maximum gain of 6.2 dB at broadside. Fig. 4.5, shows E-field and total gain pattern at these optimized

dimensions. Illustrated electric field distribution in the DRA at resonance frequency in Fig. 4.5(a), confirms the excitation of HEM11 $\delta$  radiating mode.

Fig. 4.4. Sweep of  $H_d$  and  $R_d$  of DRA.  $H_d$  at 100  $\mu$ m and  $R_d$  at 80  $\mu$ m gives maximum radiation efficiency of 0.94 and total maximum gain of 6.2 dB at broadside.

Fig. 4.5. (a) The Electric field inside the DRA at optimum dimention, (b) Total gain and radiation pattern

#### 4.5 DRA with an Attached 30 µm Silicon Slab

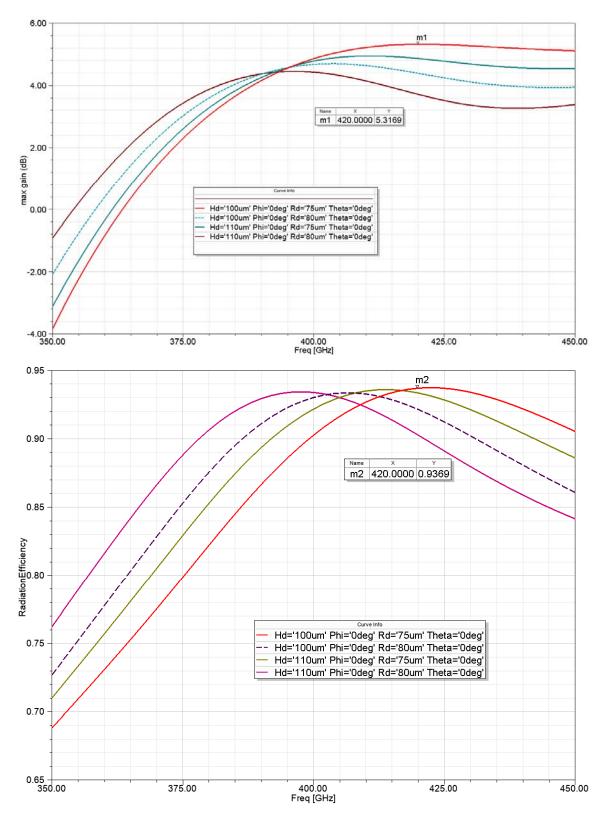

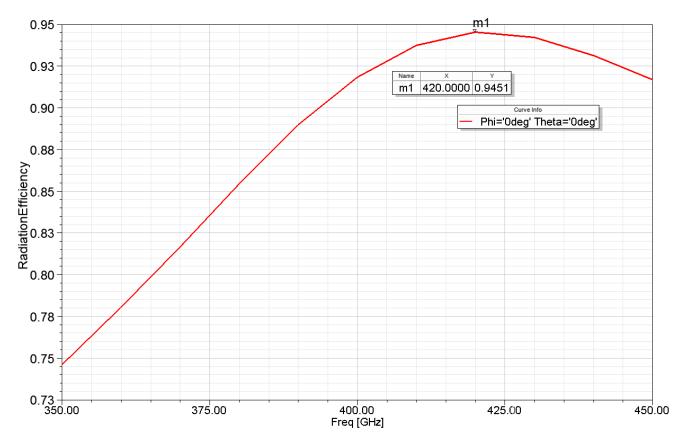

A major challenge in the integration of a DRA with an active die is placing the DRA with acceptable precision on top of the die. Additionally, in an array structure, DRAs need to be placed at a designed coordinate from each other. In order to address these two fundamental requirements, a carrier layer to arrange and fix the DRAs in specific positions is proposed and developed. This carrier layer also makes the mechanical handling of the array structure feasible. In order to study the effect of this carrier layer on the performance of the DRA, the cylindrical DRA simulation model in Section 4.4 is modified. A 30 µm thick HRS slab with the identical material as DRA is attached to the DRA bottom. The two objects, DRA and the HRS slab, are then merged. This unified structure is put on a PEC covering the top surface of an active die model. The PEC embeds an excitation slot. The active die is modeled with the same layer stack up as the previous simulation. The  $H_d$  and  $R_d$  of the DR is optimized around their initial values to achieve maximum radiation efficiency and maximum gain at 420 GHz. Fig. 4.6 shows these sweeps. DR with  $H_d$  at 100 μm and R<sub>d</sub> at 75 μm gives the maximum radiation efficiency of 0.93 and max gain of 5.3 dB at 420 GHz. The radiation efficiency of this structure compared to the stand alone DRA of Section 4.4, only decrease by 0.1. This indicates the carrier is not affecting the performance of the DRA. A closer look at the field inside the structure, as shown in Fig. 4.7 (a)(b) also indicates that the DRA field spill into the carrier slab is quite small. Fig. 4.7(c) shows directivity is reduced by 1.4 dB in compare to the model in Section 4.4.

Fig. 4.6. Sweeps of  $H_d$  and radius  $R_d$  of DRA.  $H_d$  = 100  $\mu$ m and  $R_d$  = 80  $\mu$ m gives maximum radiation efficiency of 0.94 and total maximum gain of 5.2 dB at broadside

Fig. 4.7. (a)(b) Electric field inside the DRA structure with an attached HRS carrier layer, (c) Total gain and radiation pattern

#### 4.6 DRA with Differential Excitation

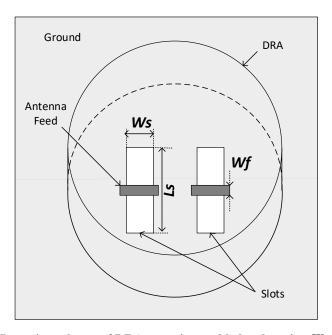

In this simulation, the DRA structure of Section 4.6 with an attached 30  $\mu$ m silicon slab is excited through two differentially driven slots. Fig. 4.8 shows this configuration. The two ports are driven with 180° phase shift and excited the same HEM118 mode inside DRA. Each slot dimension, slot width (Ws), slot length (Ls) and their separation (Ds) are optimized to obtain maximum coupling and radiation efficiency. Fig. 4.9 shows how the two differential ports contribute to excite the same HEM118 mode inside DR. Simulation shows radiation efficiency of 0.94 as shown in Fig. 4.10. This indicates the efficiency does not deteriorate in compared to the setup in Section 4.5 with single port excitation.

Fig. 4.8. (a) DRA with silicon slab excited through two ground slots, (b) Ports 1 and 2 are driven differentially with 180° phase shift

Fig. 4.9. (a) Electric field inside the DRA structure when excited with two differentially driven ground slots, (b) Total gain and radiation pattern

Fig. 4.10. Radiation efficiency of the DRA with differential port excitation

#### 4.7 Power Combining inside DRA

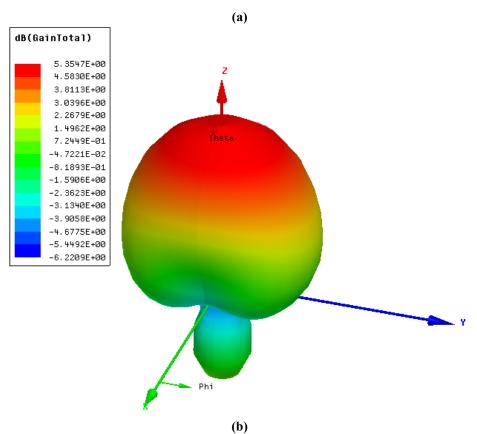

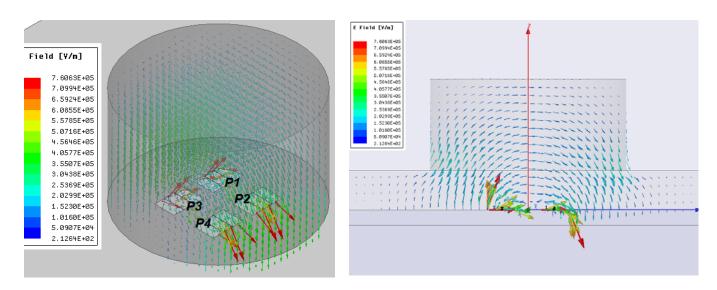

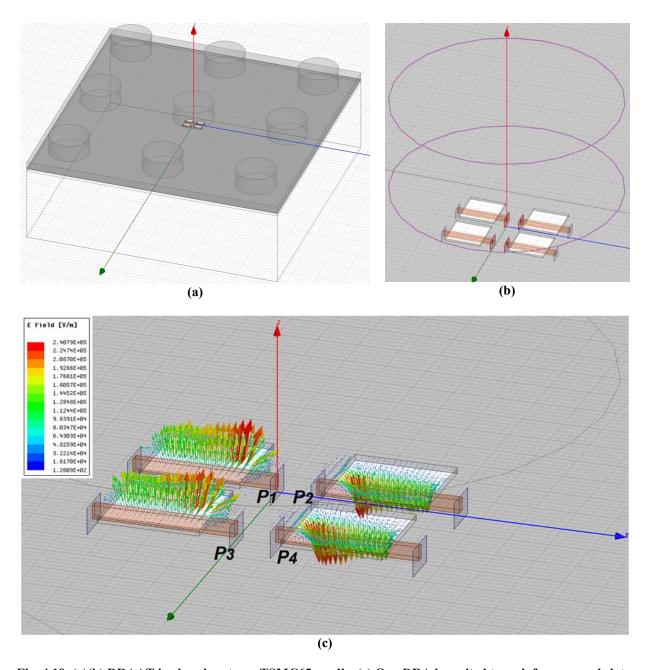

A low-loss power combiner is an essential component in any sub-THz transmitter architecture for generating a high power output signal. In my quest to obtain higher radiation power, I realized that a DRA could also work as a power comber if excited through multiple cophased ports. In this simulation setup, the same DRA structure of Section 4.5 with a 30  $\mu$ m silicon slab attachment is excited through two pairs of differentially driven slots. These two pairs are oriented alongside each other in such a way that they both excite the same HEM118 radiating mode inside DRA. As a result, the power coming from all four ground slots is combined inside the DRA. Fig. 4.11 shows this configuration. The power combining performance can be verified by checking radiation efficiency of DRA when all 4 ports are driven. As shown in Fig. 4.12, P1 and P2 are driven differentially and have 180° phases shift. P1 and P3 are co-phased similarly to P2 and P4. The four slots have identical dimensions of  $Ws \times Ls$ . Horizontal and vertical separation of the slots are optimized to obtain maximum radiation efficiency shown in Fig. 4.13.

Fig. 4.11. (a) DR with silicon slab is excited through four ground slots. (b) Two sets of differentially driven ports excite the slots and excite a single DRA

Fig. 4.12. The Electric field inside the DRA with differential ports

Fig. 4.13. (a) Radiation efficiency of a DRA excited by two differentially driven ports, (b) Total gain and radiation pattern

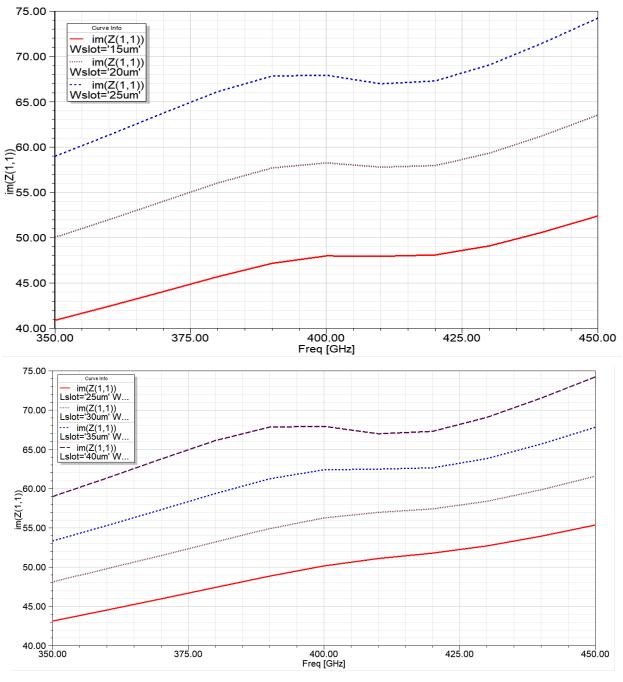

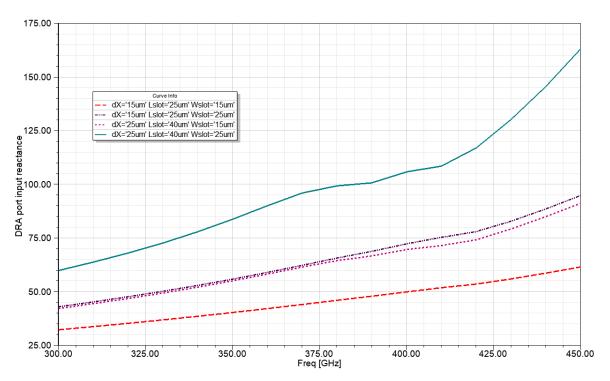

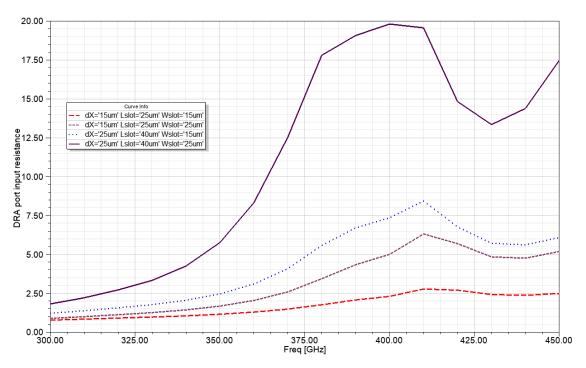

The input impedance of the input ports: P1, P2, P3 and P4 are identical. The impedance reactance part is a function of Ws, Ls. Because the four slots are positioned symmetrically with respect to the XY-axis, Ws and Ls values of each slot are limited to the circular area underneath the DRA and the X-Y separation distance between the slots. Fig. 4.14 shows the variation of input port reactance due to the Ws and Ls sizes. It is important to note that as exciting ports across the slots are ideal the port resistance remains at around 1  $\Omega$  and vary not more than 0.1  $\Omega$ .

Fig. 4.14. Variation of input port reactance with  $W_S$  and  $L_S$

#### 4.8 DRA Array Tray (DRAAT)

Antenna arrays are used to achieve higher antenna gain and narrower main beam lope. Beam steering is another application of antenna array. Normalized array factor of arrays with n identical antennas (elements) is calculated from:

$$AF(\theta,\phi) = \frac{Sin(N\Psi/2)}{N Sin(\Psi/2)}, \quad \Psi = (kd \cos \theta + \beta)$$

(4.7)

where d and  $\beta$  are the distance and phase difference between the successive elements respectively. By changing  $\beta$  electronically, beam will steer to point at different directions in space. Since the objective of this work is to achieve maxim um gain for a given array size, all the antenna elements have identical current excitations with the same amplitude and phase. Therefore,  $\beta$  is considered as 0 through-out our design. By choosing  $d = \lambda/2$ , we can obtain maximum directivity in the broad side.

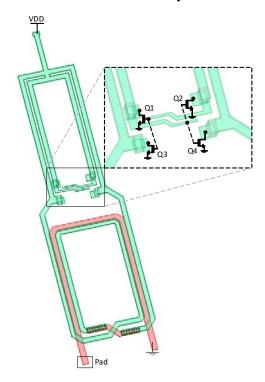

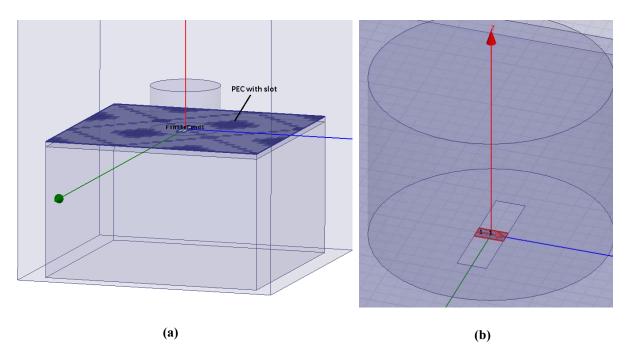

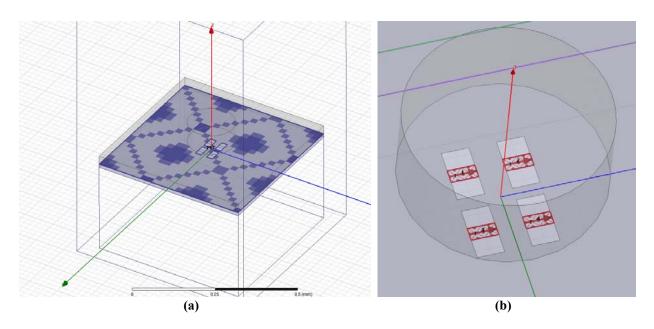

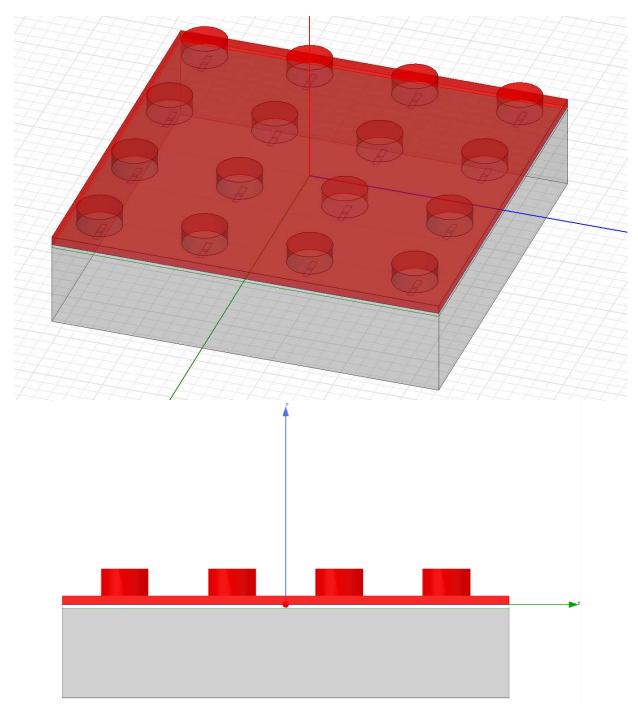

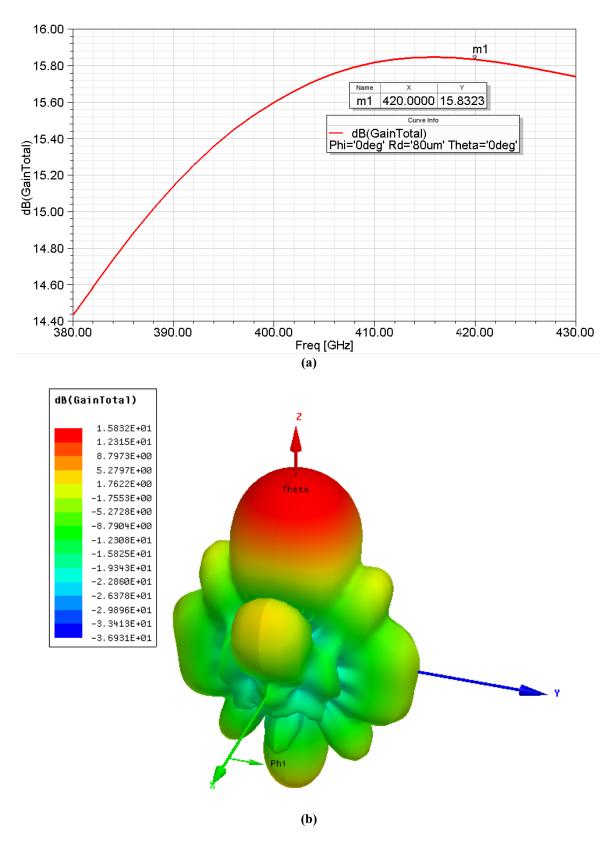

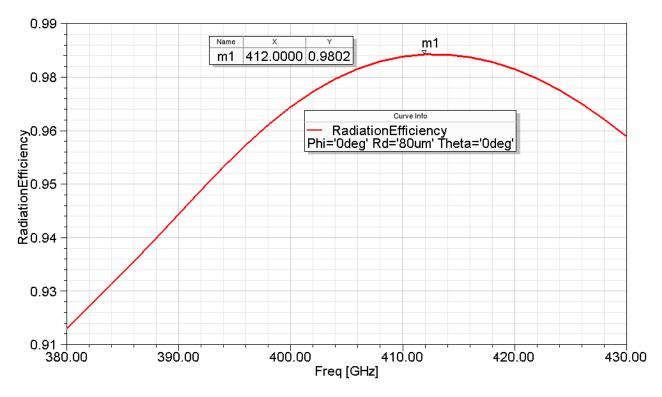

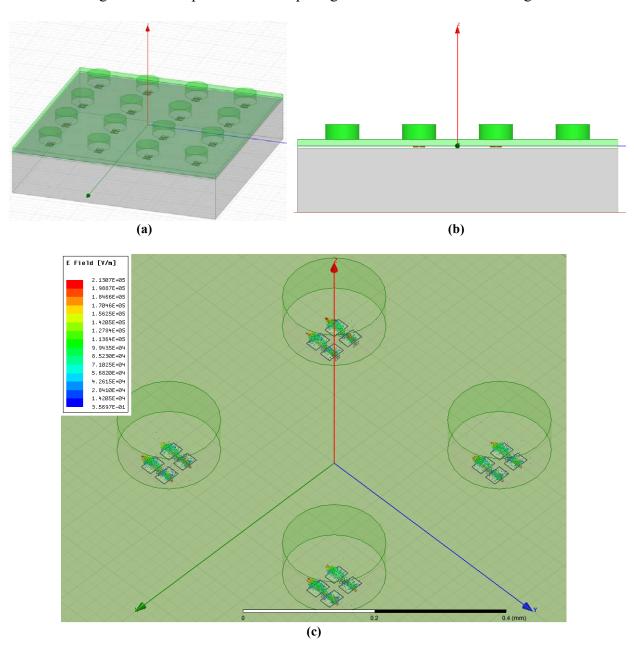

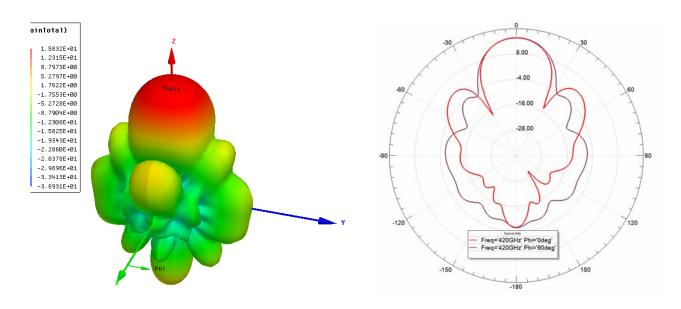

A 4×4 antenna array is investigated and developed in this work. In a simulation model, sixteen cylindrical DRAs are arranged in the form of a 4×4 array. DRAs are spaced at  $\lambda_0/2 = 360$  µm from each other. All DRAs are attached together through a 30 µm HRS carrier with the same material as DRAs. The effect of addition of this carrier layer on the performance of the DRA was described in Section 4.5. This structure of 4×4 DRAs with the attached silicon carrier is referred to as DRA Array Tray (DRAAT) is shown in Fig. 4.15. DRAAT is first simulated with each DRA is excited by a single loss-less source. This simulation would provide the reference (best) performance metrics that is required for assessing the further adjustments to the DRAAT. Each DRA is excited by a single ground slot driven by an ideal port across the slot. DRAAT shows total gain of 15.83 dB and radiation efficiency of 0.98 as shown in Fig. 4.16 and Fig. 4.17 respectively.

Fig. 4.15. The 4×4 DRAs connected through a 30  $\mu m$  silicon slab (DRAAT). DRAAT is positioned on top of a TSMC65nm die model. Each DRA is excited through an ideal port across a single ground slot

Fig. 4.16. Total gain of 4×4 DRA module with loss-less excitation. (b) Total gain pattern of array at 420 GHz

Fig. 4.17. Radiation efficiency of 4×4 DRAAT. DRAs are excited through a single loss-less ground slot

#### 4.9 DRA Excitation with Microstrip Line

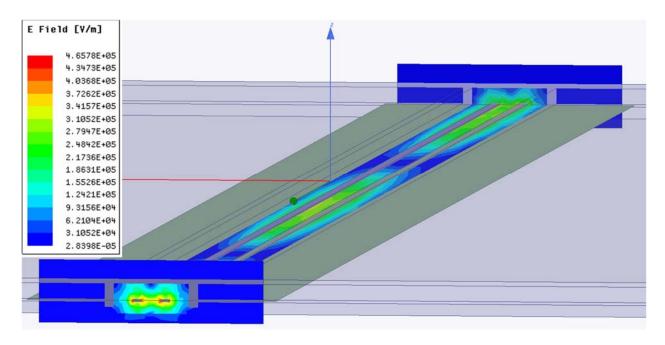

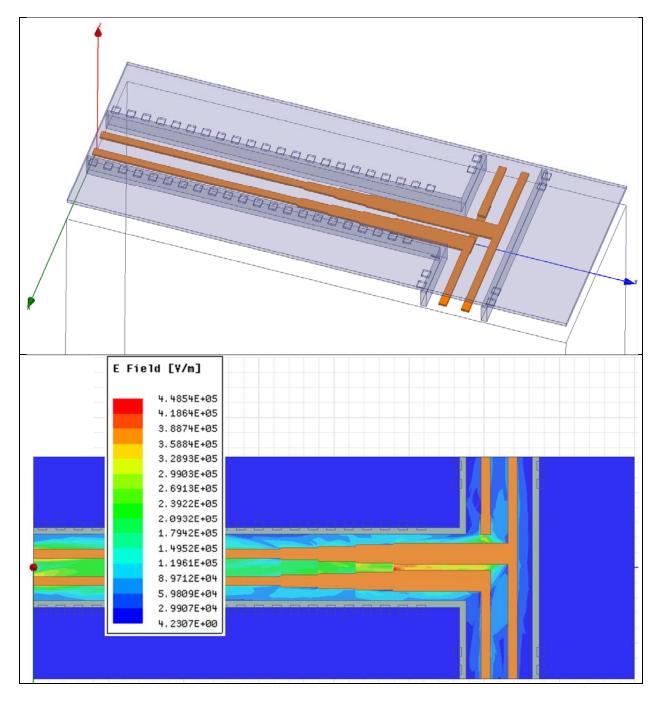

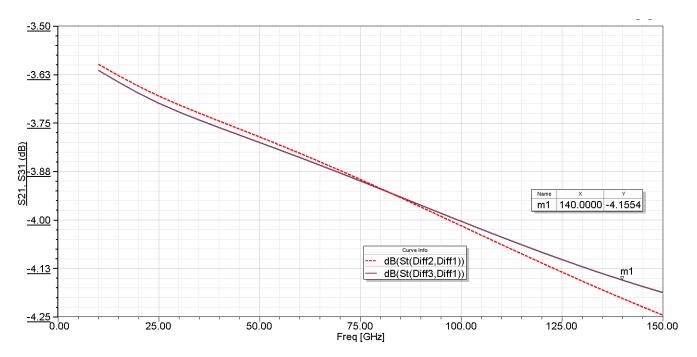

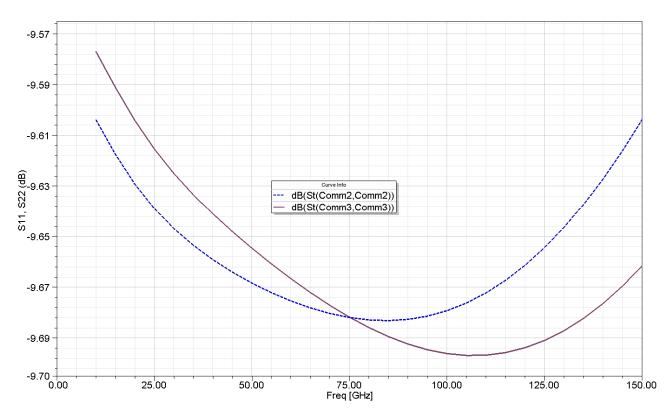

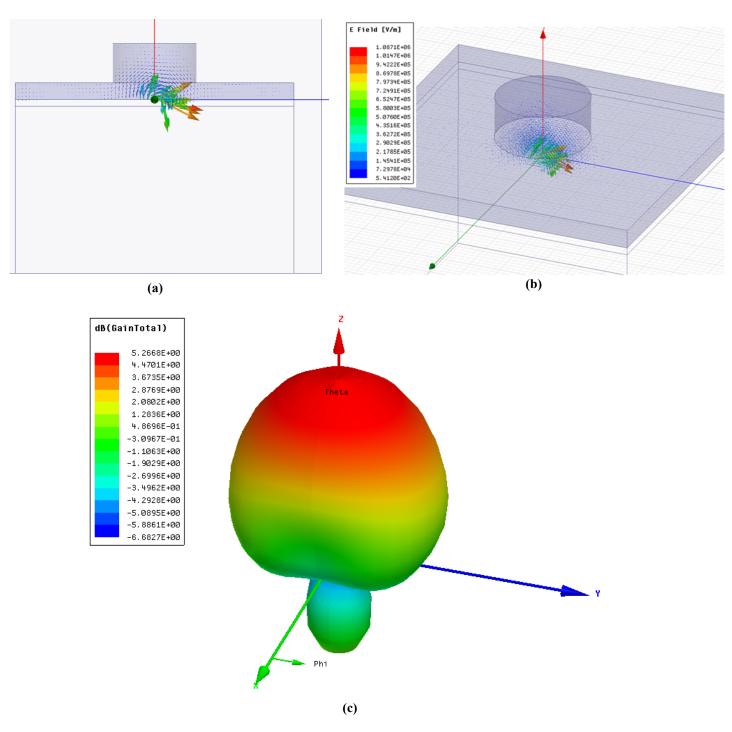

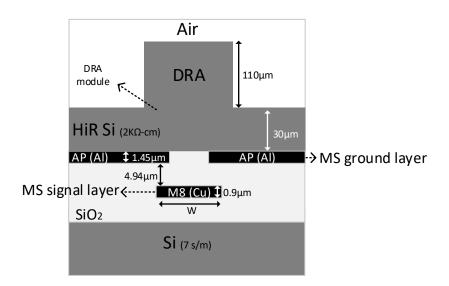

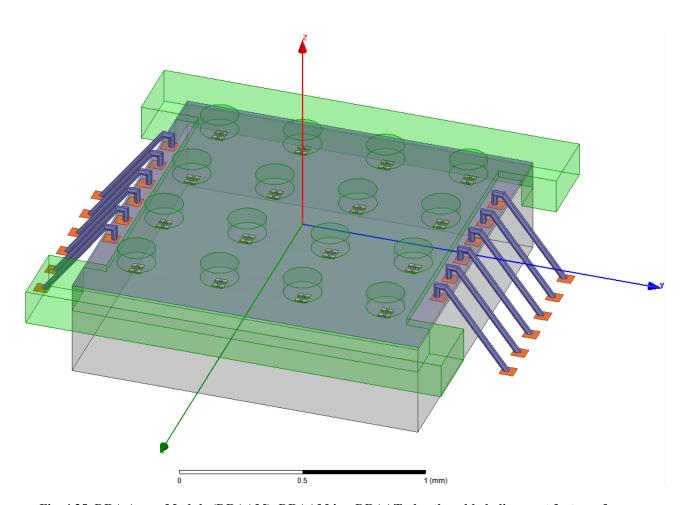

Now that we have verified the feasibility of implementing a DRA array as a separate module on top of an active die, more details of our proposed assembly scheme are added into the simulation models. In all previous simulation models, DRA was excited with ideal lump port across a ground slot. In our proposed integration scheme, the active die underneath the DRAAT excites the ground slots with a MTL implemented inside the active die. Therefore, in the following simulations, a MTL model replaces all the previous ideal ports. TSMC65nm with 9 metal layers configuration is used in this work to implement the active die. MTL vertical dimensions are determined by the metal layer stack up in TSMC65nm technology. The top metal layer of the die which is the *AP* layer is proposed to be grounded to embed the aperture slots for exciting the DRAs. For such an arrangement, an upside-down configuration for MTL is then anticipated to use the same top metal *AP* layer of the active die as the ground. *M8* is used to realize MTL signal line. Fig. 4.18 shows cross-section view of this configuration where a DRA is placed on top of a TSMC65nm die. The aforementioned configuration is used to model MTLs in a new simulation of DRAAT as shown in Fig. 4.19 (a)(b). Four MTLs underneath four ground apertures excite a single DRA.

Fig. 4.18. Implementation of antenna feed line in TSMC65nm technology. AP layer is used as MTL ground. DRA module is placed on top of active die. Ground slots in AP layer excite the DRA

Two pairs of differential lump ports drive the four MTLs. Fig. 4.19 (c) shows the E-field vectors around the MTLs aligned with the fields of  $HE_{11\delta}$  mode inside the DRA.

Fig. 4.19. (a)(b) DRAAT is placed on top a TSMC65nm die. (c) One DRA is excited trough four ground slots.

Two sets of differentially driven MTLs excite the four ground slots

With all four ports driving a DRA, radiation efficiency is at 0.85 and the gain is 6 dB, as shown in Fig. 4.20.

Fig. 4.20. (a) Radiation efficiency, (b) total radiating gain pattern of one DRA excited with differentially driven MTLs

The input impedance of the MS ports, P1, P2, P3 and P4 are identical. The impedance is a function of Ws, Ls, and the width of microstrip line. As shown in Fig. 4.21 wider and longer slots will result in higher reactance. The reactance can vary from 30 to 120  $\Omega$  which will result in an inductance of 34 to 125 pH at 420 GHz. The input resistance of the MS ports also changes as the

dimension of the slot varies. Fig. 4.22 shows the variation of the input resistance when the MS line has a fixed length at 35  $\mu$ m and width of 5  $\mu$ m. Resistance changes are from 2 to 20  $\Omega$  at 420 GHz.

Fig. 4.21. Input reactance of each of the four MS ports

Fig. 4.22. Input resistance of each of the four MS ports

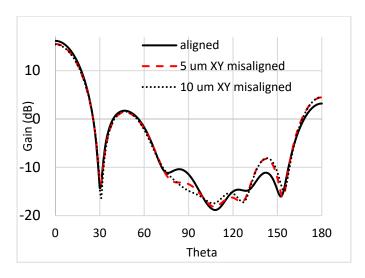

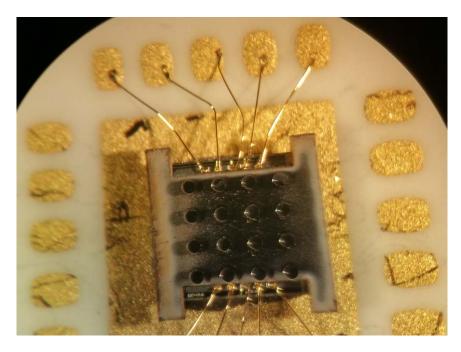

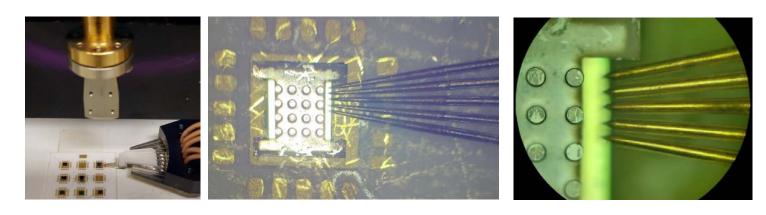

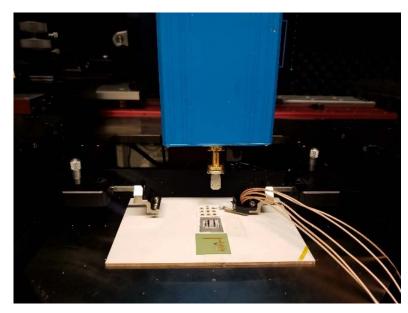

#### **4.10 4×4 DRAAT**