# Backplane Circuit Design with Amorphous Silicon Thin-Film Transistors for Flexible Displays

by

Qing Li

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2020

© Qing Li 2020

## Examining Committee Membership

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

External examiner Dr. Tse Nga (Tina) Ng

Associate Professor of Electrical and Computer Engineering

University of California at San Diego, CA, USA

Supervisor(s) Dr. Manoj Sachdev

Professor of Electrical and Computer Engineering

Dr. William S. Wong

Professor of Electrical and Computer Engineering

Internal examiner Dr. Karim S. Karim

Professor of Electrical and Computer Engineering

Internal examiner Dr. David Nairn

Associate Professor of Electrical and Computer Engineering

Internal-external examiner Dr. Yuning Li

Professor of Chemical Engineering

## **Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

In recent years, rapid advancement in LED fabrication has enabled the possibility of using GaN µLEDs to be the light media in a display panel. It has superior performance in many aspects when compared with OLED technology, such as high contrast, wide viewing angle, and low power consumption. These advantages have enabled a possibility of using µLED technology to realize flexible displays. Currently, OLEDs need high mobility low-temperature-poly-silicon (LTPS) TFTs to be the backplane driving circuit material because lower mobility TFTs are inadequate to drive OLEDs. However, LTPS TFTs have poor uniformity over a large area due to unpredictable grain sizes and require additional fabrication processes which prevent it from being integrated onto a large-area flexible platform. On the other hand, conventional amorphous silicon (a-Si:H) technology used on LCD panels have an edge in terms of uniformity over large-area and low-cost fabrication. Even though the field-effect mobility of a-Si:H TFTs is much less than LTPS technology, it is sufficient to power up µLEDs with decent pixel density, which is impossible with OLEDs. However, the nature of amorphous materials gives rise to electrical instability issues. The output current of a-Si:H TFTs gradually decreases over time under electrical stress, which results in dimmer µLEDs in pixels. Moreover, the lack of complementary p-type TFTs in a-Si:H limits the integration of driver and control circuits onto the flexible platform to realize a full "system-on-flex". To overcome such shortcomings of a-Si:H technologies, this thesis makes a contribution in providing a solution to compensate the output current degradation by a novel pixel circuit with simple control scheme, as well as bootstrapped logic circuits that can be used as row driver and control circuits on flexible substrates. The proposed compensation pixel and row driver circuits can be combined to facilitate the realization of a "system-on-flex" backplane for a display panel with a-Si:H and µLED technologies.

## Acknowledgments

I would like to express my greatest appreciation to professor Manoj Sachdev and professor William Wong for their invaluable advice and generous support to all my research activities. I would like to also thank my committee members: professor David Nairn, professor Karim Karim, professor Yuning Li and professor Tina Ng for reviewing my thesis and providing insightful suggestions during the defense.

I want to express my sincere gratitude to my colleague Dr. Czang-Ho Lee and a fellow doctoral student Mohsen Asad for working tirelessly with me on fabricating samples and debugging mistakes. The collaboration among us should always be remembered and celebrated. The help from Melissa and Maofeng at the early stage of my research is also much appreciated. During the course of the past five years, I enjoyed and learned tremendously from discussions with Bright, Mohammad, Mahdi, Govind, and Hugo.

I would like to acknowledge the administrative and technical help form Richard Barber and Phil Regier from the ECE department.

The last, but the most valuable support comes from my wife Shanshan, who has to take up the burden of keeping up the family and raising our young daughter Grace. None of my achievements would have been possible without her love, tolerance and trust. Besides, I am deeply grateful to my parents, and my parents-in-laws for their generous support and endless encouragement. Especially, my mom, who has always driven me to achieve better in whatever I do since I was a kid, sadly passed away just before the completion of my degree in the uncertain corona virus pandemic time. She will forever be remembered as a generous and encouraging parent.

## Dedication

To my mom.

## Table of Contents

| Li | List of Figures ix |                                                       |    |  |  |

|----|--------------------|-------------------------------------------------------|----|--|--|

| Li | st of              | Tables                                                | xi |  |  |

| 1  | Intr               | roduction                                             | 1  |  |  |

|    | 1.1                | A brief history of display technologies               | 1  |  |  |

|    | 1.2                | Display panel components                              | 3  |  |  |

|    | 1.3                | Comparison of light media                             | 4  |  |  |

|    | 1.4                | Comparison of backplane circuit technologies          | 6  |  |  |

|    | 1.5                | Motivations                                           | 8  |  |  |

|    | 1.6                | Thesis outline                                        | 10 |  |  |

| 2  | Bac                | kground                                               | 11 |  |  |

|    | 2.1                | Display architectures                                 | 11 |  |  |

|    |                    | 2.1.1 Passive-matrix architecture                     | 11 |  |  |

|    |                    | 2.1.2 Active-matrix architecture                      | 12 |  |  |

|    | 2.2                | TFT families for display backplane                    | 13 |  |  |

|    |                    | 2.2.1 The structure of a-Si:H TFT                     | 14 |  |  |

|    | 2.3                | Peripheral control circuits                           | 17 |  |  |

|    | 2.4                | Summary                                               | 18 |  |  |

| 3  | Pow                | ver-efficient pixel circuit                           | 19 |  |  |

|    | 3.1                | Source-anode configured conventional pixel            | 20 |  |  |

|    | 3.2                | Power-efficient pixel circuit                         | 23 |  |  |

|    | 3.3                | Realization of the drain-cathode pixel circuit        | 25 |  |  |

| 4  | Con                | npensation pixel circuits for flexible displays       | 29 |  |  |

|    | 4.1                | Introduction to compensation schemes                  | 31 |  |  |

|    |                    | 4.1.1 Conventional 2T pixel circuit                   | 31 |  |  |

|    |                    | 4.1.2 Compensation scheme - external detection        | 33 |  |  |

|    |                    | 4.1.3 Compensation scheme - reverse annealing         | 35 |  |  |

|    |                    | 4.1.4 Compensation scheme - internal detection        | 37 |  |  |

|    |                    | 4.1.5 Compensation scheme - charge transfer           | 38 |  |  |

|    | 4.2                | The proposed 6T pixel circuit and compensation method | 40 |  |  |

|    |                    | 4.2.1 Circuit operation                               | 40 |  |  |

|    |                    | 4.2.2 Circuit simulation                              | 18 |  |  |

|              |                        | 4.2.3 Fabrication and measurement results                       | 56  |

|--------------|------------------------|-----------------------------------------------------------------|-----|

|              |                        | 4.2.4 Characterization of TFT stability under bending           | 56  |

|              |                        | 4.2.5 Measurement results of the 6T pixel circuit               | 58  |

|              |                        | 4.2.6 Analysis of the lifetime and overlap capacitance          | 61  |

|              | 4.3                    | Comparison of pixel circuits                                    | 65  |

|              |                        | 4.3.1 Comparison between charge-transfer pixel circuits         | 65  |

|              |                        | 4.3.2 Comparison of existing compensation pixel circuits        | 67  |

|              | 4.4                    | Summary                                                         | 68  |

| 5            | $\mathbf{C}\mathbf{M}$ | OS-like logic circuits for flexible displays                    | 70  |

|              | 5.1                    | Introduction to TFT logic gates                                 | 72  |

|              |                        | 5.1.1 Conventional unipolar logic gates                         | 72  |

|              |                        | 5.1.2 Prior solution - 4-TFT inverter                           | 73  |

|              |                        | 5.1.3 Prior solution - 7-TFT and 1-capacitor inverter           | 74  |

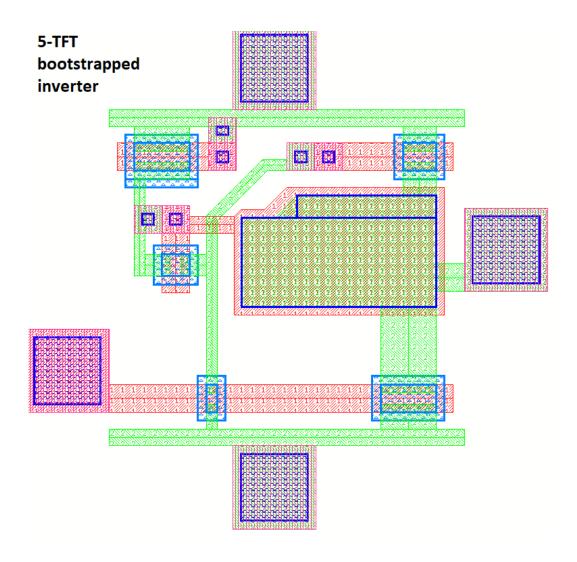

|              | 5.2                    | Bootstrapped logic gates                                        | 75  |

|              |                        | 5.2.1 Mathematical analysis of the feedback loop                | 76  |

|              |                        | 5.2.2 Simulation of the bootstrapped 7T inverter                | 80  |

|              | 5.3                    | Multi-stage logic circuits with bootstrapped gates              | 83  |

|              |                        | 5.3.1 Design and simulation of a 1-to-2 decoder                 | 83  |

|              |                        | 5.3.2 The impact of the $\Delta V_T$ degradation of a-Si:H TFTs | 85  |

|              |                        | 5.3.3 Impact of applied mechanical strain                       | 86  |

|              |                        | 5.3.4 Fabrication and experimental results                      | 88  |

|              | 5.4                    | Area-efficient bootstrapped logic gates                         | 92  |

|              |                        | 5.4.1 When input switches from ground to $V_{DD}$ :             | 93  |

|              |                        | 5.4.2 When input switches from $V_{DD}$ to ground:              | 94  |

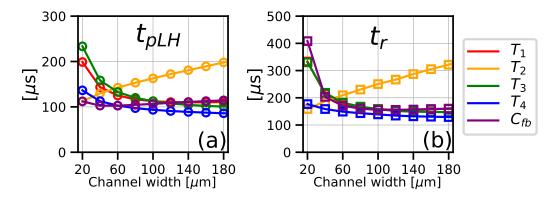

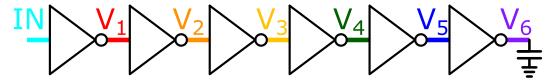

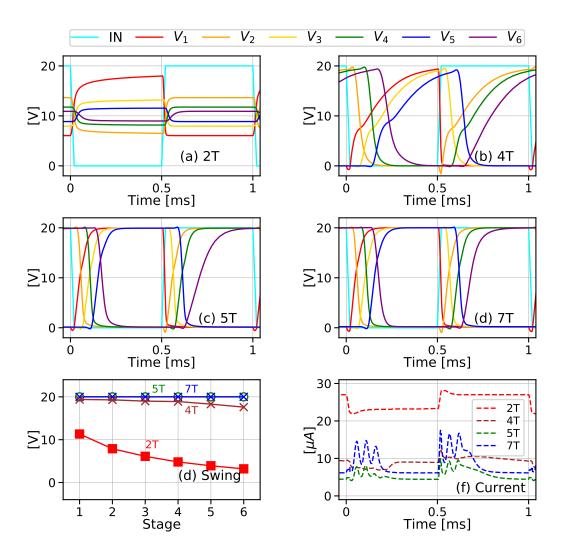

|              |                        | 5.4.3 Comparison of 2T, 4T, 5T and 7T inverters                 | 96  |

|              |                        | 5.4.4 Fabrication and measurement results of logic gates        | 97  |

|              | 5.5                    | Multi-stage logic circuit demonstration                         | 99  |

|              | 5.6                    | Comparison of TFT logic circuits                                | 101 |

|              | 5.7                    | Realization of a flexible display backplane                     | 102 |

|              |                        | 5.7.1 Row decoder + 2T pixel array                              | 103 |

|              |                        | 5.7.2 Row decoders + 6T pixel array                             | 105 |

|              | 5.8                    | Summary                                                         | 107 |

| 6            | Cor                    | nclusions and Future Work                                       | 108 |

|              | 6.1                    | Conclusions                                                     | 108 |

|              | 6.2                    | Future work                                                     | 109 |

|              | 6.3                    | Contributions                                                   | 110 |

| R            | efere                  | nces                                                            | 112 |

| $\mathbf{A}$ | ppen                   | dices                                                           | 124 |

## List of Figures

| 1.1<br>1.2<br>1.3<br>1.4                                    | Evolution of the display technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2<br>4<br>5<br>9                                                     |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                      | Backplane circuit example of an LCD display panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12<br>13<br>15<br>15<br>16<br>17                                     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | The conventional 2T pixel circuit with timing-control signals The single-transfer laser-lift-off process and integration steps Micro-graphs and transient behavior of the conventional pixel circuit. The schematic of the conventional and proposed pixel circuits Simulated transient current comparison of pixel circuits                                                                                                                                                                                                                                                                                                                                                                                                            | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>26<br>27                   |

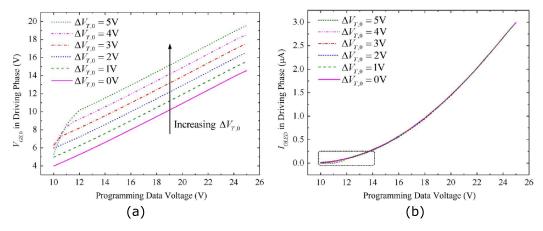

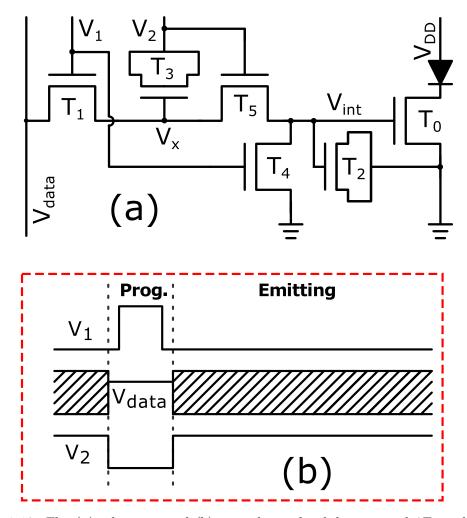

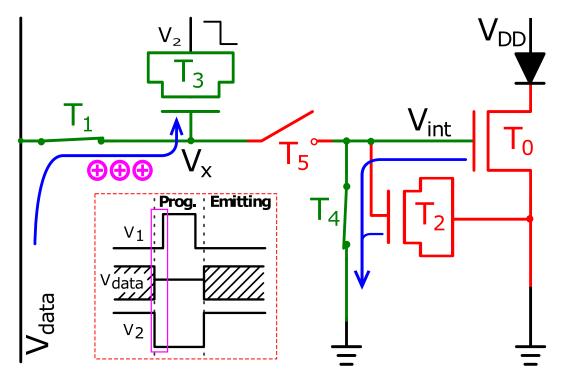

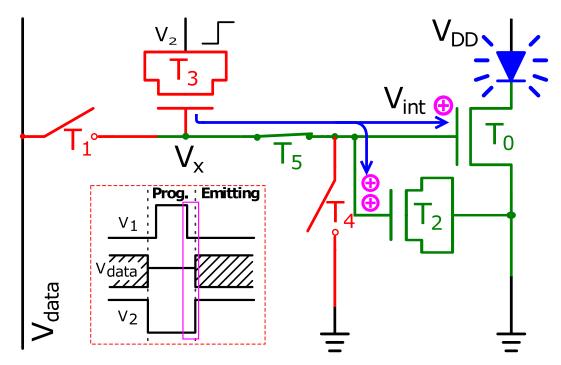

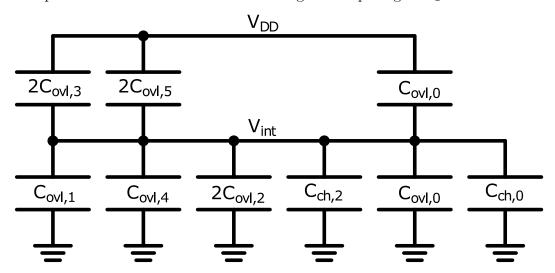

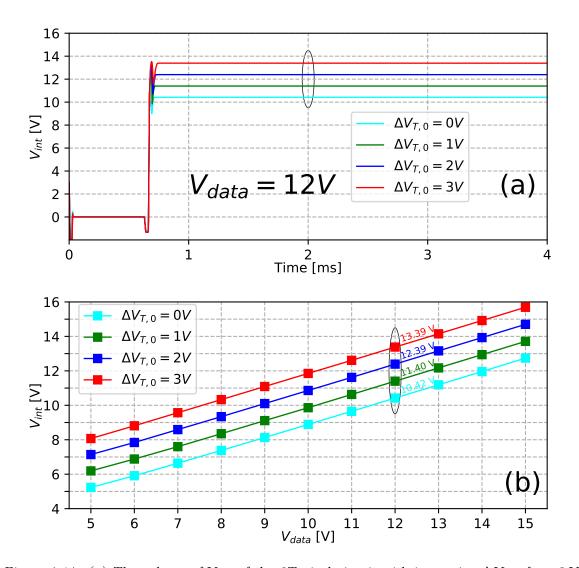

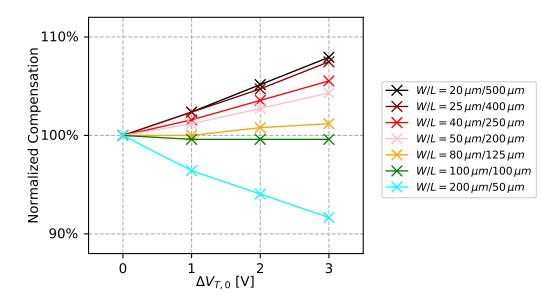

| 4.13                                                        | The schematic and control signals of the conventional 2T pixel circuit. An example of $I_{DS}$ degradation under constant voltage-bias over-time. External compensation method using a $3T+1C$ pixel circuit. Reverse annealing compensation method using a $6T+1C$ pixel circuit. Compensation performance by the reverse annealing method The schematic and control signals of the $5T+1C$ pixel circuit. Node A voltage and output current performance of the $5T+1C$ pixel. The schematic and timing-control signals of the $4T$ pixel Voltage of $V_{GS,0}$ and output current performance of the $4T$ pixel The schematic and control signals of the proposed $6T$ pixel circuit. The programming phase of the $6T$ pixel circuit | 31<br>32<br>33<br>35<br>36<br>37<br>38<br>39<br>41<br>42<br>43<br>45 |

|                                                             | Voltage at $V_{int}$ of the 6T pixel circuit with increasing $\Delta V_T$ Summary of output current for all $V_{data}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50<br>51                                                             |

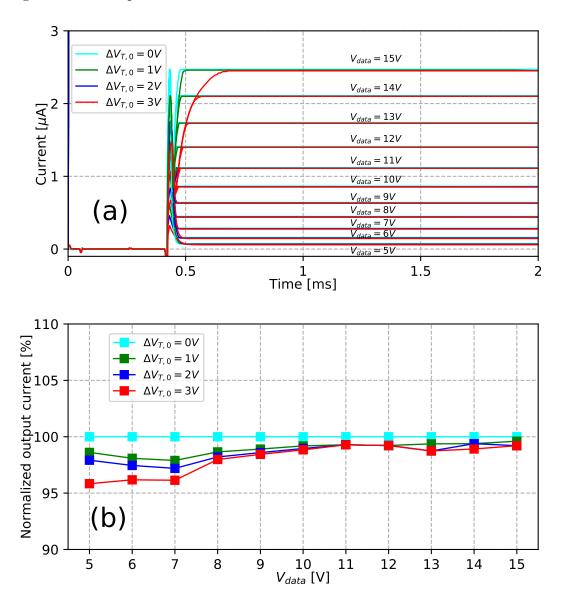

| 4.16 | Normalized compensation with various geometries of $T_2$                  | 53  |

|------|---------------------------------------------------------------------------|-----|

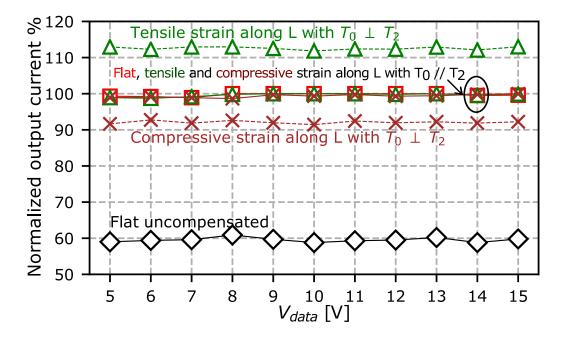

| 4.17 | Output current simulation under bending in the $V_{data}$ range           | 55  |

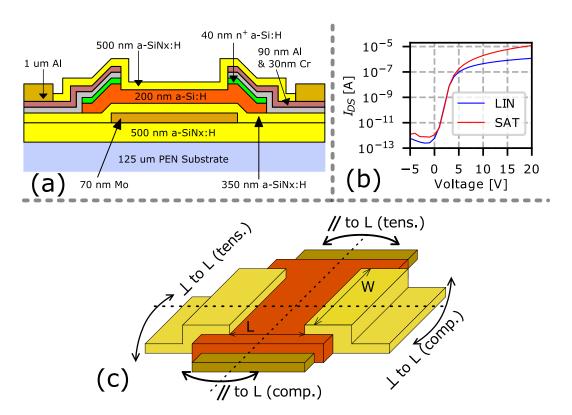

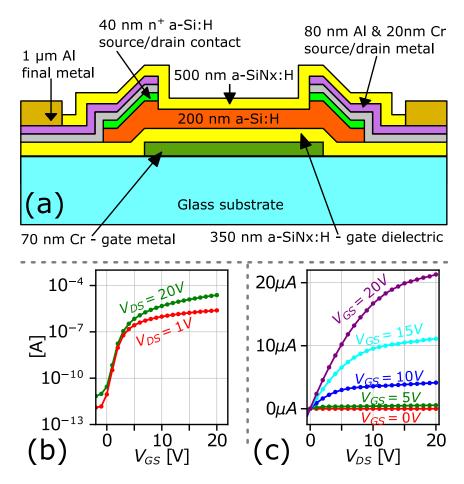

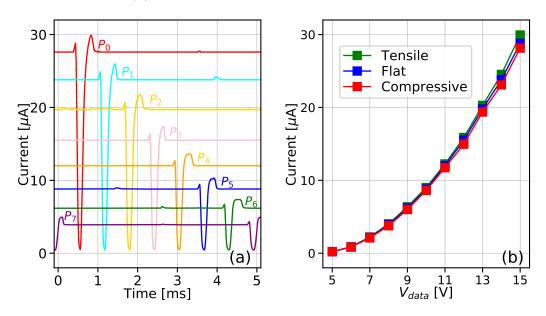

|      | TFT cross-section schematic and I-V curves                                | 57  |

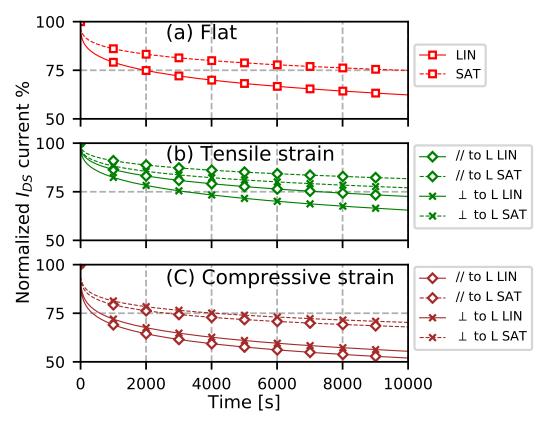

| 4.19 | Normalized current of single TFT under bending with electrical stress.    | 58  |

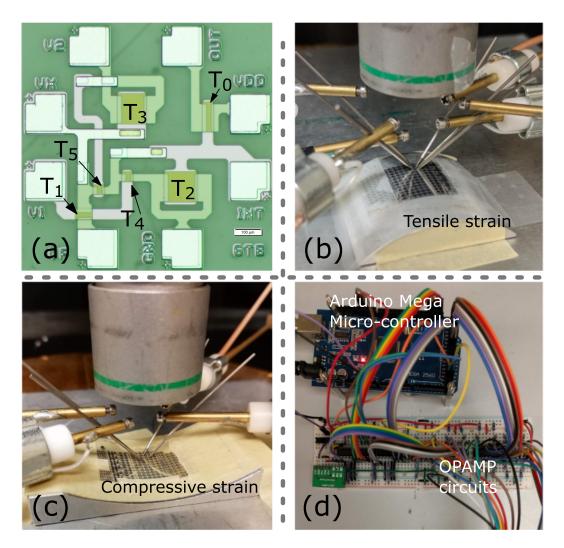

| 4.20 | 6T pixel circuit micro-graph and test setup                               | 59  |

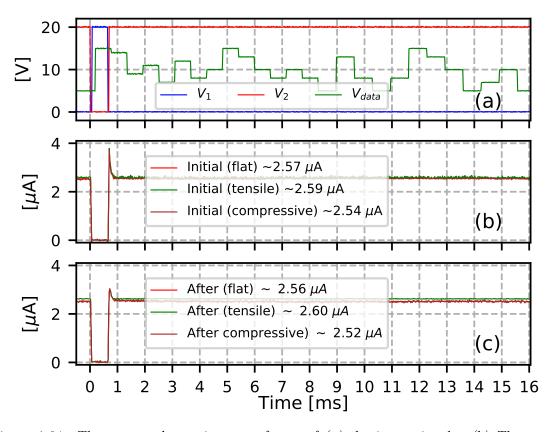

| 4.21 | Measured transient waveforms under bending                                | 60  |

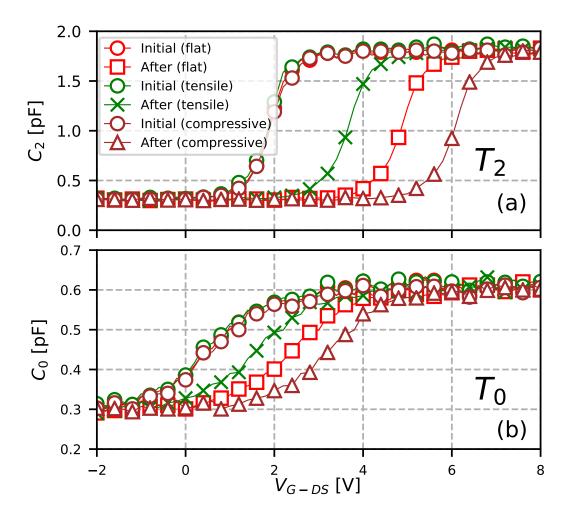

| 4.22 | Measured C-V curves for $T_0$ and $T_2$                                   | 62  |

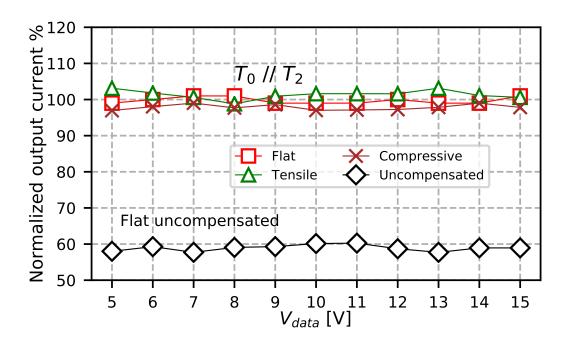

|      | Normalized current comparison between 6T and 2T pixel circuits            | 63  |

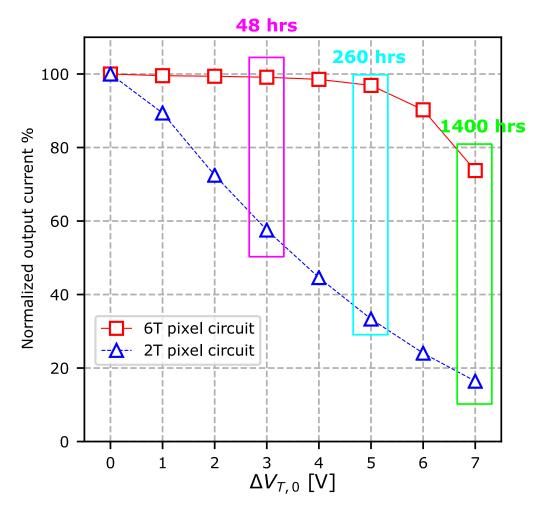

| 4.24 | Normalized current comparison with increasing $\Delta V_T$                | 64  |

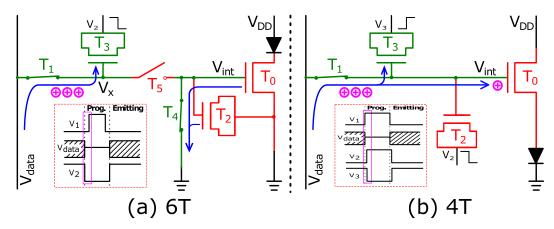

| 4.25 | 6T and 4T pixel circuits comparison in programming phase                  | 66  |

| 5.1  | The row driver and bonding pads of a conventional TFT LCD panel.          | 71  |

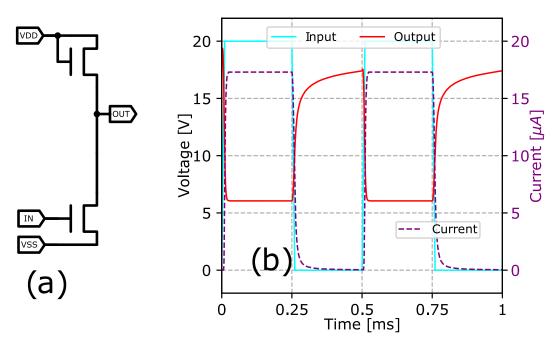

| 5.2  | The schematic and transient response of conventional 2T inverter          | 72  |

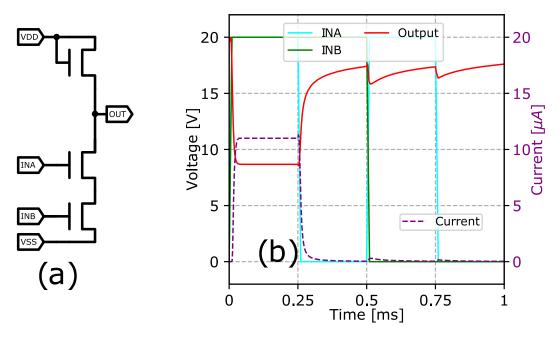

| 5.3  | The schematic and transient response of conventional 3T NAND              | 73  |

| 5.4  | The schematic and transient response of 4T inverter                       | 74  |

| 5.5  | The schematics of the 7T+1C inverter                                      | 75  |

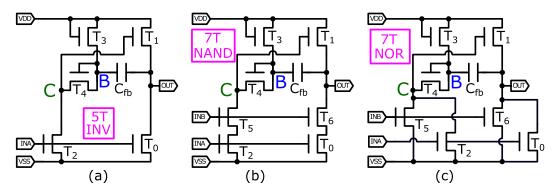

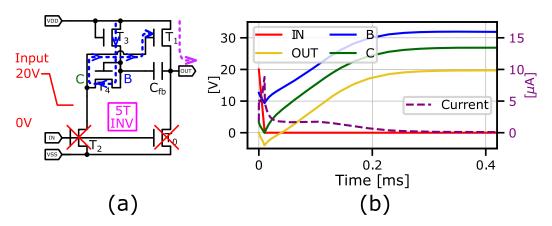

| 5.6  | The schematics of bootstrapped logic gates                                | 76  |

| 5.7  | Steady-state internal nodal voltages of during pull-down                  | 77  |

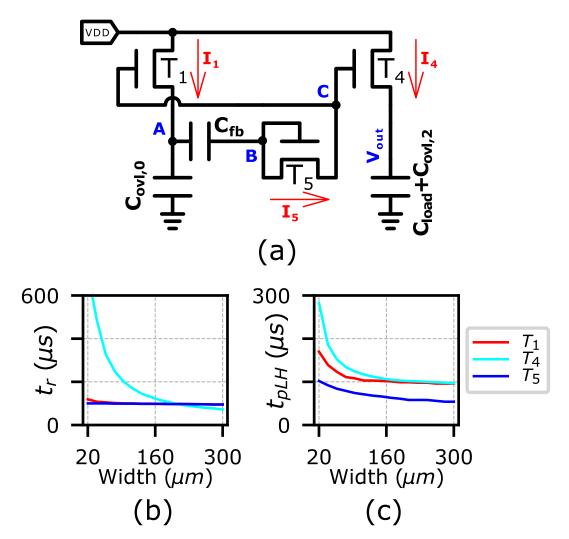

| 5.8  | The feedback network, $t_r$ and $t_f$ comparison of the 7T inverter       | 78  |

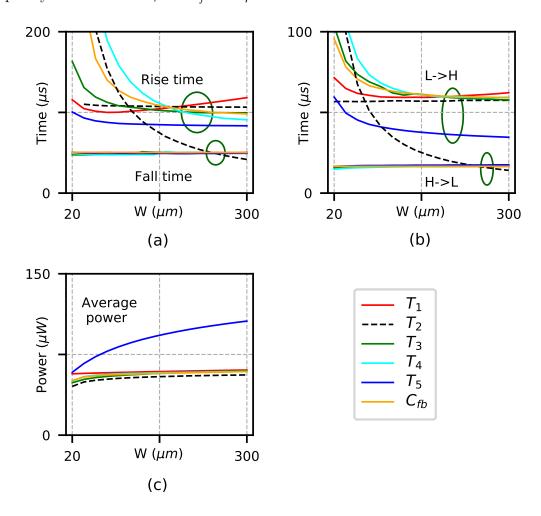

| 5.9  | The impact of TFT size variation on 7T inverter transient properties.     | 81  |

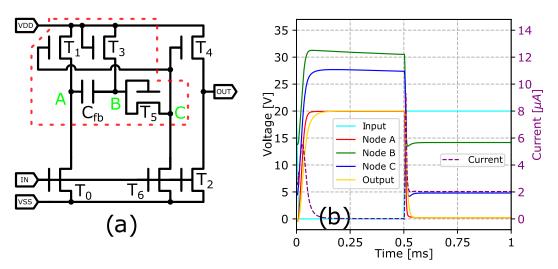

| 5.10 | The transient simulation of the 7T inverter                               | 82  |

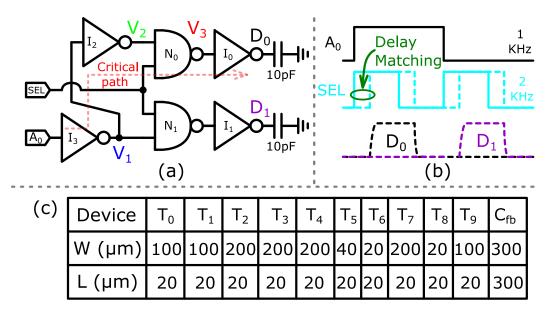

| 5.11 | The schematic of a 1-to-2 decoder, $I/O$ waveforms and device sizing      | 84  |

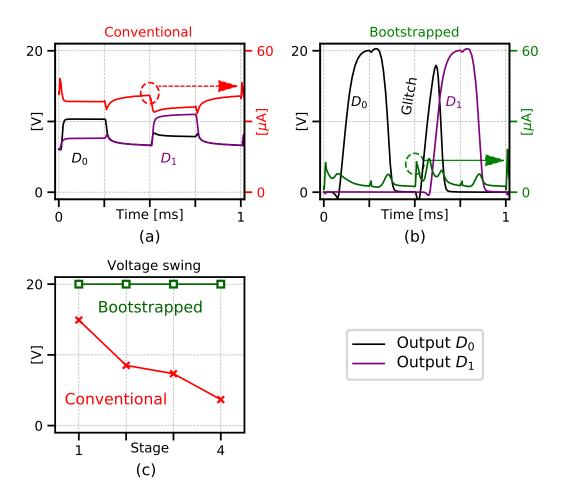

| 5.12 | Transient simulation of the 2T and 7T inverters                           | 85  |

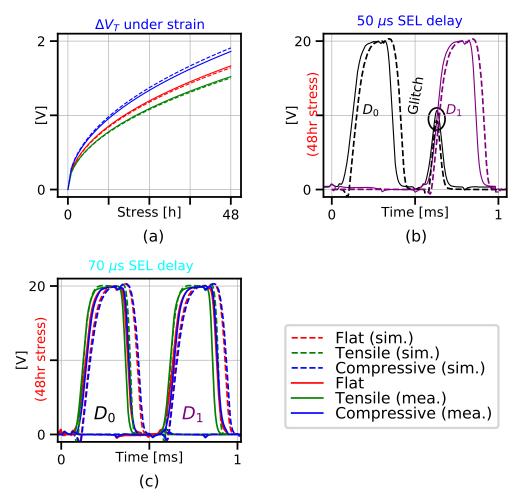

| 5.13 | Simulated glitch levels and output waveforms with increasing SEL delay.   | 87  |

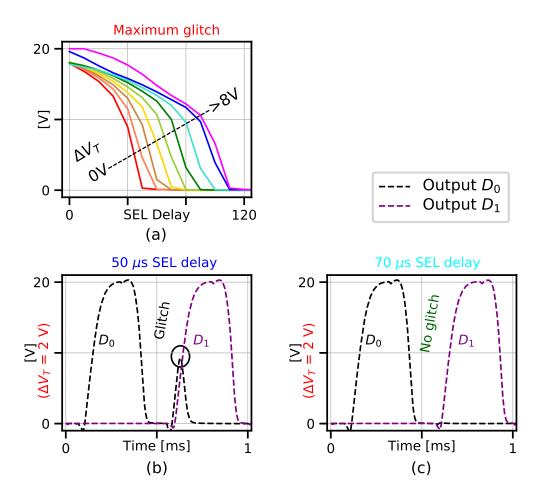

| 5.14 | Simulated output waveform of the decoder under bending                    | 88  |

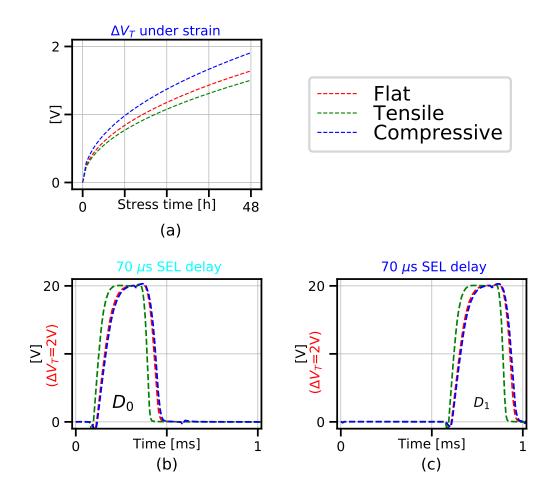

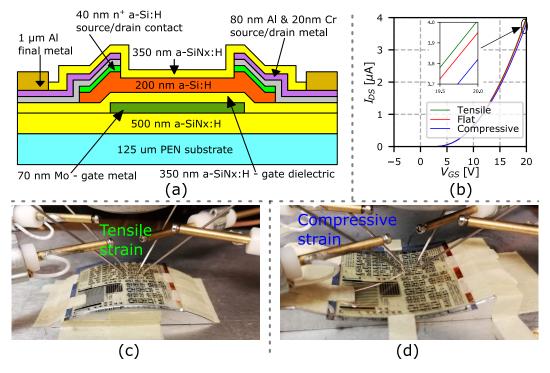

| 5.15 | The cross-section, and I-V curves of a TFT under bending                  | 89  |

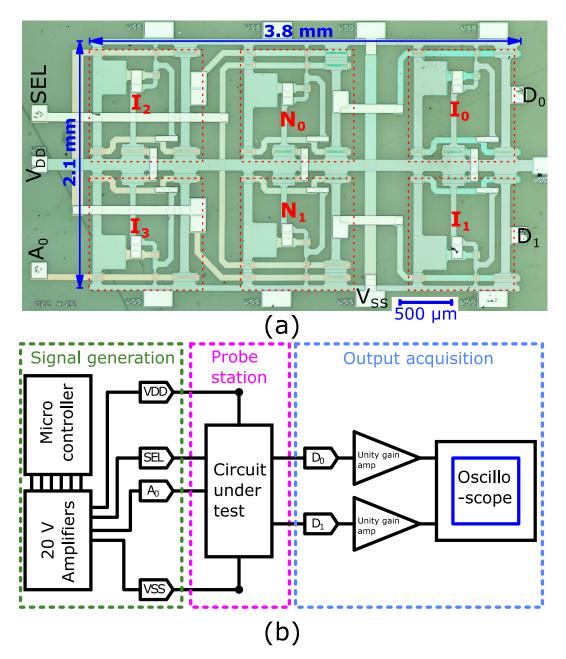

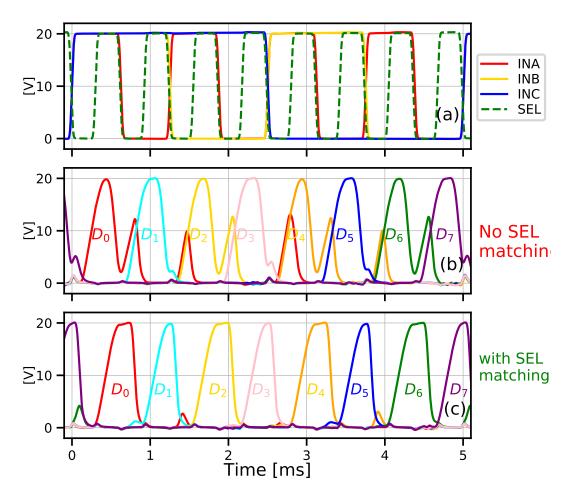

| 5.16 | The mocro-graph and the testbench of the decoder                          | 91  |

| 5.17 | Measured $\Delta V_T$ and output waveforms under bending                  | 92  |

| 5.18 | The schematic of conventional and proposed logic gates                    | 93  |

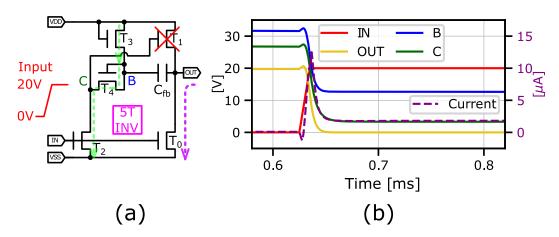

| 5.19 | The transient behavior of the 5T inverter with high input                 | 94  |

| 5.20 | The transient behavior of the 5T inverter with low input                  | 95  |

| 5.21 | The impact of individual TFTs in the feedback loop                        | 96  |

|      | A six-inverter buffer chain                                               | 96  |

| 5.23 | The transient behavior of the 2T, 4T, 5T and 7T inverter chains           | 98  |

| 5.24 | Fabricated layers and I-V performance of TFTs on glass substrate          | 99  |

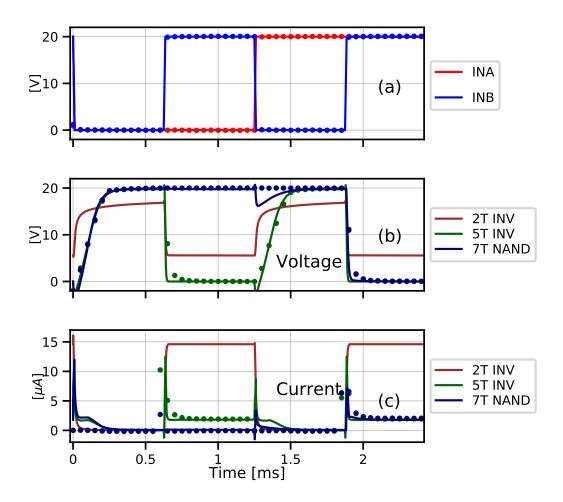

| 5.25 | Overlaid simulation and measurement results of the logic gates 1          | 100 |

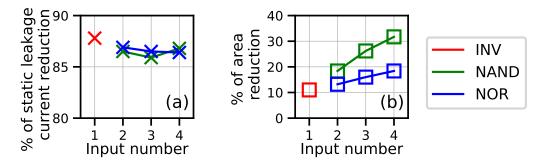

| 5.26 | Normalized static leakage current and area reduction of proposed gates. 1 | 100 |

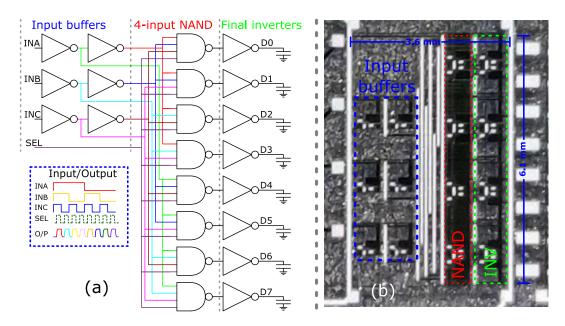

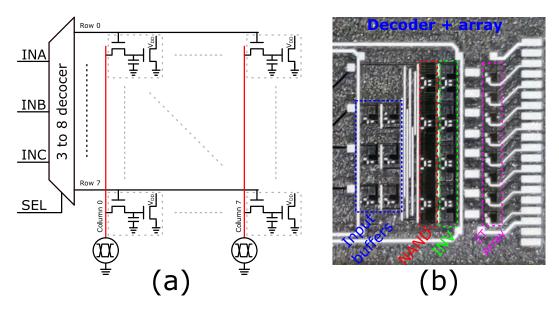

| 5.27 | The schematic and micro-graph of the 3-to-8 decoder                       | 101 |

| 5.28 | Measurement results of the 3-to-8 decoder                                 | 102 |

| 5.29 | Schematic and micro-graph of a decoder + 2T pixel array                   | 104 |

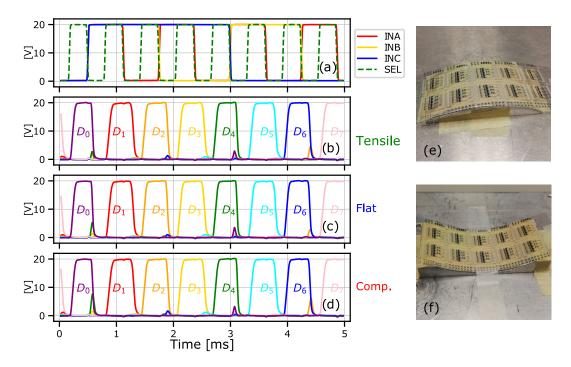

| 5.30 | Measurement results of the 3-to-8 decoder under bending 1                 | 104 |

| 5.31 | Measurement results of the 3-to-8 decoder with 2T pixels                  | 105 |

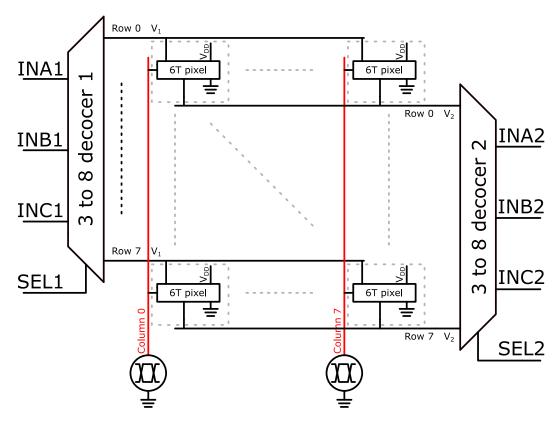

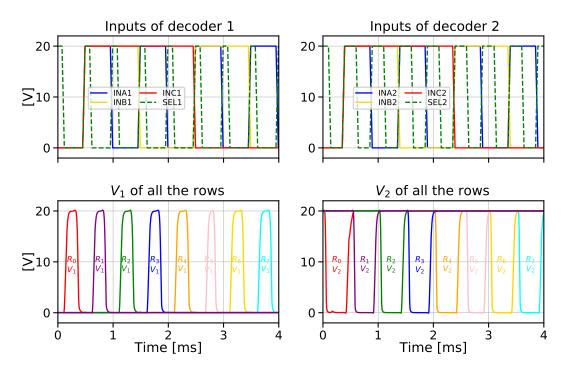

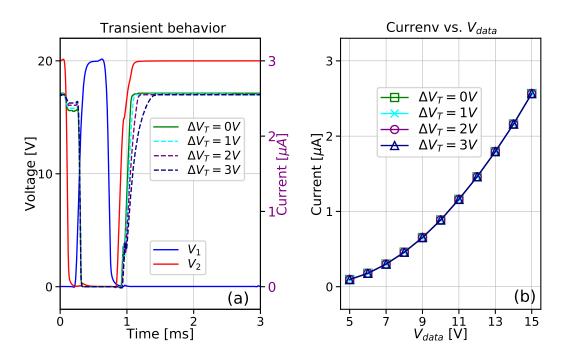

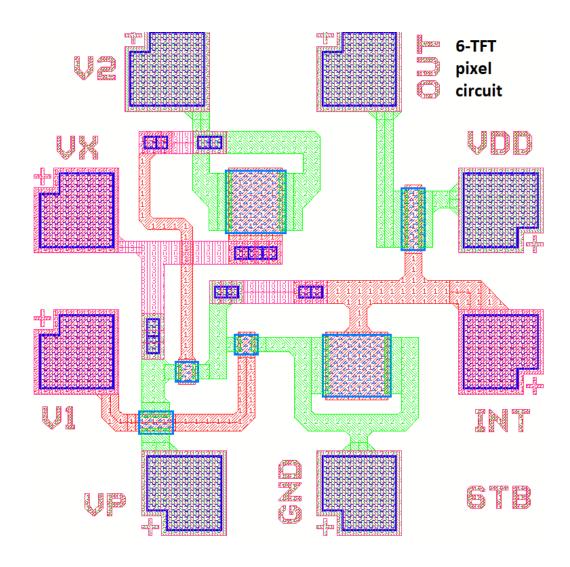

| 5.32 | Schematic of decoders driving 6T pixel array                              | 106 |

| 5.33 | Simulated results of two 3-to-8 decoders for 6T pixels                    | 106 |

| 5.34 | Simulated output current results of 6T pixel array                        | 07  |

## List of Tables

| 1.1 | Comparison of light media                                                        | 6   |

|-----|----------------------------------------------------------------------------------|-----|

| 1.2 | Comparison of backplane technologies                                             | 7   |

| 4.1 | Device and process parameters used in the simulation                             | 49  |

| 4.2 | Comparison of compensation with different geometries of $T_2$                    | 52  |

| 4.3 | Summary of $\Delta V_{T,2}$ and $\Delta V_{T,0}$ under various stress conditions | 61  |

| 4.4 | Comparison of a-Si:H compensation pixel circuits                                 | 68  |

| 5.1 | Device geometries of the 5T inverter                                             | 96  |

| 5.2 | Comparison of logic circuits with thin-film transistors                          | 103 |

## Chapter 1

### Introduction

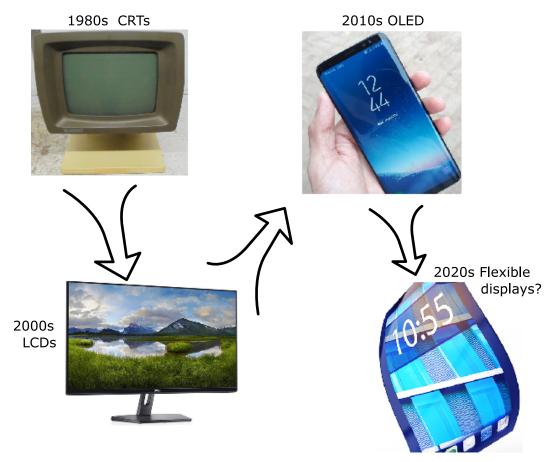

#### 1.1 A brief history of display technologies

Display technologies have come a long way since the inception of monochrome cathode-ray-tubes (CRTs) in the late 1890s [1]. The idea of CRTs is relatively simple. It operates on the principle that electrons, when fired at a high speed onto a screen coated with fluorescent materials can produce light. By changing the voltage, and subsequently the amount of electrons and their positions, it became possible to realize complex patterns. For a long period of time, CRTs were only used in laboratory environment. However in early 1900s, early development has explored the commercial viability of CRTs. With a tremendous amount of efforts, the first television came to the market in 1923. Even though its images were monochrome, blurry and slow, it still captured humanity's fascination of images.

However, people were not satisfied by monochrome images moving on their screens. The world of CRTs continued to evolve, and in the 1950s the first tri-color (red, green, and blue, i.e. RGB) CRT was shown to the market. Then, it enjoyed a successful commercial longevity all the way into the 1980s.

While CRTs were being purchased for every living room in ordinary families, the industry did not pause its pace. In the 1960s, the first light-emitting diodes (LEDs) were invented as well as plasma displays and liquid-crystal displays (LCDs). The first

LCD displays were only used in simple devices such as calculators and watches due to fabrication limitations [2].

The next revolution in the world of display technology was triggered by the arrival of personal computers (PCs). Screens had to be made with higher resolutions and easier to handle. Fortunately, by the advent of amorphous silicon (a-Si) thin-film transistors (TFTs), when integrated with liquid-crystals, a new generation of TFT-LCD displays were fitted onto the first large scale commercial PCs and laptops. These displays offered a much wider range of vivid colors and faster refresh rates. The fundamental idea behind the TFT-LCD is also not difficult. Using an array of TFTs to alter the voltage behind the liquid-crystals causing them to block portions of RGB light, it made gray-scale possible so that images can be formed.

Figure 1.1: Evolution of the display technologies.

The LCD displays have made a high impact on the display industry as well as

the society during their popularity of the PC era. In the past decade, the world has witnessed a rise of another form of consumer electronics, the handheld devices in which more and more functionalities of the PCs have been integrated. As a result, the demand of a better display has increased tremendously due to the smaller size and higher resolution requirements. Driven by this demand, the development on low-temperature-poly-silicon (LTPS) TFTs and organic light-emitting diodes (OLEDs) have enabled high-contrast and high-resolution small size displays suitable for smart-phones. Since their inception, they have been popular on the market till now [3, 4, 5, 6].

In the past few years, the focus on the Internet-of-Things (IoT) has spurred research activities on wearable electronics, which require curved or flexible displays for conformable shaping as well as high-brightness feature for outdoor use. As a result, the OLED displays started to show some challenges to cope with these requirements [7, 8]. In addition, these flexible displays will be powered by batteries, so a new solution with low power consumption and high brightness will be the key to the realization of this type of displays [9].

In the following sections, several key components in a modern display panel will be introduced.

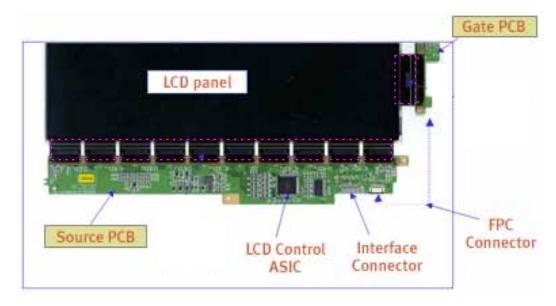

#### 1.2 Display panel components

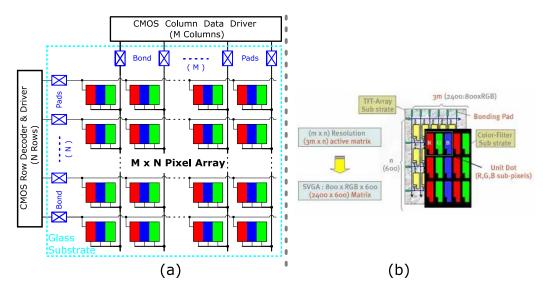

Using a modern LCD panel as a demonstration, shown in Fig. 1.2, there is a number of components required to make a display.

The shown glass panel contains the TFT array, liquid-crystal layer, color filter, polarizer, and transparent electrodes. Then, the off-panel components, which may include power management integrated circuits (ICs), data source generator, row-select signal generator, interface connectors and other required connections to the glass panel. Shown on Fig. 1.2, a number of black ribbon cables (highlighted within

Figure 1.2: The PCB components and the panel of an LCD display.

dashed pink lines) are used to realize such connections. These connections require a complex and precise bonding process to secure links between the glass panel and external printed-circuit boards (PCBs) [10].

The cost of external components are comparatively high, and there is motivation to integrate functionality onto the display panel. Additionally, adding functionality on panel can make display energy efficient.

#### 1.3 Comparison of light media

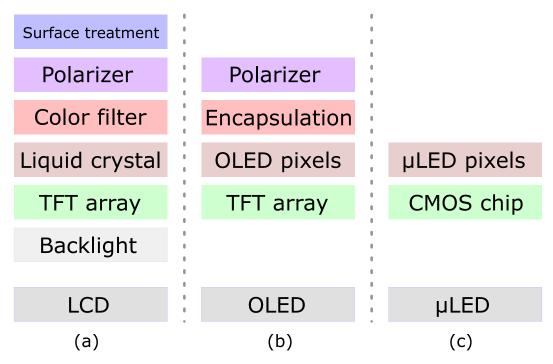

In most of the modern displays, the panel is made by glass which houses the light media and the backplane circuits, as well as filters and other optical components [8].

For a conventional LCD display shown in Fig. 1.3(a), there is a constant-on backlight, which is the source of all the illumination. The function of TFT array and liquid crystal is to block portions of light coming out of the back-light to achieve a range of gradient scales. Then, the color filter is to provide the combination of RGB since back-light is only white color.

Next, shown in Fig. 1.3(b), OLED displays do not require a back-light because

Figure 1.3: Schematic comparison of light media on rigid panels.

they are self-emissive. The TFT array delivers power to each OLED pixel directly so that there is no need of having a constant-on light source. As a result, the color contrast ratio is almost infinite because when pixels are not glowing they are completely dark. However OLEDs suffer from burn-in effect and low electro-luminescence efficiency problems. It also requires a high quality encapsulation layer to isolate the pixels from the environment to extend the life-span.

The shortcomings of OLED devices have led to the development of  $\mu$ LEDs, which are in-organic GaN LEDs processed at  $\mu$ m scale [11]. Conventionally GaN LEDs are used in interior or automobile lighting applications where their high-brightness and high electro-luminescence efficiency properties are exploited. They seem to be the ideal solution to display applications, however, difficulties in mass-transferring pixelated  $\mu$ LED arrays to large TFT backplanes has been the bottleneck. This is the reason that most demonstrations of  $\mu$ LED displays are CMOS driven small-size microdisplays shown in Fig. 1.3(c). With significant advancement in process development, the integration of  $\mu$ LED with TFT backplanes has become possible.

A comparison is provided in Table 1.1 which outlines the characteristics of LCD, OLED and  $\mu$ LEDs. It can be seen that the  $\mu$ LED media are the most attractive due to high output efficiency and long operational life-time [12].

Table 1.1: Comparison of light media

|             | LCD                                            | OLED                   | μLED                     |  |

|-------------|------------------------------------------------|------------------------|--------------------------|--|

| Mechanism   | Color filter/backlight                         | Self-emissive          | Self-emissive            |  |

| Luminous    | Low                                            | Medium                 | High                     |  |

| efficiency  | LOW                                            | Medium                 |                          |  |

| Luminance   | $\sim 3 \times 10^2 \qquad \sim 5 \times 10^2$ |                        | $\sim 3 \times 10^5$     |  |

| $(cd/m^2)$  | (full-color)                                   | (full-color)           | (full-color)             |  |

| Contrast    | Low                                            | Uiah                   | High                     |  |

| ratio       | LOW                                            | High                   | Ingn                     |  |

| Response    | ms                                             | II.e                   | ng                       |  |

| time        | 1115                                           | μs                     | ns                       |  |

| Power       | Medium                                         | Medium                 | Low                      |  |

| consumption | Medium                                         | Wedium                 | LOW                      |  |

| Operating   | $-20 \sim 80^{\circ}C$                         | $-30 \sim 70^{\circ}C$ | $-100 \sim 120^{\circ}C$ |  |

| temperature | -20 73 00 0                                    | 30 70 0                | -100 ~ 120 C             |  |

| Life        | Long                                           | Medium                 | Long                     |  |

| span        | Long                                           | Medium                 | Long                     |  |

#### 1.4 Comparison of backplane circuit technologies

Beside the light media, backplane circuit technologies are also the determining factor for a display [13, 14]. There are several implementations on the market suited for different types of displays shown in Table 1.2.

Crystalline-silicon based CMOS backplane technology is being applied for ultrahigh resolution small-area devices used in virtual-reality (VR) or augmented-reality

Table 1.2: Comparison of backplane technologies

|                                  | Crystalline | Low-temperature   | Amorphous               | Transition        |

|----------------------------------|-------------|-------------------|-------------------------|-------------------|

|                                  | silicon     | poly-silicon      | silicon                 | metal-oxide       |

| Mobility $(cm^2/Vs)$             | $\sim 10^3$ | $\sim 10^2$       | ~ 1                     | ~ 10              |

| Device type                      | p- and n-   | p- and n-         | n- only                 | n- only           |

| Fabrication area diagonal length | Very small  | Small $\sim 10''$ | Very large $\sim 100''$ | Large $\sim 10''$ |

| Electrical stability             | High        | Medium            | Low                     | Low               |

| Device uniformity                | High        | Very low          | High                    | High              |

| Substrate flexibility            | No          | Medium            | High                    | High              |

| Cost                             | Very High   | High              | Low                     | High              |

(AR) gears. Since CMOS transistors possess very high carrier mobility at  $\sim 1000$   $cm^2/Vs$ , they can accommodate a very small pixel down to a dimension of  $5 \,\mu m \times 5 \,\mu m$ , which is crucial for the near-eye VR displays [15, 16]. However, CMOS chips are known for their high fabrication cost and rigidity. Recently, there has been demonstrations on thinning the CMOS wafers and achieve some degree of flexibility, but the area limitation is still the major concern for making larger displays with crystalline CMOS backplane [17].

Next, the low-temperature poly-silicon (LTPS) TFTs have a carrier mobility around  $\sim 100\,cm^2/Vs$  and can also be complementary [18]. They are mostly used on phone-sized displays driving OLEDs [19, 20]. The fabrication of LTPS TFTs requires a laser crystallization process on the amorphous silicon channel region. This procedure causes the TFTs to have poor large-area uniformity so that the display panels

struggle to reach tens of inches in size.

Then, hydrogenated amorphous silicon (a-Si:H) TFTs which have a low mobility of  $\sim 1\,cm^2/Vs$  are conventionally used on TFT-LCD display panels [21]. Because of the constant-on back-light, the TFTs are only acting as switches to control the liquid-crystals. Therefore, these low performing TFTs are sufficient for this purpose [22]. However, due to the random nature of the amorphous material, the large-area uniformity of these TFTs are relatively high. In addition, they can be deposited with low temperature which is suitable for transparent plastic substrate enabling the potential to realize flexible displays.

Lastly, transition-metal-oxide TFTs are also deposited with the amorphous structure [23]. They resemble similar uniformity and flexibility features of a-Si:H TFTs, but with at least one order of magnitude higher carrier mobility [24]. However, their fabrication cost is higher than a-Si:H TFTs and the technology is not yet mature.

#### 1.5 Motivations

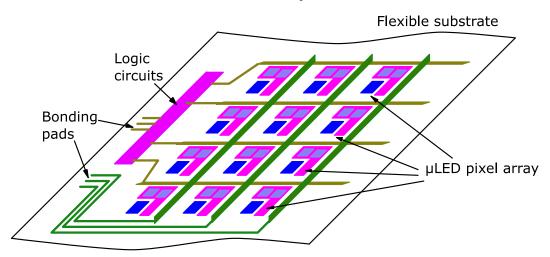

Driven by the rapid growing demand of IoT and wearable devices, flexible displays have become a crucial component in shaping the display technology of the future. Market analysis have predicted a multi-billion dollar market on flexible electronics in the next decade. This research work was carried out with the goal of realizing a flexible display system ("system-on-flex" shown in Fig. 1.4), which is capable of providing high-brightness, low power consumption and high reliability displays.

Shown in the previous introduction,  $\mu$ LEDs appear to be the best choice as the light medium for flexible displays due to its high luminescence efficiency and long life span. On the other hand, a-Si:H TFTs which have excellent large-area uniformity and low cost may emerge as the backplane circuit choice.

After the successful demonstration of  $\mu$ LED integrated onto plastic substrate, it becomes crucial to design reliable a-Si:H backplane circuits to realize flexible displays.

#### System-on-flex

Figure 1.4: The diagram of a flexible  $\mu LED + a$ -Si:H TFT backplane.

Due to the nature of amorphous material, the electrical instability of the TFTs is a major disadvantage, especially in the case of  $\mu$ LED displays. Because these displays are self-emissive, so the TFTs need to supply power unlike their functions of being only switches in the conventional TFT-LCD displays. With this constraint, the well-known mobility degradation of a-Si:H TFTs can cause a display to lose brightness over-time. In addition, the lack of a complementary transistor type further complicates design of additional functionalities on the flexible panel.

With above mentioned challenges in mind, the thesis makes an attempt to provide circuit solutions. In particular, a novel compensation pixel circuit is demonstrated that is able to provide stable brightness despite changing threshold-voltage of the driver transistor on a flexible substrate. In addition, realization of multistage logic circuit with only n-type transistor is demonstrated that has CMOS-like properties.

With these challenges in mind for a-Si:H backplane, this thesis has provided several solutions to tackle the problems, such as compensation pixel circuits to retain  $\mu$ LED brightness over-time and full-swing low-power logic gates to realize complex digital circuits on flexible substrate. All these solutions are to facilitate the realization of flexible displays with the combination of  $\mu$ LED and a-Si:H TFTs.

#### 1.6 Thesis outline

This thesis is organized in the following manner:

Chapter 1 provides a brief introduction of the display technologies for the past half a century and compared the light media and backplane technologies. It also brings up the motivation and goal of the research work.

Chapter 2 discusses background information on existing pixel driving scheme and amorphous silicon TFT properties to prepare readers for the core analysis of the thesis.

Chapter 3 shows a successful integration of  $\mu$ LEDs onto a-Si:H TFT pixel circuit on flexible substrate which demonstrates high-brightness and low-power features.

Chapter 4 proposes a novel compensation pixel circuit on flexible substrate to tackle the electrical instability of the TFTs with mathematical derivation, circuit simulation and measurement results.

Chapter 5 proposes novel logic gates with full-swing and low static leakage current suitable for peripheral circuits that controls pixel arrays on flexible substrate. Also, a demonstration of "system-on-flex" has been realized.

Chapter 6 concludes the thesis and lists suggested future work.

## Chapter 2

## Background

#### 2.1 Display architectures

The majority of the area on the backplane of a display panel is occupied by the pixels. There are two types of display pixel architectures in the existing market, they are passive-matrix and active-matrix methods.

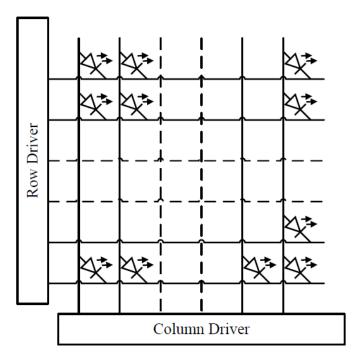

#### 2.1.1 Passive-matrix architecture

In the passive-matrix (PM) addressing scheme shown in Fig. 2.1, there is no transistor backplane involved, only the light media [25]. The LED array is addressed row by row from an external driver. When a row of LEDs is selected, the voltage of the row line turns to ground and individual column driver is set to the desired current to represent the image information of all the LEDs. Because there is no transistor or storage component to maintain the image information, all the LEDs turn off when the next row is being addressed [26].

Even though PM architecture is known for its simplicity of only requiring light media on the display panel without backplane circuits, it is not capable of delivering the needs for large-area and high-resolution displays. Because in order to form any still image or video on a PM display panel, the LEDs need to be driven at a much higher refresh rate. In addition, the column data drivers have to cope with accurate and high-levels of instant current density during the very short ON period of a display cycle which is very difficult to achieve. Therefore, PM architecture is only suitable for small-area and low-resolution digital displays typically less than 200 rows to maintain a standard refresh rate of 60 Hz [26, 27].

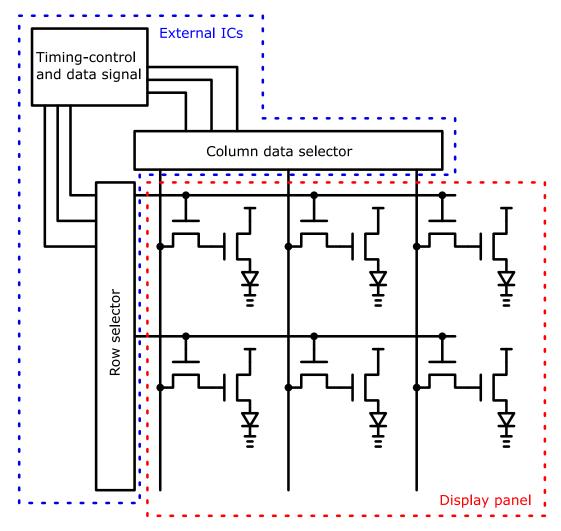

Figure 2.1: Backplane circuit example of an LCD display panel.

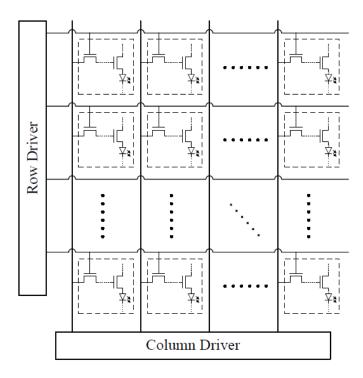

#### 2.1.2 Active-matrix architecture

Considering the disadvantages of PM architecture, the active-matrix (AM) addressing was invented (shown in Fig. 2.2) and have been widely used since its inception [28]. In AM display panels, TFTs are used to control each pixel. There are typically two phases of operation. During programming phase, the data is stored in the pixel circuit. Next, in the emitting phase, the LED will glow proportionately to the stored data in the pixel circuit. The programming operation is carried out row by row through an external IC driver and traverses through the entire display panel. In addition,

the instant peak current density is much reduced compared to the PM architecture because of the continuous emission from the LEDs. Therefore, AM architecture is widely used in flat-panel displays. It is also the method used in this research work.

Figure 2.2: Backplane circuit example of an LCD display panel.

#### 2.2 TFT families for display backplane

After comparing the display architecture and choosing the AM scheme, it is important to understand the differences among existing backplane technologies. The two main ones are low-temperature-poly-silicon (LTPS) and hydrogenated amorphous silicon (a-Si:H).

LTPS TFTs have excellent carrier mobility of  $\sim 100\,cm^2/Vs$  as well as complementary device types, i.e. p- and n-. In addition, the electrical stability of LTPS TFTs is superior compared to a-Si:H ones because of the higher degree of crystallization in the channel region. However, a major drawback of LTPS TFTs is the poor spatial uniformity, i.e. high device variation in a large area. This is due to the non-

uniform crystallization during the laser annealing process which forms the poly-silicon active layer. These spatial variations cause poor pixel performance and result in low image quality. Therefore, LTPS TFT backplane is mostly used for OLED smartphone displays which requires high current and small fabrication area.

Owing to the superior performance of  $\mu$ LEDs against OLEDs, a-Si:H TFTs has emerged to be a viable backplane material solution. Even though the mobility of a-Si:H TFT is just around  $\sim 1\,cm^2/Vs$ , it is sufficient to drive  $\mu$ LEDs with excellent brightness. In addition, a-Si:H TFTs have been used in the TFT-LCD panels for such a long time, the fabrication cost of these backplanes are much lower compared to LTPS panels.

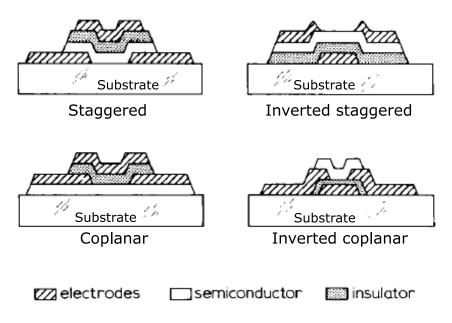

#### 2.2.1 The structure of a-Si:H TFT

Fig. 2.3 depicts four typical device structure of a-Si:H TFTs, i.e. staggered, inverted staggered, co-planar and inverted co-planar. Co-planar (inverted co-planar) devices are fabricated with the semiconductor layer being the first (last). These fabrication techniques are typically used for printed organic TFTs because the printing step does not use a conventional deposition chamber and require all other layers to be made prior to the printing. On the other hand, co-planar devices have sub-optimal contact resistance resulting in lower carrier mobility [29]. The other device category is staggered structure where the semiconductor and gate dielectric layers are sandwiched between the gate and source/drain electrodes. Such configurations can reduce contact resistance which leads to higher carrier mobility. Moreover, the gate dielectric and semiconductor layers could be deposited sequentially without breaking vacuum from the chamber, so that the quality of the material interface is higher [30]. With these considerations, the TFT devices used in this research work are based on the staggered structure.

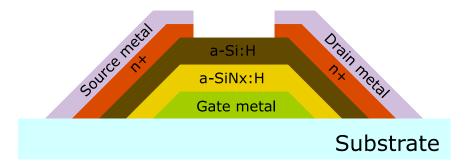

In the detailed layer-by-layer view of a-Si:H TFTs with inverted staggered struc-

Figure 2.3: Four device structures for a-Si:H TFTs.

ture shown in Fig. 2.4, metal gate is at the bottom of the stack and directly fabricated on top of the substrate. Then, a tri-layer of amorphous silicon nitride (a-SiNx:H), intrinsic a-Si:H and doped  $n^+$  are deposited sequentially on top of the gate metal using a plasma-enhanced chemical-vapor deposition (PECVD) system. Afterwards, the source/drain metal is patterned and the tri-layer is etched back to expose the intrinsic a-Si:H layer as the channel of the transistor. After these process steps a-Si:H TFTs can be formed.

Figure 2.4: Fabricated layers of inverted staggered a-Si:H TFTs.

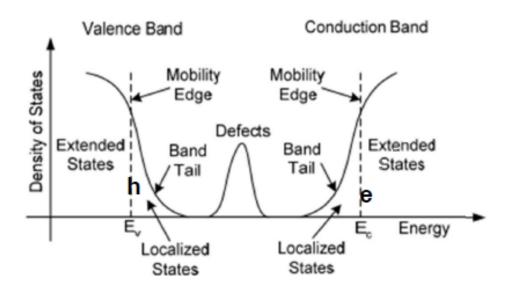

The deposition of a-Si:H layer uses a low-temperature process (typically less than  $300^{\circ}C$ ) which is very different from the high-temperature growth conditions used in crystalline-silicon CMOS fabrication. Shown in Fig. 2.5, the density of state vs.

energy level of amorphous silicon material is presented. Different from the clearly defined band edges of crystalline-silicon, amorphous silicon has broadened tail states extending into the forbidden band-gap caused by localized energy states. In addition, the defects from broken Si-Si bonds contribute to the states in the middle of the band-gap. The high concentration of defects and the slightly n-type nature of amorphous silicon material have made the realization of p-type a-Si:H TFTs difficult [31, 32].

Figure 2.5: The band diagram of intrinsic a-Si:H.

The presence of high density of defects contributes to the low carrier mobility of a-Si:H TFTs [32]. In addition, voltage bias induced degradation may occur under different circumstances [33, 34, 35]. When stressed with a positive gate voltage, there could be more defect states formed in the channel or dielectric layers manifesting as a threshold-voltage  $(V_T)$  shift on the I-V curve. When a-Si:H TFTs are used as the pixel circuits for displays, this degradation can cause the brightness to go down resulting in a short life-span. Therefore, providing a method to compensate for such degradation is a focus of this research work. Furthermore, when considering applied mechanical strain, the electrical instability may behave differently under various strain conditions. Such effect is also studied in this work in details.

#### 2.3 Peripheral control circuits

Traditionally, display panels consist of large array of pixel circuits as illustrated in Fig. 2.6, and several other components such as data and control drivers are outside the panel implemented in expensive CMOS technologies. However, there is growing motivation to integrate some of these components to make displays cheaper, energy-efficient and reliable [36, 37, 38].

Figure 2.6: Backplane and external IC components of a display.

In CMOS technologies, both p- and n- type transistors are available which are efficient for conducting logic "1" and "0", respectively. Unfortunately, this is not the case for a-Si:H TFT technology. Often only n-type device is available for circuit

designers which makes realization of full-swing, energy-efficient, logic circuit a challenging task. Prior solutions mainly focus on fabrication improvement or exploiting external power supply to realize full swing logic gates which is costly and complex. Therefore, circuit solution would be the ideal method to tackle this problem. In this research work, novel circuit solutions to realize full-swing and low-power logic gates are proposed and verified to prove the feasibility of integrating circuit components on panel.

#### 2.4 Summary

This chapter provides the readers with relevant background knowledge on the display architectures and TFT devices.

It outlines the benefit of AM addressing scheme and the benefits of using a-Si:H TFTs in the backplane circuit on flexible substrate. It also explains the shortcomings of a-Si:H TFTs, such as electrical instability under bending and the lack of a complementary device type. Solving those challenges is the focus of this research work and will be presented thoroughly in the following chapters.

## Chapter 3

## Power-efficient pixel circuit

In recent years, micrometer sized light-emitting diodes (µLEDs) have been extensively researched as potential light media for the next-generation of flat-panel as well as flexible emissive displays. µLEDs possess many benefits when compared with organic-light-emitting diodes (OLEDs) such as brightness, operational life-time, and luminescence efficiency [39]. In the past few years, there have been multiple technologies developed for integrating µLEDs onto different substrates such as transfer-printing, epitaxial lift-off, and laser-induced transfer [40]. These methods have attained varying degrees of success. For flexible displays, passive matrix (PM) addressing is still the popular implementation method owing to its simplicity [41]. However, it has several well-known drawbacks such as low resolution and high instant power consumption and etc. Consequently, active-matrix (AM) addressing scheme is needed if the display were to scale to a higher resolution and refresh rate.

At present, the display of choice includes low-temperature poly-silicon (LTPS) TFTs with OLEDs. However, if  $\mu$ LEDs were to become a reality for flexible displays, additional considerations such as cost, scalability, and mechanical stability needs to be investigated.

As mentioned in the previous chapter, the LTPS technology has superior carrier mobility and higher current drive compared to a-Si:H TFT technology. However, it suffers from poorer uniformity over large display area. On the other hand,  $\mu$ LEDs are more power and energy efficient compared to OLEDs. Arguably,  $\mu$ LEDs together with a-Si:H TFTs can be a viable alternative to power-hungry OLED and LTPS panels. This was the motivation for the research described in this chapter. Two pixel circuit configurations with  $\mu$ LEDs are presented and analyzed.

#### 3.1 Source-anode configured conventional pixel

The first method to realize  $\mu$ LED with a-Si:H TFT pixel circuit is to mimic the LTPS+OLED configuration in which the anode of the  $\mu$ LED is placed at the source side of the driving TFT shown in Fig. 3.1. In the pixel circuit, the switch TFT  $(T_1)$  controls the charging and discharging of the storage capacitor in the programming phase and the driving TFT  $(T_0)$  supplies current to the  $\mu$ LED in the emitting phase [42].

Figure 3.1: The conventional 2T pixel circuit with timing-control signals.

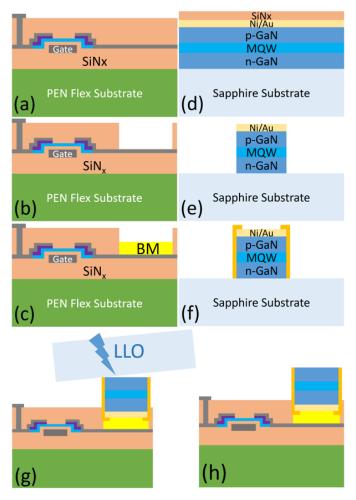

The integration process is divided into three major parts. Fig. 3.2(a) to (c) show the preparation of the surface after a-Si:H TFT pixel circuits have been fabricated

<sup>&</sup>lt;sup>1</sup>This chapter is an amended version of "Integration of GaN light-emitting diodes with a-Si:H thin-film transistors for flexible displays", including modified figures and tables, by M. Asad, Q. Li, C.-H. Lee, W. S. Wong, M. Sachdev, published in Nanotechnology, with ©IOP Publishing 2019. If citing any figure or table, please refer to the original publication.

onto flexible substrate. These steps expose "a landing pad" on the source terminal of  $T_0$  and also coat a bonding metal (BM). (d) to (f) show the process to obtain individual  $\mu$ LEDs from the sapphire substrate. Lastly, (g) and (h) show the final steps of bonding with a laser-lift-off process [43].

Figure 3.2: The single-transfer laser-lift-off process to integrate the  $\mu LED$  onto 2T pixel circuit in a source-anode configuration. (a) to (c) represent the preparation process after the a-Si:H TFT pixel circuit has been fabricated onto a flexible PEN substrate (BM = bonding metal). (d) to (f) show the process steps to fabricate individual  $\mu LEDs$  from a sapphire wafer. (g) to (h) is the bonding and laser-lift-off process to integrate the two parts to form full pixels.

In this experiment, the  $\mu$ LED had a geometry of  $90 \,\mu m \times 90 \,\mu m$ . From the I-V curve and electro-luminescence performance of the  $\mu$ LED, the TFTs in the pixel are designed to have a W/L of  $100 \,\mu m/20 \,\mu m$  and  $1000 \,\mu m/20 \,\mu m$  for  $T_1$  and  $T_0$  respectively. The layout of  $T_0$  uses an inter-digitation style to make the pixel square-

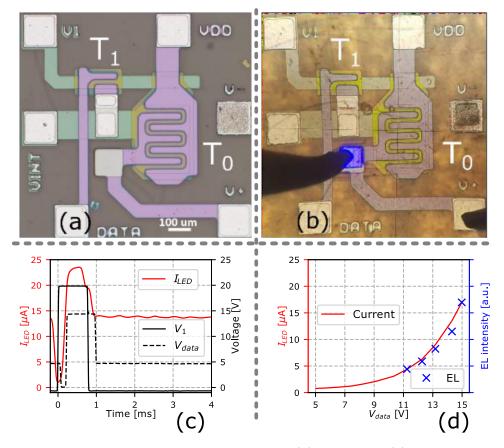

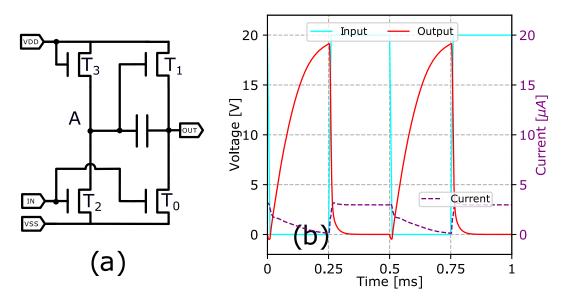

shape. The extracted measurement results showed that the TFTs have an effective carrier mobility  $\mu_{eff}$  of  $\sim 0.9 \, cm^2/Vs$  and a threshold-voltage of  $\sim 3 \, V$ . The  $\mu$ LED has an on-voltage of  $\sim 2.4 \, V$ . When using  $20 \, V$  as the supply  $(V_{DD})$  and  $5 \sim 15 \, V$  as the  $V_{data}$  range, the pixel circuit could supply a current from  $0 \, \mu A$  to  $\sim 17 \, \mu A$ . The post-fabrication micro-graph of the 2T pixel circuit before and after  $\mu$ LED integration is shown in Fig. 3.3(a) and (b), respectively. The transient voltage and current waveform of the full pixel is shown in Fig. 3.3(c) and the current/electro-luminescence vs.  $V_{data}$  is shown in (d).

Figure 3.3: The micro-graph of the 2T pixel circuit (a) before and (b) after  $\mu$ LED bonding. (c) The transient voltage (black) and current (red) waveform of the full pixel circuit when  $V_{data} = 14\,V$ . (d) The current (red) and relative electro-luminescence (crosses) vs.  $V_{data}$ .

#### 3.2 Power-efficient pixel circuit

With the advancement of  $\mu$ LED transfer and bonding technology, there is a distinct advantage of  $\mu$ LED over OLED media which is the ability to create drain-cathode inverted  $\mu$ LED structures shown in Fig. 3.4(b). Unlike the conventional OLED process, where a drain-cathode structure is impractical due to the environmental instability of the electron injection layer [44, 45],  $\mu$ LED devices may be integrated onto the pixel circuit with diode on the drain-side of the driving TFT. This configuration provides much higher dynamic range for the display due to the lower overdrive voltage needed to bias the  $\mu$ LED.

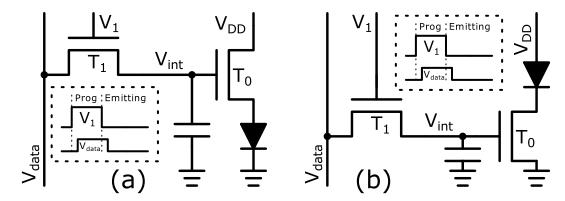

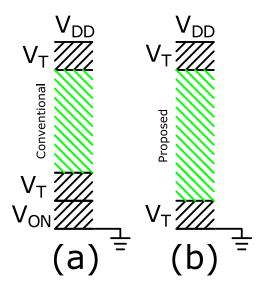

Figure 3.4: (a) The conventional source-anode and (b) proposed drain-cathode 2T pixel circuit.

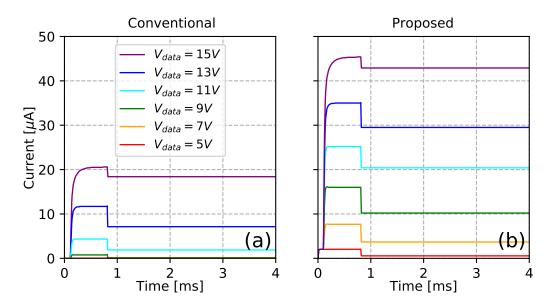

Using a level-61 a-Si:H TFT model [46], the conventional and proposed pixel circuits have been simulated and the transient current waveform is shown in Fig. 3.5(a) and (b), respectively. In the simulation,  $V_{data}$  was set to be between 5V to 15V with 2V intervals to demonstrate the advantages of the proposed drain-cathode configuration.

The improvement of the proposed drain-anode pixel circuit could be explained as follows. Assume TFTs only turn on after threshold-voltage is reached and channel-length-modulation ( $\lambda$ ) is negligible. In the conventional pixel circuit, the lower bound of the  $V_{data}$  needs to be at least the sum of the on-voltage of the  $\mu$ LED ( $V_{ON}$ ) and the threshold-voltage of the driving TFT ( $V_T$ ), so that  $T_0$  can light up the  $\mu$ LED. On

Figure 3.5: Simulated transient current at different  $V_{data}$  of the (a) conventional and (b) proposed pixel circuits.

the other hand, the upper bound of the  $V_{data}$  needs to be one  $V_T$  less of the on-state voltage of  $V_1$  (in this case it is  $V_{DD}$ ).

On the other hand, with the proposed pixel circuit, the  $\mu$ LED is moved to the drain side of  $T_0$  so that the lower bound of  $V_{data}$  only needs to be  $V_T$  while the upper bound remains the same. Therefore, the dynamic range of  $V_{data}$  has been increased from  $V_{DD} - 2V_T - V_{ON}$  to  $V_{DD} - 2V_T$ . The comparison is visually demonstrated in Fig. 3.6.

The first order field-effective transistor equation is used to demonstrate current-voltage relationship for the driving TFT  $(T_0)$  in saturation mode.

$$I_{DS} = \frac{1}{2} \mu_{eff} C_{nitride} \frac{W_0}{L_0} \left( V_{int} - V_T \right)^2$$

(3.1)

The impact of voltage on the drain-source current is squared so that a dynamic range increase on the  $V_{data}$  can drastically increase the current output and the pixel brightness without raising the power supply voltage. On the other hand, if the brightness level remains the same, the proposed pixel circuit would require a much lower

Figure 3.6: The dynamic range comparison on  $V_{data}$  of the (a) conventional and (b) proposed pixel circuits. The green shaded region indicates the dynamic range.

$V_{data}$  signal to program the storage capacitor resulting in low-power consumption on the external column data driver.

In summary, the proposed drain-cathode pixel circuit could provide higher dynamic range and lower power consumption on the external data driver. It is preferred over the conventional source-anode pixel circuit.

#### 3.3 Realization of the drain-cathode pixel circuit

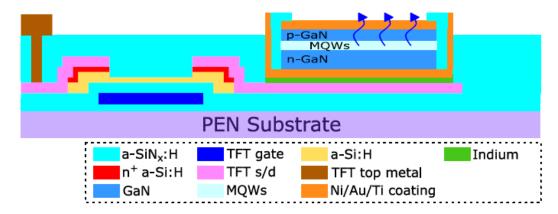

The fabrication of the proposed drain-cathode pixel circuit has a distinct difference from the conventional one. The procedure included a double-transfer step which is necessary to temporarily hold the pixelated  $\mu$ LEDs onto a handler substrate. Only in this way, the cathode side of the  $\mu$ LED can be exposed and bonded to the drain contact pad of the driving TFT. The final schematic of the fabricated pixels are shown in Fig. 3.7. It can be seen that the TFT layers had no difference and the only the  $\mu$ LED is flipped.

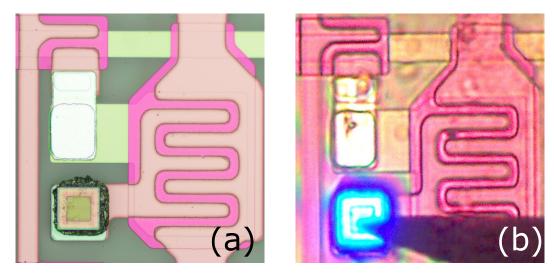

The micro-graphs of the bonded and lit-up pixels with drain-cathode configuration are shown in Fig. 3.8.

Figure 3.7: The schematic view of the fabricated layers using the double-transfer laser-lift-off process to integrate the  $\mu LED$  onto 2T pixel circuit in a drain-cathode configuration.

Figure 3.8: The micro-graph of the 2T pixel circuit (a) before and (b) after  $\mu$ LED bonding with the proposed drain-cathode configuration.

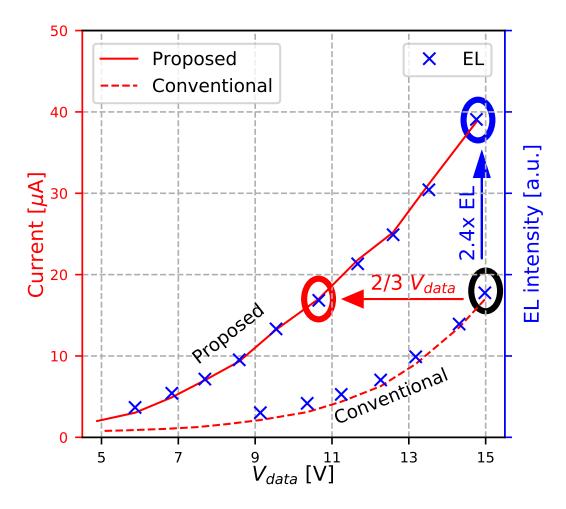

Both the conventional and proposed pixel circuits have been characterized under the same  $V_{DD}=20\,V$  and  $V_{data}=5\,V\sim15\,V$  conditions and the results are illustrated in Fig. 3.9. The proposed pixel circuit could provide a maximum output current of  $\sim40\,\mu A$  and the conventional one was only  $\sim17\,\mu A$ , this is a 2.4x improvement. Such increase in dynamic range is also reflected in the electro-luminescence data shown as blue crosses in the figure.

Meanwhile, the proposed pixel circuit only required  $\sim 11 V$  on the  $V_{data}$  signal to achieve the same brightness as the conventional pixel when  $V_{data}$  was equal to 15 V. Assume each  $V_{data}$  has equal probability during normal display operation, the energy saving could be up to 38% on the column data driver.

Figure 3.9: Current and EL intensity comparison of the conventional and proposed pixel circuits.

In conclusion, the proposed drain-cathode pixel circuit using high-performance µLEDs and a-Si:H TFTs have been demonstrated, it provides advantages of high dynamic range and low power consumption. Such benefits may lead to the realization of next-generation flexible displays.

However, this integration is not problem free. Even though  $\mu$ LEDs do not demonstrate drastic differences under long-term electrical stress or mechanical strain, a-Si:H TFTs do suffer from these shortcomings. It is well known that amorphous silicon with its random nature degrades under voltage-bias induced stress and applied bending. Therefore, it is crucial to find a solution to tackle these problems so that the back-

plane TFT circuits could function reliably on a flexible substrate. These concerns lead to a solution that will be presented in the next chapter in which a compensation pixel circuit is proposed and its operating principle and effectiveness under bending are thoroughly discussed and analyzed.

# Chapter 4

# Compensation pixel circuits for flexible displays

Hydrogenated amorphous silicon (a-Si:H) thin-film transistor (TFT) technology is a popular and inexpensive technology of choice to realize active-matrix liquid-crystal displays (AM-LCDs) [42, 47]. The technology has its advantages in low-temperature processing and excellent device uniformity in large-area fabrication. These advantages may facilitate the realization of next-generation flexible displays. Recent advancements in micro-light-emitting-diode (μLED) fabrication and transfer have enabled the possibility of integrating μLED onto a-Si:H TFT backplane to achieve low-power and flexible emissive displays [48, 49]. Unlike organic-LEDs (OLEDs), μLEDs are inorganic devices with much lower power consumption to reach equivalent brightness [50]. Thus, a-Si:H technology with relatively lower carrier mobility compared to low-temperature poly-silicon (LTPS) which is commonly used in OLED display for smart-phones, becomes a potent candidate for the backplane circuits.

The previous chapter has proven that the integration of  $\mu$ LED onto flexible PEN substrate with a-Si:H TFTs is feasible. The combination may provide a low-cost and mechanical flexible solution to next-generation displays.

Even though a-Si:H technology possesses great advantages to realize flexible back-

plane circuits, its shortcomings are also well known. The voltage-bias induced degradation of electrical stability causes a reduction of output current over-time. This behavior is mainly due to defect-creation and charge-trapping in the a-Si:H channel and the gate dielectric layers, respectively [51]. The degradation is usually modeled as a threshold-voltage shift  $(\Delta V_T)$  [52, 53]. If left uncompensated, the degradation can result in brightness loss over-time and lead to shortened life-time of a display panel. A number of circuit solutions have been proposed to tackle this issue including reverse-bias annealing of the emitting TFT [45], sensing the  $\Delta V_T$  of the emitting TFT using external ICs [54], internally sensing the  $\Delta V_T$  using feedback TFTs [55], and charge-transfer using a correlation between driving and compensation TFTs [46]. All these methods have compensation capabilities to varying degrees. Their drawbacks include: complex control signals, added pixel circuit complexity, high cost of external CMOS circuits, and slower operating speed due to internal sensing and reverse annealing.

Furthermore, when fabricated onto flexible substrates, a-Si:H TFTs have another degree of variation due to applied mechanical strain. Tensile and compressive strains cause a-Si:H TFTs to degrade differently under constant voltage bias [56]. The orientation of the TFT also affects the degradation under bending [57, 58]. This additional factor should be taken into account when designing pixel circuits on flexible substrates.

This chapter first discusses prior compensation schemes, and then presents a charge-transfer self-compensating 6-TFT (6T) pixel circuit with only two control signals implemented on a flexible substrate. The proposed 6T pixel circuit provides reliable compensation performance when laid flat or even under mechanical strain. The proposed pixel circuit operates under an enhanced charge-transfer method to provide stable output current to the display media. The layout of the pixel is also specifically designed to mitigate the impact of bending on the circuit performance. Moreover, detailed operation of the 6T pixel circuit with various bending simulation and measurement results are thoroughly investigated.

# 4.1 Introduction to compensation schemes

## 4.1.1 Conventional 2T pixel circuit

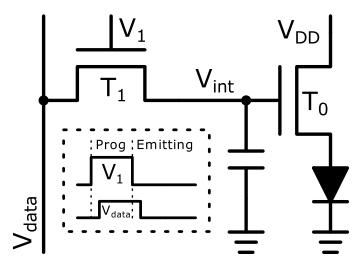

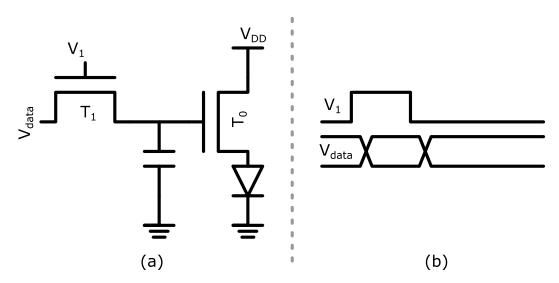

The simplest active-matrix pixel circuit involves two TFTs, one functions a switch  $(T_1)$  and the other one functions as a driver  $(T_0)$  that supplies power to the light medium, such as an OLED or a  $\mu$ LED shown in Fig. 4.1(a). The pixel circuit also contains a storage capacitor realized by metal-insulator-metal (MIM) layers. The operation of the pixel circuit is divided into two phases, programming and emitting shown in Fig. 4.1(b). During programming phase,  $T_1$  is switches on by a high control signal  $V_1$  and immediately afterwards  $V_{data}$  programs the storage capacitor with the desired brightness voltage level. After allowing sufficient time for the storage capacitor to be fully charged,  $V_1$  is turned low to switch  $T_1$  off, the pixel enters the emitting phase, in which the pixel glows with the programmed brightness until the next refresh cycle begins.

Figure 4.1: The (a) schematic and (b) control signals of the proposed 2T pixel circuit.

During the normal operation of a display panel, the TFTs are constantly under voltage-bias induced stress and their performance degrade over-time, especially the driving TFTs because they are operating in saturation mode nearly all the time. In the case of a-Si:H TFTs, the degradation could be generally modeled by a threshold-voltage shift  $(\Delta V_T)$  [59, 51, 56] given by the equation below:

$$\Delta V_T(t) = (V_{GS} - V_T) \times \left[1 - e^{-(\frac{t}{\tau})^{\beta}}\right]$$

(4.1)

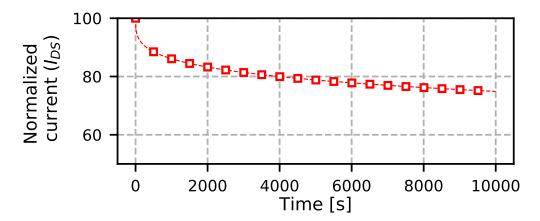

The  $\tau$  and  $\beta$  are process parameters related to the fabrication condition of the TFTs, and "t" is the time under which the TFTs are bias stressed. An example of output current  $(I_{DS})$  decay under constant voltage bias is shown in Fig. 4.2. In this example, the parameters values were  $\tau = 116000$  and  $\beta = 0.3053$ , the drain voltage  $V_{DD}$  was 20 V and the  $V_{data}$  was 15 V.

Figure 4.2: An example of  $I_{DS}$  degradation under constant voltage-bias over-time.

It is noticed that without any designated compensation mechanism, the 2T pixel circuit alone is not suitable for any display product due to a very short life-time. The output current decreases by 20% even within the first hour of operation.

Therefore, in order to utilize a-Si:H TFTs as the backplane circuit devices for display panels, compensation scheme is required. The following sections will briefly introduce several prior compensation schemes and list their pros and cons to facilitate a well-rounded understanding of the compensation concept.

# 4.1.2 Compensation scheme - external detection

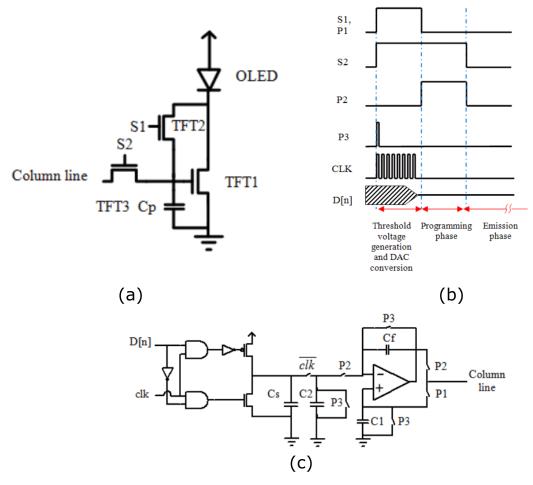

One intuitive method for compensation is to engage external CMOS ICs to detect the threshold-voltage shift in the pixel circuit. Amiri et al. has proposed a simple pixel circuit with off-panel ICs to achieve this goal [60].

The full compensation scheme is shown in Fig. 4.3. It consists of a 3-TFTs and 1-capacitor (3T+1C) pixel circuit shown in Fig. 4.3(a) and an external cyclic digital-to-analog converter (DAC) with its associated switches and capacitors shown in Fig. 4.3(c). The timing-control signals of the pixel circuit and the external switches are presented in Fig. 4.3(b).

Figure 4.3: An external compensation method using (a) a 3T+1C pixel circuit. The control signals and off-panel IC schematic are shown in (b) and (c), respectively [60].

The operating principle of the proposed compensation scheme relies on the correct

generation and extraction of the threshold-voltage on the driving TFT ( $TFT_1$ ). In the first phase of operation, both  $S_1$  and  $S_2$  switches are set to high so that  $TFT_1$  is in a diode-connected mode. At the same time, the DAC is sampling the voltage on the column line which has a direct relationship with the threshold-voltage of  $TFT_1$ . As soon as the sampling phase ends, the DAC has obtained the threshold-voltage information and the weighted sum of the data voltage, threshold-voltage and the overdrive voltage of  $TFT_1$ . It then outputs this lumped sum voltage to the column line which subsequently programs the pixel circuit. The last phase is the emission in which the compensated data value has been stored on the capacitor, and the pixel is supplying the desired current to the LED.

The advantageous side of the external compensation method is that it could provide accurate output-current corrections for up to 5 V of  $\Delta V_T$  within a narrow variation of only 3% [60]. In addition, the simple 3T+1C pixel circuit with only two timing-control signals are also beneficial. However, there are several drawbacks about the scheme. First, the speed of operation is limited because the external DAC has to perform the sequence of sense-correct-program for every single pixel in a row of a display panel. For example, if a 60 Hz RGB HD display with a resolution of  $1920 \times 1080$ were to be compensated, there needs to be at least  $1920 \times 3 = 5760$  sense-correctprogram sequences carried out in a single display cycle of 16.67 ms for a single row of tri-color pixels. The calculated sense-correct-program time for each pixel is less than  $3 \mu s$  which is a strict timing requirement for the external ICs. As a result, this scheme consumes a substantial amount of power due to its high operating speed. In addition, the  $V_{data}$  lines are being charged and discharged by serially connected transistors which may impact the speed and limit the refresh rate of the display. Moreover, threshold-voltage degradation may also occur on the other two TFTs in the pixel circuit causing inaccurate compensation.

In summary, the external compensation scheme could provide accurate output

current to a certain degree for pixels with high values of  $\Delta V_T$ , but its scaling capability to accommodate higher resolution display panels is limited due to demanding off-panel hardware components, high power consumption and implementation complexity.

# 4.1.3 Compensation scheme - reverse annealing

Beside external compensation scheme, there are also several methods that use slightly complex pixel circuits to tackle the  $\Delta V_T$  within each pixel. One of the methods uses a reverse annealing scheme to partially rectify the  $\Delta V_T$  on the driving TFT.

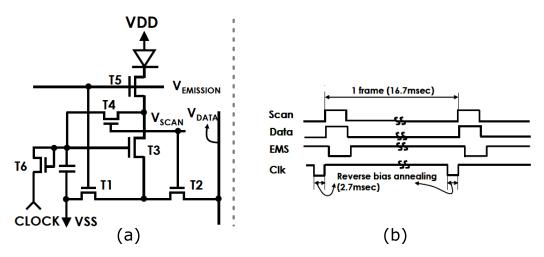

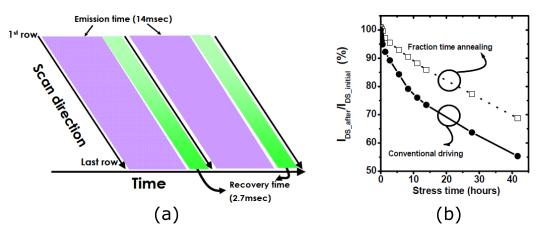

Lee et al. has proposed a 6-TFT and 1-capacitor (6T+1C) pixel circuit using this concept [61]. The full pixel circuit and the timing-control signals are shown in Fig. 4.4(a) and (b), respectively. This pixel circuit uses a portion of the display cycle to apply a negative overdrive voltage on the driving TFT  $(T_3)$ , in this case, a  $2.7 \, ms$  recovery time has been taken off the full display cycle of  $16.67 \, ms$  to facilitate the reverse annealing procedure.

Figure 4.4: A reverse annealing compensation method [61] using (a) a 6T+1C pixel circuit. The control signals schematic shown in (b).

The  $\Delta V_T$  behavior of a-Si:H TFTs have been well investigated and it is known that positive (negative) gate-bias stress will result in positive (negative)  $\Delta V_T$  [53]. The 6T+1C pixel circuit exploits this idea. At the end of the emission phase, the external

clock signal applies a negative value lasting  $2.7 \, ms$  shown in 4.5(a). The resulting voltage-bias stress on the gate of the driving TFT is  $-10 \, V$  during the  $2.7 \, ms$ .

After a 42-hour accelerated test, the result shows that the compensated output current could maintain approximately 70% of the original current while the uncompensated value dropped to 55% shown in 4.5(b). The measured threshold-voltage on the driving TFT has shifted by  $0.48\,V$  compared to the uncompensated value of  $0.75\,V$ .

Figure 4.5: (a) The schematic of the reverse-annealing time frame with respect to the full display cycle. (b) The compensation performance by the reverse annealing compensation method [61]. The solid circles represent normalized output current degradation without compensation and the hollow squares are for reverse annealing method.

The benefit of the reverse annealing method is that the compensation is applied on the individual pixels. It does not involve complex external detection circuits. The shortcomings of this method is also obvious: the compensation could never fully recover all the  $\Delta V_T$  because the reverse annealing is only slowing down the degradation on the TFT but not rectifying it. Furthermore, the loss of emission phase due to the required recovery period may cause flickering during display operation. Since the  $2.7 \, ms$  recovery time is a significant portion (16.2%) of the full display cycle, the pixel can not glow during this phase which may cause negative viewer experience.

Therefore, the reverse annealing compensation scheme attempts to solve the  $\Delta V_T$  by slowing down the degradation of the driving TFT, however, it suffers from non-

optimal compensation performance and potentially poor viewer experience.

## 4.1.4 Compensation scheme - internal detection

Since the external detection method shows promising result at pixel level, there has been much efforts to incorporate the  $V_T$  detection within each pixel so that the dependence on external ICs could be potentially relieved.

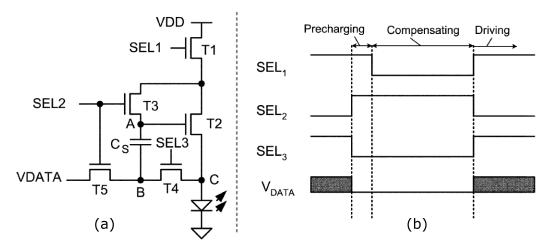

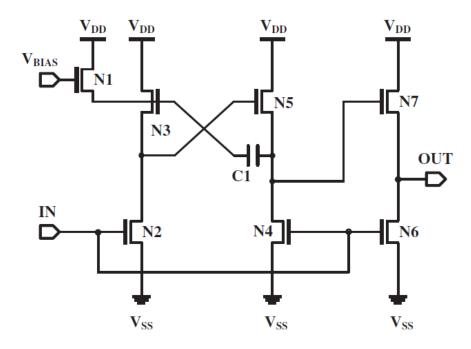

Ashitiani et al. has proposed a 5-TFT and 1-capacitor (5T+1C) pixel circuit [55] with three timing-control signals to tackle the  $\Delta V_T$  problem. The schematic and control signals are shown in Fig. 4.6(a) and (b), respectively.

Figure 4.6: (a) The schematic and (b) timing-control signals of the 5T+1C pixel circuit engaging an internal  $V_T$  detection scheme [55].

This compensation scheme divides each display cycle into pre-charging, compensating, and driving/emitting phases. During pre-charging phase, the gate (node A) of the driving TFT  $(T_2)$  is charged close to  $V_{DD}$  while the data line voltage is also charged to the desired value. Then, in the compensating phase,  $T_2$  is draining current in a diode-configured mode such that node A voltage eventually reaches around the threshold-voltage of  $T_2$  ( $V_{T,2}$ ). In the last phase, the sum of the data voltage and  $V_{T,2}$  is pumped on to the gate of  $T_2$  to achieve compensation. Since the  $\Delta V_T$  of  $T_2$  will constantly go up due to the operation of the pixel, the voltage at node A will also rise accordingly to mitigate the  $\Delta V_T$  on  $T_2$ .

The transient node A voltage, output current and the compensation performance vs. increasing  $\Delta V_T$  are shown in Fig. 4.7(a), (b) and (c). The node A voltage is able to rise according to the  $\Delta V_T$  shown in Fig. 4.7(a) from 0 V to 1 V. The overall compensation result also achieved a 90% output current retention rate with a 4 V threshold-voltage shift.

Figure 4.7: (a) The transient voltage at node A and (b) OLED current during a display cycle. (c) Compensation performance at different output current with increasing  $\Delta V_T$  [55].

The internal detection compensation scheme has provided another approach to tackle the threshold-voltage shift. The advantages of this design is its self-contained nature and relative better compensation result because there is no need to involve additional circuitries to extract the threshold-voltage and the output current retention rate is higher than the reverse annealing method. However, the complex timing-control signals could be difficult to generate and the  $\Delta V_T$  on  $T_1$  is not accounted for which could also contribute to the non-ideal compensation results.

## 4.1.5 Compensation scheme - charge transfer

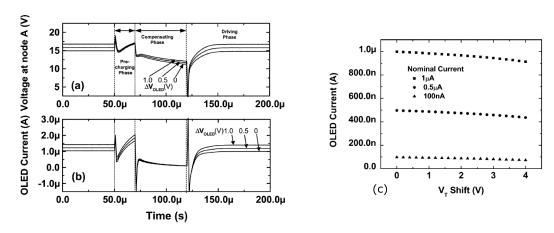

Beside the internal detection compensation method, Yang et al. has proposed another approach of a charge-transfer mechanism along with a 4-TFT (4T) pixel circuit with its three timing-control signals shown in Fig. 4.8(a) and (b), respectively.

The 4T pixel circuit uses a correlation between difference of  $\Delta V_T$  in either linear

Figure 4.8: (a) The schematic and (b) timing-control signals of the charge-transfer 4T pixel circuit [46].

and saturation mode of a TFT to compensate the output current by raising voltage at node A. The simulated node A voltage and output current at different  $V_{data}$  are shown in Fig. 4.9(a) and (b), respectively. It can be seen that when  $\Delta V_T$  rises from 0 V to 5 V, node A voltage goes up accordingly to compensate.

Figure 4.9: (a) The transient voltage at node A  $(V_{GS,0})$  in the driving phase of a display cycle. (b) Compensation performance at different output current with increasing  $\Delta V_T$  [46].

The charge-transfer method provides good compensation results. However, the complex timing-control signals and gaps in degradation between the two correlation TFTs are its disadvantages. The charge-transfer method leads to the proposed novel 6-TFT pixel circuit with simplified timing-control signals, which will be thoroughly introduced and analyzed in the next sections.

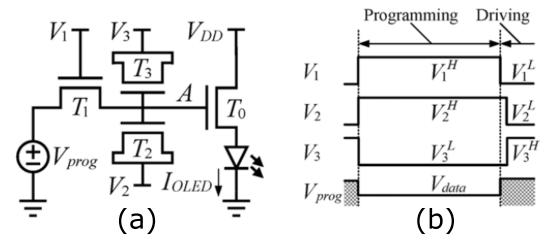

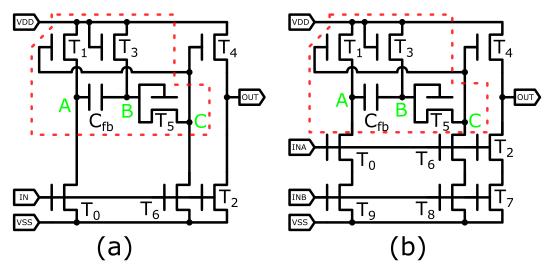

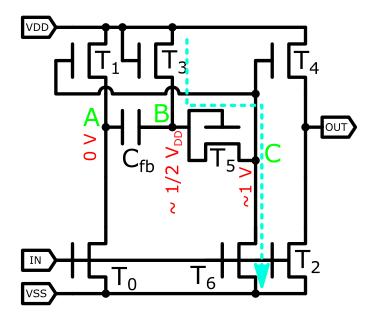

# 4.2 The proposed 6T pixel circuit and compensation method

Prior work discussed previously has laid out different pathways to the compensation of pixel circuits. The most effective method is the charge-transfer method, however, the 4T pixel circuit previously proposed by [46] has its deficiencies. To overcome those shortcomings, A novel 6T pixel circuit has been proposed to mitigate the impact of electrical instability of flexible a-Si:H TFTs based on the specific ratio of TFT degradation in linear and saturation modes [62]. It provides enhanced compensation performance through a self-compensating charge-transfer process. In addition, special consideration to the layout of TFTs has been given to ensure the correct behavior of the pixel circuit under different bending conditions. Furthermore, only a pair of timing signals is sufficient to control a row of such pixels, which reduces the complexity of external drivers compared to prior solutions [54, 55, 46] <sup>1</sup>.

# 4.2.1 Circuit operation