# Fabrication of an Atom Chip for Rydberg Atom-Metal Surface Interaction Studies

by

Owen Cherry

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Master of Science

in

Physics

Waterloo, Ontario, Canada, 2007 © Owen Cherry 2007 I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Owen Cherry

#### Abstract

This thesis outlines the fabrication of two atom chips for the study of interactions between <sup>87</sup>Rb Rydberg atoms and a Au surface. Atom chips yield tightly confined, cold samples of an atomic species by generating magnetic fields with high gradients using microfabricated current-carrying wires. These ground state atoms may in turn be excited to Rydberg states. The trapping wires of Chip 1 are fabricated using thermally evaporated Cr/Au and patterned using lift-off photolithography. Chip 2 uses a Ti/Pd/Au tri-layer, instead of Cr/Au, to minimize interdiffusion. The chip has a thermally evaporated Au surface layer for Rydberg atom-surface interactions, which is separated from the underlying trapping wires by a planarizing polyimide dielectric. The polyimide was patterned using reactive ion etching. Special attention was paid to the edge roughness and electrical properties of the trapping wires, the planarization of the polyimide, and the grain structure of the Au surface.

## Acknowledgments

Over the course of my work, a number have people have offered invaluable help and to them I feel a great deal of gratitude. First and foremost I would like to thank my supervisor, Dr. James D. D. Martin, for all of his support and assistance throughout my research. His passion for his and his students' work has always inspired me.

I would like to acknowledge my M. Sc. examination committee, Dr. Jan Kycia and Dr. Xiaorong Qin, for giving their time and valuable comments, and Dr. Donna Strickland for being a member of my advisory committee.

The work in this thesis would not have been possible without the generosity and accommodation of Dr. Raafat Mansour, director of the CIRFE facility, who allowed me to use the CIRFE clean room. Without these facilities, much of the work in this thesis would not have been possible. I would also like to thank the members of the CIRFE group for their assistance and guidance, specifically Bill Jolley and Reena Al-Dahleh. Reena went out of her way on many occasions to help me with fabrication processes, mask making and SEM imaging and I am truly grateful. Thank you to Roger Grant for sharing some of his wisdom through many discussions, and to Siamak Fouladi for giving his help with SEM imaging.

I owe a great deal of thanks to Czang-Ho Lee who, while completing his PhD thesis, spent many late nights helping me with early stages of fabrication in the a-SiDIC clean room. Likewise, Zhara Fakhraai who generously gave her time to take AFM for me. I would like to thank many people in the department of physics, including Judy McDonnell for her timely reminders and Andy Colclough for his outstanding guidance in the student machine shop.

I would like to thank my current and former group members Jeff, Parisa, Joe, Roger, Blair, Mukto, Koroush, Maria, and Ashton. Thank you to Leslie Dema for carefully editing this thesis.

To my family and friends, thank you all so much for your constant support during my entire university education. My parents, Lois and Nik, have helped me in so many ways over these past eight years, including twelve moves! My brother and sister, Robin and Allison, have always been my best friends.

# Dedication

This thesis is dedicated to my parents, Lois and Nik, for their unending love and encouragement.

I also dedicate this thesis to my grandmother, Marion Aitkin, whose excitement of learning is truly inspiring.

# Contents

| 1 | Intr | roduction                                | 1          |

|---|------|------------------------------------------|------------|

| 2 | Bac  | ekground                                 | 4          |

|   | 2.1  | Atom Chips                               | 4          |

|   |      | 2.1.1 Magnetic Trapping                  | 4          |

|   |      | 2.1.2 Miniaturization                    | 7          |

|   |      | 2.1.3 Losses and Fragmentation           | 8          |

|   | 2.2  | Rydberg Atoms Near Metal Surfaces        | 9          |

|   | 2.3  | Thin Film Growth and Structure           | 11         |

|   |      | 2.3.1 Physical Vapour Deposition         | 11         |

|   |      | 2.3.2 Interdiffusion                     | 12         |

| 3 | Fab  | orication Methods, Materials and Devices | L <b>3</b> |

|   | 3.1  | Spin Coating                             | 13         |

|   | 3.2  | Metallization                            | 14         |

|   |      | 3.2.1 Evaporation                        | 14         |

|   |      | 3.2.2 Sputtering                         | 16         |

|   | 3.3               | Photolithography                                                                                                                                              | 8ء                         |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   |                   | 3.3.1 Photoresist                                                                                                                                             | 18                         |

|   |                   | 3.3.2 Mask Aligner                                                                                                                                            | 20                         |

|   |                   | 3.3.3 Patterning                                                                                                                                              | 21                         |

|   | 3.4               | Planarization                                                                                                                                                 | 25                         |

|   | 3.5               | Reactive Ion Etching                                                                                                                                          | 27                         |

|   | 3.6               | Wirebonding                                                                                                                                                   | 28                         |

|   | 3.7               | Scanning Electron Microscope                                                                                                                                  | 29                         |

|   | 3.8               | Atomic Force Microscope                                                                                                                                       | 31                         |

|   | 3.9               | Dektak Surface Profiler                                                                                                                                       | 32                         |

|   |                   |                                                                                                                                                               |                            |

| 4 | Ato               | m Chip Design                                                                                                                                                 | 3                          |

| 4 | <b>Ato</b> 4.1    | m Chip Design 3  Experimental Setup                                                                                                                           |                            |

| 4 |                   |                                                                                                                                                               | 33                         |

| 4 | 4.1               | Experimental Setup                                                                                                                                            | 33<br>35                   |

| 4 | 4.1               | Experimental Setup                                                                                                                                            | 33<br>35<br>37             |

| 4 | 4.1               | Experimental Setup                                                                                                                                            | 33<br>35<br>37             |

| 4 | 4.1               | Experimental Setup                                                                                                                                            | 33<br>35<br>37<br>38       |

| 4 | 4.1               | Experimental Setup 3  Trap Geometry and Layout 3  Trapping Wires 3  4.3.1 Substrate 3  4.3.2 Wire Material 3  4.3.3 Wire Patterning Method 3                  | 33<br>35<br>37<br>38       |

| 4 | 4.1<br>4.2<br>4.3 | Experimental Setup 3  Trap Geometry and Layout 3  Trapping Wires 3  4.3.1 Substrate 3  4.3.2 Wire Material 3  4.3.3 Wire Patterning Method 3  Planarization 4 | 33<br>35<br>37<br>38<br>39 |

| 5 | Ato | m Chi  | p Fabrication                     | 46 |

|---|-----|--------|-----------------------------------|----|

|   | 5.1 | Substi | rate                              | 47 |

|   | 5.2 | Trapp  | ing Wires                         | 48 |

|   |     | 5.2.1  | Mask                              | 49 |

|   |     | 5.2.2  | Photoresist Patterning            | 49 |

|   |     | 5.2.3  | Metal Deposition                  | 53 |

|   |     | 5.2.4  | Lift-off                          | 58 |

|   |     | 5.2.5  | Diffusion                         | 59 |

|   |     | 5.2.6  | Electrical and Thermal Properties | 62 |

|   |     | 5.2.7  | Wire Edges and Surface            | 67 |

|   | 5.3 | Plana  | rization                          | 71 |

|   |     | 5.3.1  | Spin-on Glass                     | 71 |

|   |     | 5.3.2  | Polyimide                         | 74 |

|   |     | 5.3.3  | Polyimide Patterning              | 78 |

|   |     | 5.3.4  | Pinholes                          | 82 |

|   |     | 5.3.5  | Degree of Planarization           | 84 |

|   | 5.4 | Shield | Layer                             | 85 |

|   |     | 5.4.1  | Grain Size and Roughness          | 90 |

|   | 5.5 | Dicing | g, Assembly and Storage           | 93 |

|   |     | 5.5.1  | Dicing                            | 94 |

|   |     | 5.5.2  | Mounting                          | 95 |

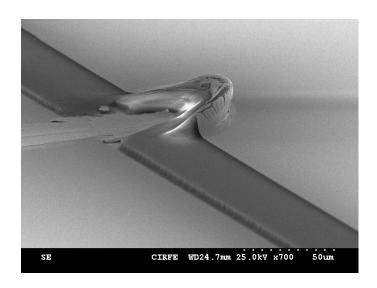

|   |     | 5.5.3  | Wirebonding                       | 95 |

|   |     | 5.5.4  | Storage                           | 96 |

| 6 Summary and Outlook           | 97          |

|---------------------------------|-------------|

| Appendix I. Process Workflow    | 102         |

| Appendix II. Fabricated Chips   | 104         |

| Appendix III. Processing Errors | 105         |

| Appendix IV. List of Acronyms   | 112         |

| Bibliography                    | <b>11</b> 4 |

# List of Tables

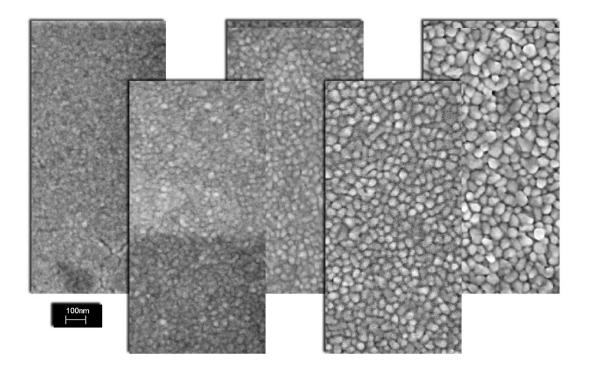

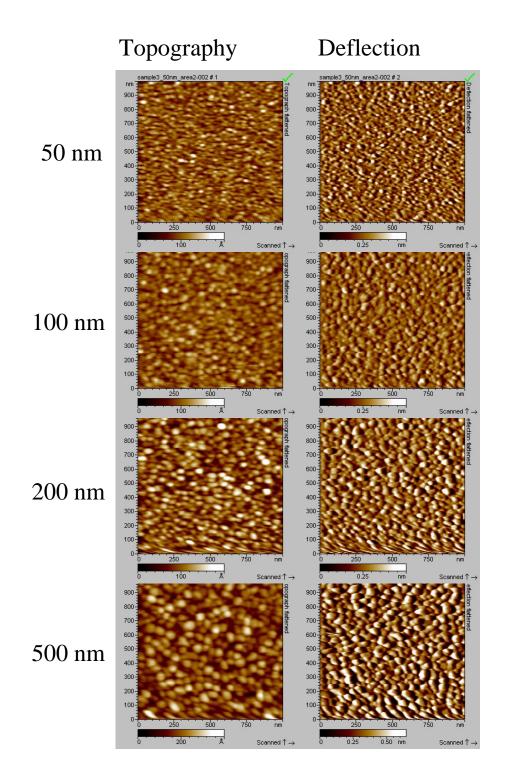

| 5.1 | Average grain diameter vs. Au film thickness | 91 |

|-----|----------------------------------------------|----|

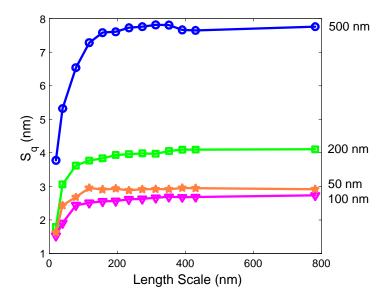

| 5.2 | RMS roughness vs. Au film thickness          | 93 |

# List of Figures

| 2.1  | Trapping potential formed by a current carrying wire and bias field                | 5  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | Configurations of U-wire and Z-wire traps and corresponding trapping potentials in |    |

|      | the z and y planes                                                                 | 6  |

| 2.3  | Trapping potentials for single wire and three wire guide                           | 8  |

| 2.4  | Diagram of electric field from Rydberg atom and image charges                      | 10 |

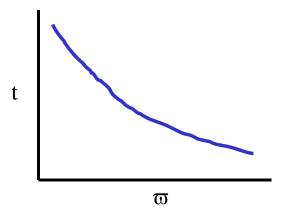

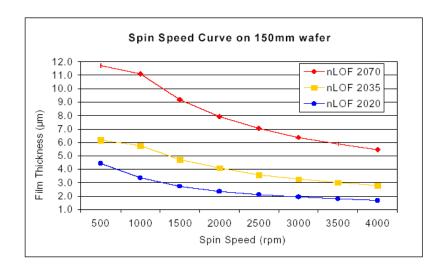

| 3.1  | Typical spin curve plotting spun thickness vs. spin speed                          | 14 |

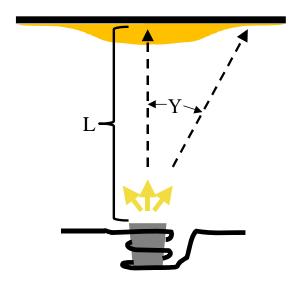

| 3.2  | Geometric non-uniformity in evaporated film thickness                              | 16 |

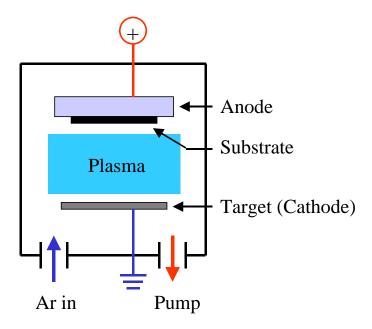

| 3.3  | Diagram of a parallel plate sputtering system                                      | 17 |

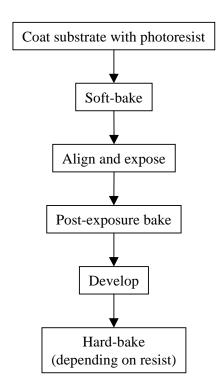

| 3.4  | Workflow for patterning photoresist                                                | 18 |

| 3.5  | Intensity at the surface of photoresist when exposed through a mask                | 19 |

| 3.6  | Slope profiles of positive and negative resists                                    | 19 |

| 3.7  | Characteristic curve of a negative and positive photoresist                        | 20 |

| 3.8  | Exposure profiles of negative resist                                               | 20 |

| 3.9  | Three methods of patterning a metal wire                                           | 22 |

| 3.10 | Metal evaporation vs. sputtering in lift-off lithography                           | 25 |

| 3.11 | Profile of a planarizing material over patterned wires                             | 25 |

| 3.12 | Depth profile of interaction regions in SEM                                              | 30 |

|------|------------------------------------------------------------------------------------------|----|

| 4.1  | Submount for atom chip                                                                   | 34 |

| 4.2  | Two trap configurations for chip wires                                                   | 36 |

| 4.3  | Layout of Chip 1                                                                         | 36 |

| 4.4  | Layout of Chip 2                                                                         | 37 |

| 4.5  | Three methods of achieving a planar surface above atom chip wires                        | 41 |

| 4.6  | Planarization of a single wire vs. a gap                                                 | 43 |

| 4.7  | Schematic cross section of Chip 2 design                                                 | 45 |

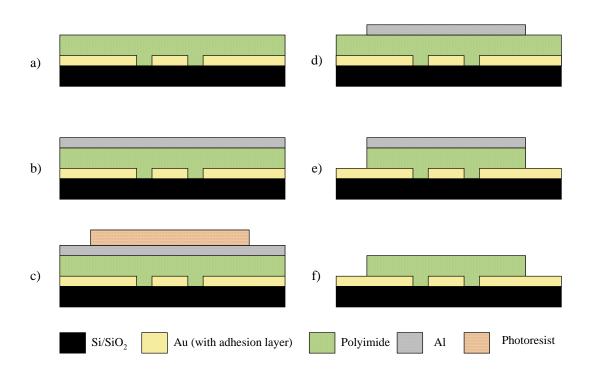

| E 1  | An outline of the februaries process for Chin 2                                          | 47 |

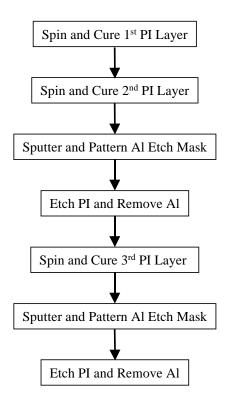

| 5.1  | An outline of the fabrication process for Chip 2                                         |    |

| 5.2  | Spin curves for AZ 2000 nLOF series of photoresists                                      | 51 |

| 5.3  | Modified Edwards evaporator                                                              | 54 |

| 5.4  | Quartz crystal and holder for film thickness monitoring                                  | 55 |

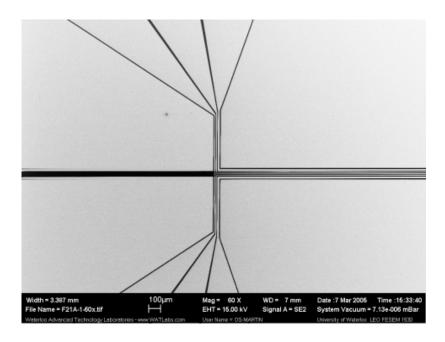

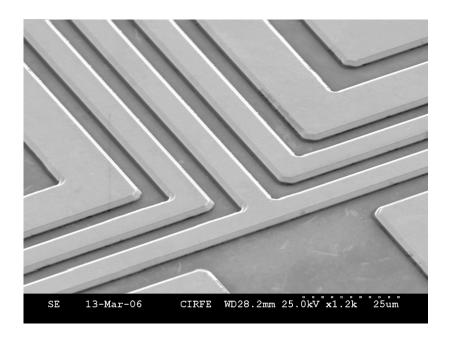

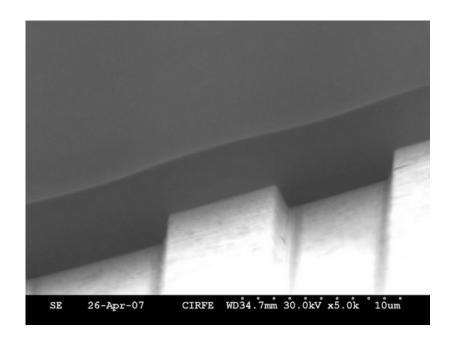

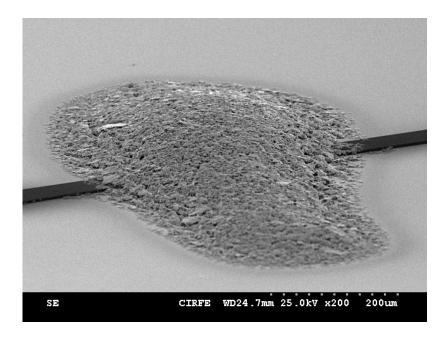

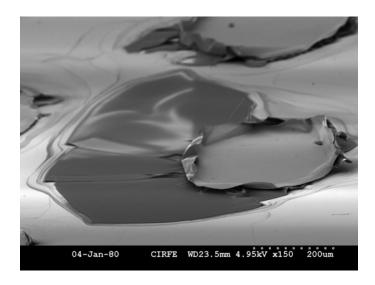

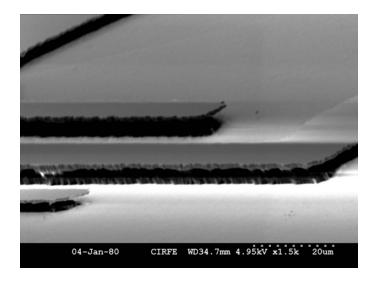

| 5.5  | SEM image of trapping wires of Chip 1                                                    | 59 |

| 5.6  | SEM image of kinks in wires of Chip 1                                                    | 60 |

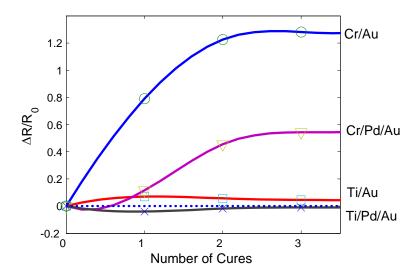

| 5.7  | Change in resistance in centre wire after subjecting to polyimide cure cycles for Cr/Au, |    |

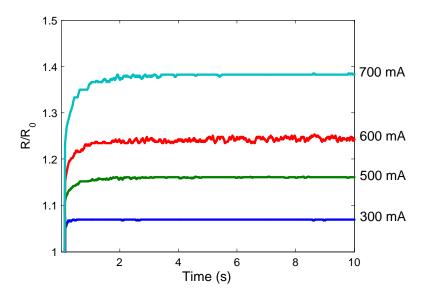

|      | Ti/Au, Cr/Pd/Au and Ti/Pd/Au metallizations                                              | 61 |

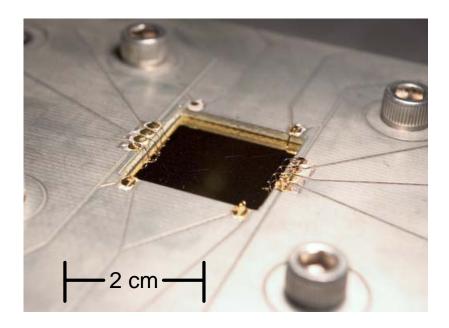

| 5.8  | Test stage for atom chips                                                                | 62 |

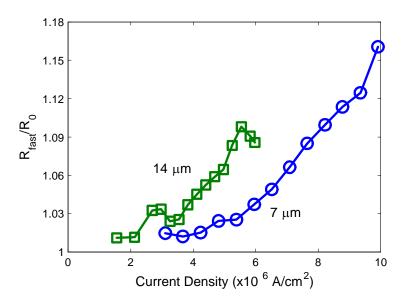

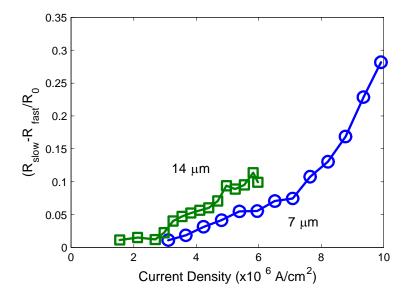

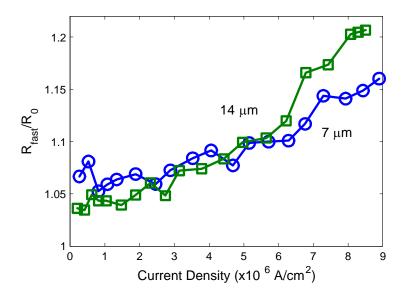

| 5.9  | Change in resistance due to fast heating for Cr/Au wires of Chip 1                       | 64 |

| 5.10 | Change in resistance due to slow heating for Cr/Au wires of Chip 1                       | 64 |

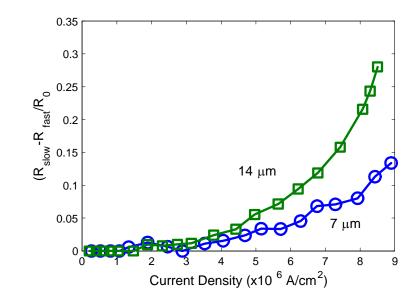

| 5.11 | Change in resistance due to fast heating for Ti/Pd/Au wires of Chip 2                    | 65 |

| 5.12 | Change in resistance due to slow heating for Ti/Pd/Au wires of Chip 2                    | 66 |

| 5.13 | Change in resistance due to slow heating for Ti/Pd/Au centre wire of Chip 2 with         |    |

|      | current through all wires.                                                               | 66 |

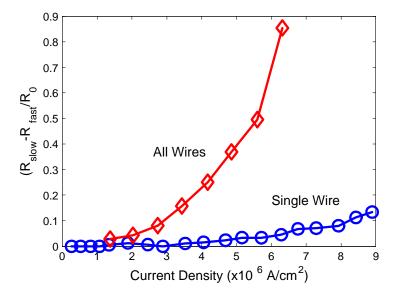

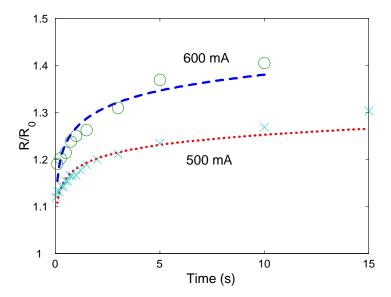

| 5.14 | Change in resistance as a function of heating time for centre wire of Chip 1             | 67 |

|------|------------------------------------------------------------------------------------------|----|

| 5.15 | Change in resistance as a function of heating time for centre wire of Chip 2             | 68 |

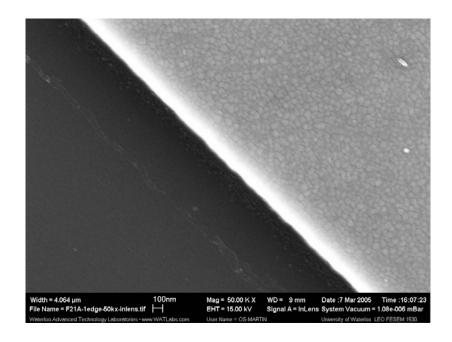

| 5.16 | SEM image of a Chip 1 wire edge at $50,000 \times \text{magnification}$                  | 69 |

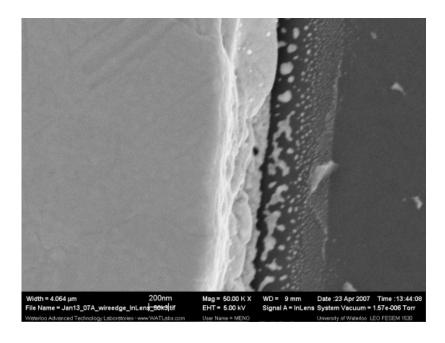

| 5.17 | SEM image of a Chip 2 wire edge at $50,000 \times \text{magnification}$                  | 69 |

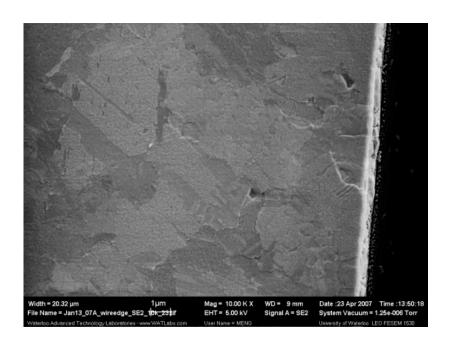

| 5.18 | SEM image of a Chip 2 wire edge at $10,000 \times \text{magnification}$                  | 70 |

| 5.19 | AFM image of surface of a Chip 2 wire                                                    | 70 |

| 5.20 | Patterning of polyimide planarization layer                                              | 72 |

| 5.21 | Planarization with a single layer of T-512B spin-on glass                                | 73 |

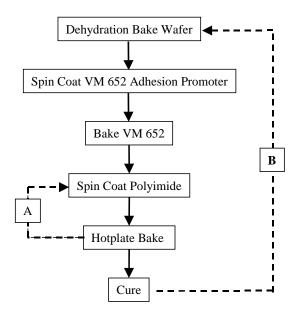

| 5.22 | Application process for PI 2562 and PI 2611                                              | 75 |

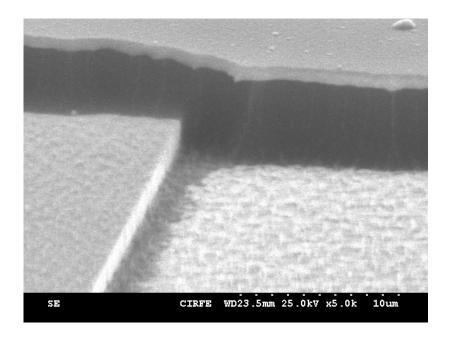

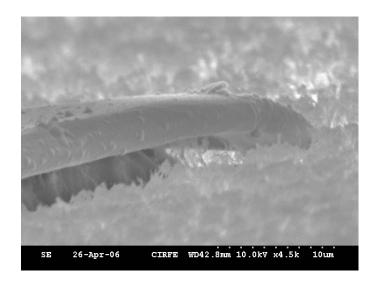

| 5.23 | SEM image of edge of polyimide planarization layer with Al etch mask                     | 82 |

| 5.24 | Process for eliminating holes etched through polyimide film                              | 83 |

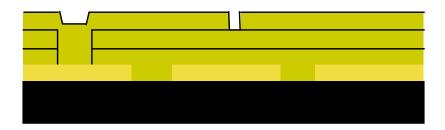

| 5.25 | Cross section of three layers of polyimide                                               | 84 |

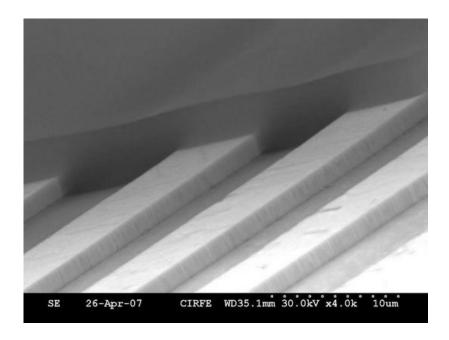

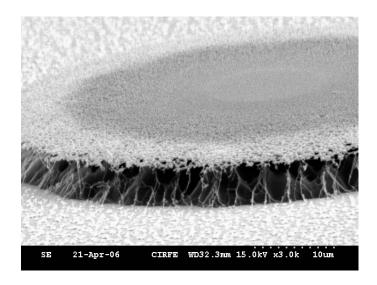

| 5.26 | SEM image showing etched-back polyimide film                                             | 85 |

| 5.27 | SEM image showing etched-back polyimide film over centre trap wires to demonstrate       |    |

|      | planarization                                                                            | 86 |

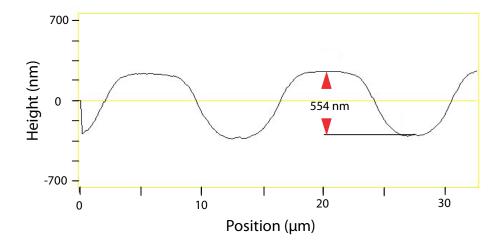

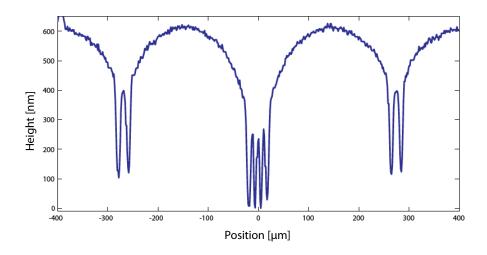

| 5.28 | Dektak profilometer scan of polyimide surface over five centre wires                     | 86 |

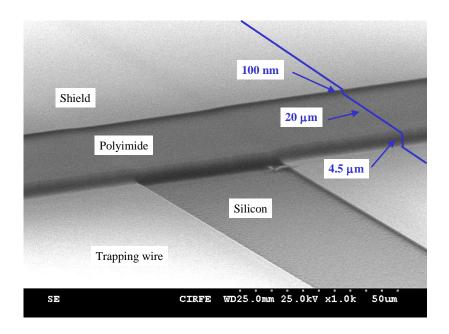

| 5.29 | SEM image of edge of shield and polyimide layers of Chip 2                               | 88 |

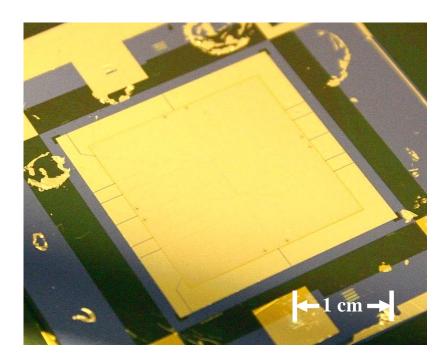

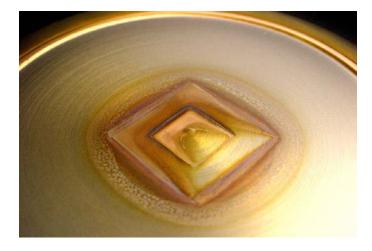

| 5.30 | Image of a fabricated Chip 2 with patterned polyimide and shield layer                   | 89 |

| 5.31 | SEM image of silver-filled Epotek H77 epoxy used to connect shield layer to ground       |    |

|      | pads                                                                                     | 89 |

| 5.32 | SEM images of thermally deposited Au (with Cr adhesion layer) over PI 2562. $\ \ldots$ . | 90 |

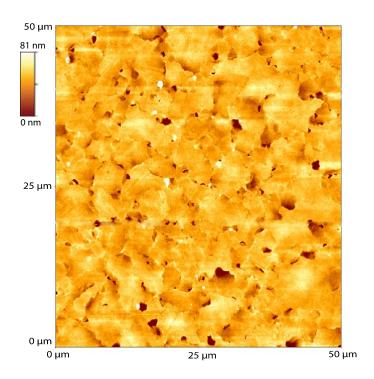

| 5.33 | AFM scans of Au films on polyimide                                                       | 92 |

| 5.34 | RMS roughness of thermally deposited Au on polyimide (with Cr adhesion layer) for        |    |

|      | four thicknesses.                                                                        | 93 |

| 5.35 | SEM image of $100\mathrm{nm}$ Au layer on polyimide                                           |

|------|-----------------------------------------------------------------------------------------------|

| 5.36 | Chip 1 mounted to Macor block                                                                 |

| 6.1  | "Reverse Fabrication" method to attain a single crystal Au shield layer 99                    |

| 6.2  | Connecting a Au electrode to underlying Au using via etched through polyimide 100             |

| 6.3  | Absorption image of $^{87}\mathrm{Rb}$ atoms magnetically trapped with macroscopic Z-wire and |

|      | external field coils                                                                          |

## Chapter 1

## Introduction

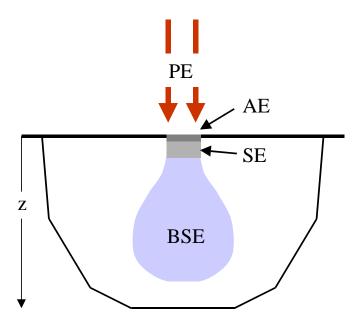

A Rydberg atom has a single electron excited to a state with a high principal quantum number, n [1]. The size of a Rydberg atom scales as  $n^2$ , and likewise the electric transition dipole moment to energetically similar states. Close to a metal surface, a Rydberg atom generates a surface charge that arranges to mimic an image of the atom. Dipole-dipole interactions between Rydberg atoms and their "image charges" shift and broaden the atomic energy levels through perturbations of the Rydberg electron wavefunction [2]. Since it is highly excited, the Rydberg electron is loosely bound. At short atom-surface distances it may be stripped from the atom through an attraction to its image (creating an ion).

Previously, the interactions between Rydberg atoms and metal surfaces have been studied using thermal atomic beams [3]. These collimated beams are optically excited to Rydberg states and intersect the surface at near-grazing incidence. By measuring ion signal as a function of applied electric field, atom-surface distance may be inferred. However, as the Rydberg atom moves towards the surface it undergoes a complex interaction with the surface. As a result, the character of the Rydberg wavefunction changes significantly before ionization [4]. As this wavefunction character is thought to significantly influence the ionization event, this situation is not ideal.

Magnetic microtraps, or "atom chips", offer an alternate method of studying Rydberg atoms close to a surface. An atom chip uses current-carrying wires, microfabricated on a substrate, to form

a magnetic potential minimum above the chip's surface [5]. Weak field-seeking atoms are attracted to the minimum and thus contained. Control over the location of the potential minimum, and the gradient and curvature around it, allows one to accurately manipulate the position and size of the trapped atom cloud. Therefore, the distance between the atoms and the surface of the chip is well-defined and controllable, in contrast to Rydberg atom-surface interaction experiments which employ thermal beams. We plan to use an atom chip to magnetically trap  $^{87}$ Rb atoms and bring them close (within  $\mu$ m) to the chip's metal surface. There they will be excited to Rydberg states, and we will study shifts and/or broadenings of the spectral lines to probe surface interactions. Although the Rydberg atoms will not be trapped, the timescale of the interactions and spectroscopy is less than that of the thermal expansion of the atomic cloud.

Atom chips have been used as tools for: creating Bose-Einstein condensates (BEC<sup>1</sup>); manipulating atoms with guides; beamsplitters and "conveyor belts"; splitting and recombining clouds of atoms for interference studies; and many other experiments with integrated atom optics [6], [7]. However, to this date there has been little crossover between a Rydberg atom physics and atom chips<sup>2</sup>.

In this thesis, I describe in detail the fabrication of atom chips intended for the study of Rydberg atom-metal surface interactions. Two designs of atom chips have been fabricated. Chip 1 is a simple design, used to gain experience with magnetic trapping techniques. Chip 2 is a multi-layer design, specialized for studying interactions between a Rydberg atom and its metal surface. This thesis is intended as a comprehensive guide to the fabrication of the chips. Specific details of the design of the atom chips will be found in a fellow graduate student Jeff Carter's M.Sc. thesis [9]. His thesis will also contain a discussion of the laser cooling and trapping scheme, preliminary magnetic trapping and trapped atom imaging.

The thesis is divided into six chapters. Chapter 2 gives a background of magnetic trapping and atom chips. It then offers an overview of Rydberg atoms and their interactions with metal surfaces, including the effects of randomly distributed "patch potentials". Growth and diffusion mechanisms of thin films are also discussed. Chapter 3 is an overview of the relevant methods and

<sup>&</sup>lt;sup>1</sup>A list of acronyms is found in Appendix I.

<sup>&</sup>lt;sup>2</sup>An atom chip for trapping Rydberg atoms has been proposed by Mozley et. al. [8].

devices that are used in atom chip fabrication. This includes thin film deposition, patterning with photolithography, and planarization. It concludes with metrology techniques (surface profilometry and scanning electron microscopy) used to characterize microfabricated devices. Chapter 4 presents the design of the two atom chips. The chapter begins with an overview of the experimental setup to illustrate the role of the atom chips in the planned Rydberg atom-surface studies. The design and fabrication method of each layer of the chips is given, supported by a summary of methods used by other groups. Detailed methods of the fabrication of Chip 1 and Chip 2 are given in Chapter 5. In addition, it includes measurements of important aspects of the fabricated chips, including thermal properties, wire edge roughness, planarization and grain structure and roughness of the top surface. The thesis concludes with a summary and a discussion of possible continuing work on this project.

# Chapter 2

# Background

#### 2.1 Atom Chips

#### 2.1.1 Magnetic Trapping

A particle with spin and a magnetic moment  $\mu$  interacts with a magnetic field **B** by the potential [10]

$$V_{mag} = -\boldsymbol{\mu} \cdot \mathbf{B}. \tag{2.1}$$

The polarity of the interaction depends on whether or not the particle is in a strong or weak field-seeking state (with the particles's magnetic moment aligned parallel or anti-parallel to the applied field). A magnetic field minimum can form a trap for neutral atoms in the weak field-seeking state by taking advantage of this interaction.

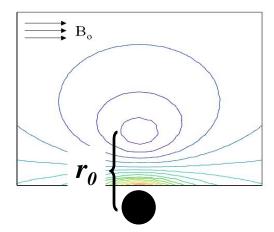

A simple two-dimensional trap can be formed by combining the field from a straight currentcarrying wire with a homogeneous perpendicular bias field generated, for example, by a pair of Helmholtz coils [11]. At a certain distance from the wire,  $r_0$ , the two fields will cancel, resulting in a line of zero field parallel to the wire at

$$r_0 = \frac{\mu_0 I}{2\pi B_b} \tag{2.2}$$

Figure 2.1: Trapping potential formed by a wire carrying current (out of page) and a homogeneous bias field  $(B_0)$ .

where I is the current in the wire and  $B_b$  is the magnitude of the bias field (see Figure 2.1). The position of  $r_0$  can be controlled by varying I and  $B_b$ , allowing for precise positioning of the trapped atoms. Near  $r_0$  the gradient of the resulting field is [6]

$$\nabla B = \frac{2\pi B_b^2}{\mu_0 I} = \frac{\mu_0 I}{2\pi r_0^2}.$$

(2.3)

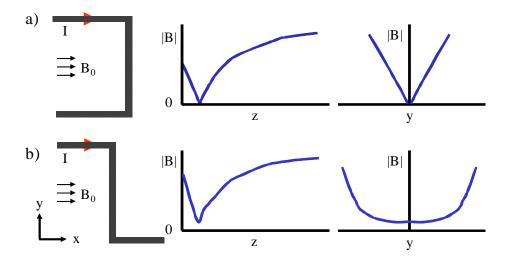

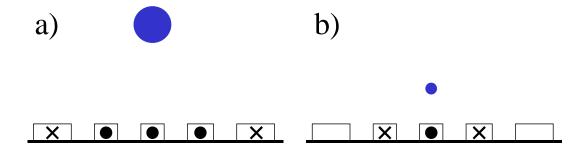

With a straight wire and a bias field, atoms are guided in just two dimensions, with no axial component to the potential. By bending the ends of the wire to form a U or Z, atoms can be trapped in all three-dimensions, with the bent sections contributing field components orthogonal to the bias field [5] (see Figure 2.2).

When trapping atoms, a field zero is not desirable, since atoms can spin-flip into the untrapped strong field-seeking state when passing near or through the zero. These are known as Majorana spin-flips. For a straight wire guide, adding a homogeneous axial field raises the trap minimum to form an Ioffe-Pritchard trap. Conventionally, this field is labelled  $B_{IP}$  and it converts the potential around the trap minimum from quadrupolar to harmonic. For a U-trap, the fields from the two bent ends cancel at the trap centre and give a field-zero. A Z-trap, however, naturally forms a Ioffe-Pritchard trap and an additional  $B_{IP}$  can further lift the minimum. The trapping potentials of U- and Z-wire

Figure 2.2: Configurations of a) U-wire and b) Z-wire traps and corresponding trapping potentials in the z and y planes.

traps are shown in Figure 2.2.

The harmonic Ioffe-Pritchard trap formed by a wire and an axial  $B_{IP}$  – neglecting any effects of the ends of the wires – can be characterized by the curvature in the radial direction. The radial oscillation frequency about the trap minimum,  $r_0$ , is [6], [7]

$$f = \frac{B_b^2}{I} \frac{2\pi}{\mu_0} \sqrt{\frac{\mu}{MB_{IP}}} = \frac{B_b}{r_0} \sqrt{\frac{\mu}{MB_{IP}}}$$

(2.4)

where M is the mass of the atom and recalling that  $\mu$  is the magnitude of the atom's magnetic moment. The size of the trap decreases with increasing oscillation frequency. With the wire ends bent, the axial trap resembles a waveguide with sharp rises in the field near the wire kinks.

Magnetic trapping must be performed in an ultra-high vacuum (UHV) environment on the order of  $10^{-10}$  -  $10^{-9}$  Torr in order to minimize collisions between trapped atoms and the background gas. Traps are most commonly loaded from a source of laser cooled atoms such as a magneto-optical trap (MOT) [12]. Atoms chosen for magnetic trapping are therefore those that are easily optically cooled, commonly alkalis.

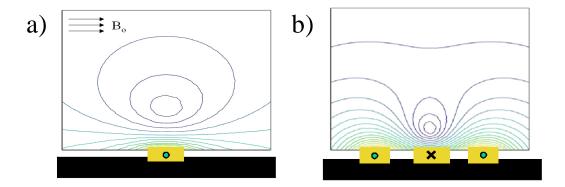

#### 2.1.2 Miniaturization

The maximum trap gradient,  $\nabla B$ , for a wire with radius  $r_0$  is at a distance  $r_0$  from the wire surface. Therefore, from Equation 2.3,  $\nabla B \propto j$ , where j is the current density in the wire [13]. The achievable current density scales inversely with wire radius, favouring miniaturization. Fabricating the wires on a substrate allows for extremely small wires and further increases the maximum current density by improving heat transport, as first proposed by Weinstein et al. [10] in 1995. The first substrate-based magnetic traps were fabricated by Drndić et al. [13] (1998), Reichel et al. [5] (1999), and Folman et al. [14] (2000), with the latter group introducing the term "atom chip". These chips were made using the established metal deposition and lithography techniques used in semiconductor manufacturing (see Section 3). A diagram of the potential formed by an atom chip wire and external bias field is shown in Figure 2.3a.

Miniaturization allows for a high degree of accuracy in positioning trapped atoms. Complex trap geometries with multiple wires can also be realized, giving the ability to transport, split and merge collections of atoms<sup>1</sup>. Shortly after successes with magnetically trapping with wires on a substrate, the first Bose-Einstein condensate (BEC) was created using an atom chip in 2001 [16], [17]. Since then, atom chip-based experiments have expanded to include BEC interferometry and diffraction, double-well potentials and single atom detection.

More complex traps can be formed by crossing wires. Lev [15] explains the multiple uses of a grid of wires for forming U-, Z- and H-shaped configurations as well as "gates" for transporting atoms. Reichel *et al.*[5] introduced the "atomic conveyor belt", which uses a corrugated wire on each side of the main guide wire to transport atoms over a distance of millimetres.

In many cases, the external coils that generate the bias field can be replaced by additional wires on the chip to form tighter traps close to the surface (Figure 2.3b). An added advantage of this is that the orientation of the fields is accurately fixed, simplifying the positioning of the trap. Also, the microfabricated wires have a much lower inductance than macroscopic external coils and can therefore be switched off and on more quickly.

<sup>&</sup>lt;sup>1</sup>Excellent reviews of atom chip design, fabrication and experiments have been written [6], [7], [15].

Figure 2.3: Trapping potentials for a) single wire and external bias field, b) three wire guide.

As the applications of atom chips progress, so too does the need for advanced fabrication techniques. As will be discussed throughout this thesis, the thermal properties of the substrate, roughness of the wires, and smoothness and reflectivity of the chip surface can be extremely important in atom chip experiments.

#### 2.1.3 Losses and Fragmentation

Many loss mechanisms come into play when magnetically trapping atoms with chips. Atoms can be lost from the trap due to Majorana flips, collisions with the background gas or other trapped atoms, or tunneling and noise induced spin flips to untrapped states [6]. Another significant cause of loss is interactions between the trapped atoms and noise in the electromagnetic field due to the vicinity of the chip. This noise is caused by thermally induced currents in the chip surface [18] and, to some degree, shot noise in the current carrying wires.

Random thermally-induced currents in the surface material cause fluctuations in the electromagnetic field. These fluctuations can cause spin-flips in the trapped atoms, leading to a decrease in trap lifetime. The loss rate is dependant on the skin depth of the material at the Larmor frequency of the trapped atoms  $(\delta)$ , the thickness of the surface (d) and the atom-surface distance (y). This

loss rate,  $\gamma$ , is approximated to be [19]

$$\gamma \propto \frac{d}{\delta^2 y^2}, \quad d \ll y \ll \delta$$

(2.5)

for thin films. Various experiments have been performed to measure trap losses due to surface proximity using both ultracold clouds and condensates [20], [21], [22], [23].

When first cooling trapped atoms to BEC near metal surfaces, it was observed that the cloud was not uniform and was instead fragmented into smaller clouds [20], [24], [25]. The severity of the fragmentation was found to depend on the average distance between the cloud and the surface by Fortágh et al. [20] and was caused by irregularities in the magnetic field [24]. The dominant cause of roughness in the magnetic field is deviations in the current flow in the trapping wires. Roughness in the wire edges and surface causes the current to stray from a straight path, generating a corrugated axial component to the magnetic field [26]. Wire edge and surface roughness is a result of the fabrication method, and it can be minimized with advanced techniques [27] (see Section 4.3.3).

#### 2.2 Rydberg Atoms Near Metal Surfaces

The size of a Rydberg atom scales as  $n^2$ , as measured by Fabre *et al.* [28], which causes exaggerated behaviour. Rydberg atoms are extremely sensitive to electric fields since the excited electron is so loosely bound. The polarizability of Rydberg atoms scales as  $n^7$  and therefore modest fields can strongly perturb Rydberg energy levels through Stark shifts, or even ionize the atoms [1]. Therefore, Rydberg atoms are ideal probes of small variations in electric fields [29]. Due to the separation between the Rydberg electron and the core, the electric transition dipole moment is large and scales with the separation.

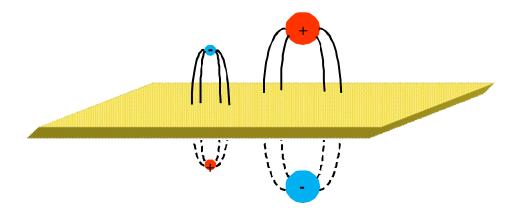

Near a metal surface, the Rydberg electron and ion core generate a charge distribution over the surface with an electric field that mimics that from a corresponding positive and negative image charge embedded in the metal (Figure 2.4). The Rydberg electron is attracted by its image through a dipole-dipole interaction, and at close enough distances the electron can be stripped from the atom

Figure 2.4: Diagram of electric field from Rydberg electron and ion core and corresponding image charges.

by field ionization [28]. The distance at which ionization occurs is [30]

$$r = 3.8n^2 a_0 (2.6)$$

where  $a_0$  is the Bohr radius.

At greater atom-surface distances, the interaction between the Rydberg atom and its image leads to a perturbative energy level shift known as the Lennard-Jones shift [31]. At intermediate distances the orientation of the Rydberg atom with respect to the surface becomes important [30]. States where the electron is most often between the core and the surface ("red" states) experience greater broadenings than states where the electron is on the opposite side of the core form the surface ("blue" states). However, as the surface is approached a particular energy level may alternate from red to blue and back due to state mixing and avoided crossings from surface induced perturbations. Therefore, a high degree of control over atom-surface distance is required, which can be realized with magnetic trapping using an atom chip.

A polycrystalline material has grains with random crystal orientations with respect to the surface. Difference in the work function between the grains generate electric fields that may have effects on Rydberg atoms that overshadow other atom-surface interactions. The effect of "patch fields" has been observed in studies of gravitation [32], [33] and ion trapping [34], [35]. This effect can be

modelled as a random distribution of square patches of width w with an average potential  $\Phi_{rms}$ . Above a planar surface the rms electric field is approximately<sup>2</sup>

$$E_{rms} = 0.33 \left(\frac{\Phi_{rms}}{w}\right) \left(\frac{w}{r}\right)^2, \quad r \gg w$$

(2.7)

where r is the atom-surface distance. The Stark shift in Rydberg states caused by this electric field is

$$\langle \delta W \rangle = -\frac{1}{2} \alpha \langle E^2 \rangle = -\frac{1}{2} \alpha E_{rms}^2$$

(2.8)

and therefore is dependent on  $w^2$  and  $1/r^4$ . For a given separation between an atom and a polycrystalline surface, reducing the grain size is favourable for minimizing Stark shifts due to patch potentials.

#### 2.3 Thin Film Growth and Structure

#### 2.3.1 Physical Vapour Deposition

A common method of growing a thin film is by evaporating or sputtering material from a bulk source and allowing it to condense on a cooler substrate (see Section 3.2). The condensed particles adsorb to the surface and form nuclei at sites where the binding energy is high [36]. As the nuclei grow, they coalesce into islands with a particular crystal orientation [37] that grow further to form grains that intersect with each other through grain boundaries. Grains boundaries migrate by diffusion and may grow into one another in order to reduce surface area, thereby reducing the boundary energy [38].

The material properties of thin films depend strongly on the growth conditions (temperature, rate, thickness) and post-growth treatment such as annealing. Grain size is known to increase with thickness and temperature during deposition [37] and with annealing [38]. Surface roughness increases with film thickness, but decreases with annealing temperature.

<sup>&</sup>lt;sup>2</sup>Calculated by Dr. J. D. D. Martin

#### 2.3.2 Interdiffusion

Highly conductive metals, such as Au, have low reactivity with other materials and often require an intermediate layer that is reactive with both the substrate and the conductive layer. These adhesion layers are commonly Cr and Ti, which function well as long as the films are not subjected to subsequent high temperature processes. At elevated temperatures these films can interdiffuse, often with considerable changes to material properties such as resistivity, adhesion, and stress [39]. In designing and fabricating metallized microelectronic devices, diffusion must be taken into account when higher temperature processes are required. For an infinite source, the rate of diffusion is governed by [36]

Rate

$$\propto \exp\left(-\frac{Q}{kT}\right)$$

(2.9)

where Q is the activation energy, k is Boltzmann's constant and T is the temperature.

Diffusion processes between various adhesion layers and gold have been studied extensively by: measuring resistivity changes in the film [40], [41]; resistivity and surface profiles at the interface between layers [42]; surface imaging with electron microscopes and atomic force microscopes [40], [41], [43]; and depth profiling using Rutherford backscattering [44].

Since thin films consist of grains, grain boundaries and dislocations, interdiffusion is not uniform across the interface between two thin films. The bulk of diffusing material has been found to preferentially travel through grain boundaries until reaching the surface [39]. This process continues until the diffusing lower layer is depleted and the bulk of the diffusing material has accumulated at the surface. Materials such as chromium and titanium form oxides on or near the surface [40], [43].

The use of an intermediate buffer layer between the adhesion and conducting layers is commonly used to reduce interdiffusion and has been studied for various film combinations including Ti/Pd/Au [44], NiCr/Pd/Au [45], and Ti/Pt/Au [46].

## Chapter 3

# Fabrication Methods, Materials and Devices

This chapter introduces the relevant methods that are used to fabricate atom chips. It begins with methods of coating substrates with thin films of polymers and metals through spinning, evaporating and sputtering. Next, photolithographic patterning of these films is explained, followed by methods of attaining planar surfaces above them. Finally, it ends with a description of devices used to characterize topography and surface properties of microfabricated films and structures. This chapter is intended as a general overview of the important aspects of fabrication. Specific recipes are given in the following chapters.

## 3.1 Spin Coating

Spin coating is a method of applying a thin, uniform layer of material (often organic) across the surface of a wafer. The material is usually dissolved in a solvent, with the concentration determining the viscosity. The liquid is dispensed onto the wafer surface using a syringe, a pipette, or by pouring. The wafer is spun between 500 and 5000 RPM and the centrifugal force causes the liquid to spread out radially over the surface, with the excess flung from the wafer edge. The wafer is then baked to

Figure 3.1: Typical spin curve plotting spun thickness vs. spin speed [48].

drive off the solvent and harden the film.

The thickness of the film depends on the spin speed and the viscosity of the liquid. Spun and baked photoresist, for example, is most commonly 500 nm to 5  $\mu$ m. Thick film resists and materials such as SU8 can be spun in a single layer, tens of microns thick, or much thicker with multiple layers [47]. The dependence of the thickness of a spun material, t, to spin speed,  $\omega$ , is characterized by a spin curve, as illustrated in Figure 3.1.

#### 3.2 Metallization

Metal films can be grown on a surface physically (vapour deposition) or chemically (electroplating, see Section 3.3.3), depending on the requirements of the film or the fabrication process.

#### 3.2.1 Evaporation

The simplest method of growing a metal film is by evaporating a small amount of metal, either resistively or with an electron beam, and allowing it to deposit on the sample [36]. Keeping the system at low pressure ( $< 10^{-5}$  torr) minimizes the presence of background gas, increasing the mean free path of the metal particles and avoiding contamination of the film. Therefore, evaporated metal does not coat the sidewalls of vertical features (low step coverage).

In a typical thermal evaporator, a crucible containing the source of metal (charge) is placed in a tungsten coil which is resistively heated. The current passing through the tungsten wire determines the crucible temperature and thus the rate of evaporation. Film deposition rate and thickness is monitored using a quartz crystal oscillator which decreases in resonant frequency as material is built up on its surface (Section 5.2.3).

The advantage of this system is that it is simple, and affordable to operate and maintain. There are, however, several disadvantages. Deposition rate is highly dependent on the thermal contact between the coil and crucible and on the surface area of the charge, making results for a given current and time inconsistent from run to run. Additionally, radiation from the hot charge, crucible and coil can cause unwanted heating of the substrate.

Electron beam deposition systems use a focussed beam of electrons to heat just the top surface of the charge. Deposition rates are much more consistent than resistively-heated evaporators, since the evaporation of the charge is controlled by the electron beam spot size and the intensity [49]. While heating of the substrate due to thermal radiation is much less in electron-beam systems, films can be damaged by high energy electrons from the electron gun.

It is often useful to deposit layers of more than one type of material. With a resistive evaporation system, each charge must have a separate current source, usually powered with a switchable transformer. In an electron beam evaporator, a charge does not require an external electrical connection, so each crucible can be moved into the path of the beam when needed.

With both evaporation methods the deposited film thickness is not uniform across the sample. If the evaporating material is considered to emit from a point source, the arrival rate across the sample decreases with  $\cos^3\theta$  for a given perpendicular charge-sample distance, L [50], with  $\theta$  defined in Figure 3.2. This effect limits the surface area that can be uniformly coated and thus the number of samples that can be coated simultaneously. Simply placing the sample or samples further from the source decreases the angle to improve uniformity, however more material is wasted to the walls of the chamber. A solution for coating multiple wafers is to place them on a rotary or planetary stage, offset from the source so that each wafer passes directly over the source multiple times during

Figure 3.2: Geometric non-uniformity in evaporated film thickness.

the deposition [49].

#### 3.2.2 Sputtering

An alternate method of thin film deposition is by sputtering material from a target using energetic ions [36]. When ions bombard a surface, many interactions can occur including scattering, dislocations, ion implantation, and electron emission. As well, impacting ions can cause a collisional cascade of atoms in the material. If atoms near the surface collide with energies greater than the surface binding energy, atoms can be ejected from the surface [50]. Sputtering systems put several kV between two plates in a chamber with Ar or Xe gas at pressures between  $10^{-1}$  and  $10^{-2}$  torr in order to form a plasma. The target, a high purity plate of the material to be sputtered, forms the cathode and particles of the ionized gas are accelerated towards it (Figure 3.3).

For sputtering metals, a dc potential is sufficient. Insulators, however, quickly build up a surface charge in a dc field and rf potentials are required instead.

Due to the high pressures required to form a plasma the mean free path of the sputtered particles is quite low ( $\sim 1 \,\mathrm{mm}$ ) [36]. Particles arrive at the substrate at a large range of angles giving a high

Figure 3.3: Diagram of a parallel plate sputtering system.

degree of step coverage. Sputtering is therefore preferable to evaporation for coating over features with topography.

Sputtering has other advantages over thermal/electron beam deposition. Sputtering systems can be very compact with simple turn-key operation. Deposition rates are consistent from coating to coating. Material properties of the film (grain size and structure, stress) can be consistently controlled by varying chamber pressure, deposition rate and substrate temperature [51]. Alloys and mixtures of two or more metals can be sputtered, with the ratio between species in the sputtered film matching the target composition.

A disadvantage of sputtering is that deposition rates are much slower than thermal evaporation. The bombarding ions dissipate most of their energy into the target, causing heating. The heating sets a maximum on ion energy, which limits the sputtering rate. Another disadvantage of sputtering is that the step coverage, while useful in some situations, is detrimental to lift-off photolithography (Section 3.3.3). The sputtered film coats the sidewalls of the photoresist (high step coverage), making chemical access difficult and giving rough feature edges.

Figure 3.4: Workflow for patterning photoresist.

#### 3.3 Photolithography

#### 3.3.1 Photoresist

Photolithography is the basis for nearly all microfabrication technology as the means of transferring patterns to a substrate. A photosensitive material is exposed to a light field shone through a mask that contains a replica of the desired pattern [48]. Typically, this material is an organic polymer, known as "photoresist", that is sensitive to ultraviolet radiation. It is applied to the substrate (wafer) by dropping a small amount onto the surface and spinning at a high rate to give a uniform layer (Section 3.1). The resist is then baked to drive off solvents and exposed for a set amount of time to UV light shone through a mask. After exposure the resist is developed, leaving resist matching the pattern on the mask. Figure 3.4 shows the typical process for patterning photoresist.

Photoresist can be one of two tones, 'positive' or 'negative', which differ depending on how light influences the polymer. Positive photoresists are relatively insoluble in resist developer unless

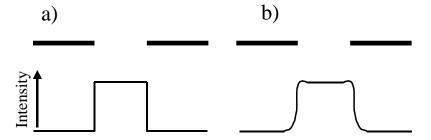

Figure 3.5: Intensity at the surface of photoresist when exposed through a mask with a) no diffraction and b) with diffraction.

Figure 3.6: a) Positive-slope profile of positive photoresist. b) Negative-slope profile of negative photoresist.

exposed to UV light, which breaks bonds in the polymer structure. Negative resists are soluble in the developer chemicals until exposure promotes cross-linking between polymers.

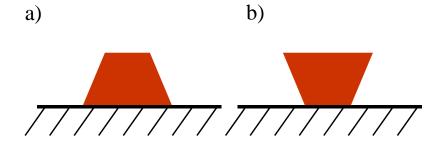

On the scale of typical photolithography features, diffraction plays an important role, broadening the intensity profile after edges on the mask pattern. Consequently, the surface of the photoresist does not receive a spatially uniform dose (Figure 3.5). This effects the edge profile (sidewall) of the resist. A positive resist exhibits a positively-sloped sidewall, since the edge of a feature is exposed to less energy than the centre (Figure 3.6a). The same is true for negative resist, only the falloff in dose at a feature edge results in a negatively-sloped sidewall, known as undercut (Figure 3.6b). It is the polarity and angle of sidewall slope that determines the type of resist best suited for a particular lithographic process.

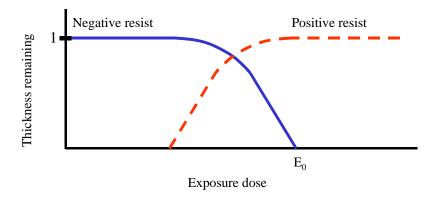

A photoresist has two exposure thresholds, between which the resist only partially develops. A quantitative way to characterize photoresist is by its contrast. Contrast can be determined by

Figure 3.7: Characteristic curve of a negative and positive photoresist showing thickness remaining after development. For a negative resist,  $E_0$  is the dose to clear all resist. For a positive resist,  $E_0$  is the minimum dose required for full resist thickness to remain.

Figure 3.8: Profile of negative photoresist when a) underexposed, b) properly exposed, c) overexposed.

measuring the exposure time to completely remove a positive resist or the exposure at which a negative resist remains after developing, as shown in the characteristic curves in Figure 3.7. The slope of the sidewall, or, in other words, the degree of undercut, also depends on the exposure dose. Figure 3.8 illustrates the degree of undercut for underexposed, properly exposed and overexposed negative photoresist.

#### 3.3.2 Mask Aligner

A mask aligner is a tool for transferring the pattern from a mask to photoresist through UV exposure. Traditionally, the source of ultraviolet light is a mercury vapour discharge lamp. In a quartz bulb a pair of electrodes excite a vapour of mercury causing it to emit a spectrum of radiation [52]. Common photoresists are sensitive to either the 365 nm (i-line) or the 436 nm (g-line) peaks [48]. In many aligners a filter reflects unwanted wavelengths to a heat sink and allows just the i-line or g-line radiation to pass. The light from the mercury discharge lamp is collected by an ellipsoidal mirror and passed to the collimation optics.

Three types of mask aligners are commonly used: contact, proximity and projection [48]. Contact aligners place the mask and wafer in direct contact with each other in order to minimize the effects of diffraction at the edges of mask features. The drawback is that there is a risk of damage to either the mask or the wafer. Also, photoresist may stick to the mask, requiring frequent cleaning of the mask. Proximity aligners leave a small gap between the mask and wafer to avoid problems arising from contact between the two. However, diffraction limits the resolution. A simple projection printing system places optics between the mask and the wafer to focus the ultraviolet light onto the wafer. Currently, most industrial projection printers use reduction optics to shrink the feature size by at least an order of magnitude, from the mask to the wafer, to achieve smaller features.

The position of the mask over the wafer is set by matching alignment marks on the mask with those on the wafer. Two alignment marks can be imaged simultaneously using a split-field microscope. Translation and rotation controls are used to achieve alignment.

#### 3.3.3 Patterning

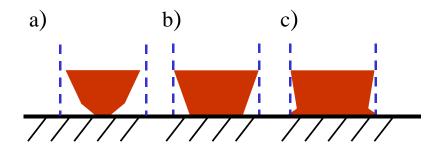

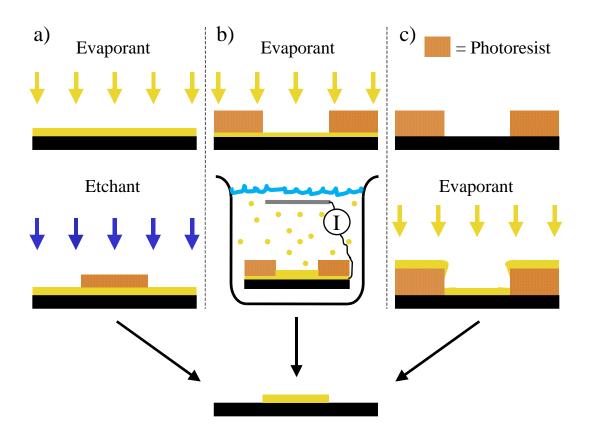

Photoresist is primarily used as a mask for transferring a pattern to a layer or layers of metal, oxide or polymer. Resist can be applied after depositing the layer as a mask for removal, or it can be applied before to define where the layer is grown. Figure 3.9 shows three methods of patterning a wire on a substrate using etching, electroplating and lift-off.

#### **Etching**

The most common method of transferring a pattern from a mask to a layer of material on a wafer is by etching [49] (Figure 3.9a). Positive photoresist is spun over the material and patterned using

Figure 3.9: Three methods of patterning a metal wire: a) etching, b) electroplating and c) lift-off.

a positive-image mask (i.e. opaque where the material is to remain). Positive resist is used because the base of the resist profile matches the features on the mask so they are accurately translated to the etched film (see Figure 3.8a). Once exposed, baked and developed the positive resist is used as a mask to etch the underlying material through either a 'wet' or 'dry' process.

Wet etching involves immersing the wafer in a liquid etchant that is highly selective between the material to be etched and the etch mask (for example, Au is etched in KI and SiO<sub>2</sub> in HF). The etchant is often heated and the wafer agitated to ensure a uniform etch with a consistent rate.

Dry etching includes reactive ion etching (Section 3.5) and ion milling. In both cases ions are accelerated towards the surface and remove material through either chemical or physical processes.

When etching with either wet or dry techniques, it is often necessary to use another material as the etch mask since both the film to be etched and the photoresist may be susceptible to the same etchant. Al and  $SiO_2$  are commonly used as they are both easily deposited and patterned into masks.

Etching can be either isotropic or anisotropic, depending on the material being etched and the method of etching. For example, Si wet etches anisotropically in KOH since the <100> crystal plane etches faster than the <110> plane which in turn etches fast than the <111> plane [49]. Polycrystalline metals wet etch isotropically since there is no bulk crystal orientation to define a preferred etch direction. Isotropic wet etching has a degree of undercut, and sidewalls of an etched film are usually quite rough regardless of the smoothness of the photoresist edge. Roughness can be improved somewhat by optimizing the etchant concentration and temperature, and by using ultrasonic to ensure a constant supply of fresh etchant to the interface [47].

## Electroplating

An alternative metallization process to evaporation and sputtering is electroplating [49]. To electroplate a substrate with a particular metal the substrate is placed in a solution containing metal salts and connected to a current supply as a cathode. The anode is a conducting plate of a dissimilar material. When current is passed between the anode and cathode, positive ions of the metal are

attracted to the cathode substrate and build up a film. To improve film uniformity and adhesion, the substrate is first coated with an evaporated or sputtered seed layer.

To electroplate a pattern, a photoresist or other thick polymer is coated and patterned over the seed layer to form a mold (Figure 3.9b). When placed in the electroplating solution, the film grows to fill the spaces in the mold. After plating, the mold is removed and the seed layer is etched from between the electroplated features.

Unlike sputtering and evaporative deposition, where just a portion of the metal vapour coats the substrate, electroplating builds up metal only where needed and is therefore much more economical. Electroplating also allows for very high aspect ratios, since the film will uniformly fill the resist pattern. Using a resist with smooth, straight sidewalls is necessary.

A drawback of electroplated metal films is surface roughness and grain size [26]. In order to etch the seed layer away, the surface of the electroplated film is also etched and becomes rough. The grain size of electroplated metal is often on the order of microns in diameter, as opposed to  $< 0.5 \,\mu\text{m}$  for typical vapour-deposited films.

#### Lift-off

Lift-off photolithography uses a sacrificial photoresist to mask where a material is to be deposited on the substrate. The photoresist is spun on a clean substrate and patterned to leave gaps defining the required metal pattern (Figure 3.9c). The metal is deposited over the entire patterned wafer and then the resist is chemically removed, leaving a patterned metal film.

In order to have good chemical access to remove the resist, the metal on the resist surface must not be continuous with the metal on the wafer. The photoresist should have a negatively sloped sidewall, requiring a negative-type resist (see Section 3.3.1). Therefore, the photomask must be opaque where the metal is to remain on the chip.

Metallization in lift-off lithography is primarily evaporative, since the low pressures ensure a long mean-free path and a perpendicular flux of metal (Figure 3.10a). The high pressure required for

Figure 3.10: Metal evaporation vs. sputtering in lift-off lithography. Evaporated metal (a) has a high mean-free path and does not coat photoresist sidewalls (poor step coverage). Sputtered metal (b) coats resist sidewalls, making lift-off difficult (good step coverage).

Figure 3.11: Profile of a planarizing material over patterned wires.

sputter coating lowers the mean-free path of the sputtered material, coating the sidewalls of the resist and making lift-off difficult or impossible (Figure 3.10b).

## 3.4 Planarization

Many applications of microfabrication stack multiple layers of material, requiring smooth topography from one layer to the next. Sharp features must be planarized before applying subsequent layers. Planarization methods can be divided into two types: additive and subtractive. Additive methods involve applying material above a layer with topography to get a flat surface. Subtractive methods remove material to transform a non-planar surface into a planar one.

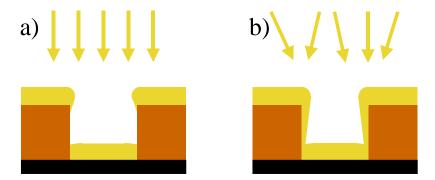

Planarization is quantified by the degree of planarization (DOP), defined as [53]:

$$DOP = 100 \times \left[ 1 - \frac{\Delta h}{h_w} \right] \tag{3.1}$$

where  $\Delta h$  is the deviation in the surface topography and  $h_w$  is the height of the underlying features (Figure 3.11). Degree of planarization can be defined globally across the wafer or locally. For most microfabrication applications local planarization is the most important, since films must be continuous over changes in topography.

The simplest way to planarize is additively, using a spun-on material such as photoresist, polyimide, benzo-cyclo-butene (BCB) or spin-on glass (SOG). These materials exhibit a range of DOP values, with photoresist and SOG being the least planarizing, and polyimide and BCB the most. Photoresist is conformal to the underlying topography and acts simply to smooth sharp edges. Polyimide and BCB are low-dielectric planarizing polymers that are spun on with a range of thicknesses from  $< 1 \,\mu\text{m}$  to  $> 10 \,\mu\text{m}$ . Two important characteristics of a planarizing spin-on layer are flow and shrinkage [54]. Materials that exhibit high flow are better planarizers since the polymers flow over wire edges to fill gaps. When planarizing materials are cured, they shrink as solvents are evaporated, decreasing the flatness of the surface. Polyimides with a high fill content and BCB are therefore better at planarization because they exhibit less shrinkage.

Subtractive planarization methods include chemical-mechanical planarization (CMP) and etch-back. CMP uses abrasives such as SiO<sub>2</sub> in a slurry with a corrosive alkali combined with an absorbent pad rotating pad to remove material from a surface [55]. The wafer sits on a polishing head, which pushes against the pad containing the slurry. The rate and uniformity of material removal is dependent on the type of slurry, the rotation speed, the pressure of the polishing head against the pad, and the temperature. Degree of planarization using a CMP process can be as good as 100%, both locally and globally.

Etch-back planarization combines additive and subtractive methods, and is most often used to obtain a flat oxide or nitride passivation layer [47]. A layer of oxide/nitride is coated with spin-on glass (Section 5.3.1). The SOG acts as a gap-filler and crude planarization layer. A reactive ion

etch (RIE, see Section 3.5) is used to selectively remove material from the surface. By adjusting the etchant gases the ratio of etch rates between SOG and oxide/nitride can be controlled. The bilayer is then etched back until a smooth surface results.

## 3.5 Reactive Ion Etching

Reactive Ion Etching (RIE) combines chemical and physical processes to etch bulk material or patterns in a material defined by a mask [47]. For our process, RIE is necessary for selectively removing material on multilayer chips to expose the underlying trapping wires. Etching takes place in a reaction chamber with an inert gas (such as Ar) at a pressure between  $10^{-2}$  and 1 torr. A potential between two plates generates a plasma in the inert gas, similar to a sputtering system (Section 3.2.2). An etchant gas mixture of gases is injected into the chamber at a controlled rate.

The chemical process is driven by reactions between etchant radicals and the material. Collisions with energized particles in the plasma dissociate the etch gas into reactive species that diffuse through the plasma to reach the surface. There, the radicals adsorb to the surface and chemically react. The reaction products are volatile gases which desorb from the surface to be pumped out of the chamber.

The physical part of the RIE process is similar to sputtering. The potential in the chamber accelerates ions towards the surface of the substrate which sits on the cathode. The bombarding ions drive material from the surface through collisions. Here etch rate is dependant on the kinetic energy of the impacting ions and not on chemical reactions. An etch based entirely on ions is therefore highly non-selective between the material to be etched and the masking material.

Purely chemical processes occur at higher pressures ( $\sim 1\,\mathrm{torr}$ ), where the short mean free path of the diffusing radicals causes isotropic etching. In contrast, purely physical etching occurs at lower pressures ( $\sim 10^{-3}\,\mathrm{torr}$ ) and is much more anisotropic due to the long mean free path. RIE combines these two processes at intermediate pressures by varying free radical and ion concentrations to control etch rates and edge profiles.

Etch gases (O<sub>2</sub>, SF<sub>6</sub>, CF<sub>4</sub>, H<sub>2</sub>, etc.) are chosen based on chemistry between the radicals formed

in the plasma and the material to be etched. The radicals either do not react with the masking material, or react at a much slower rate.

At the lower pressures required to attain straight sidewalls through anisotropic etching a simple parallel plate RIE setup is not efficient at generating a high density plasma. Etch rates are therefore low, since less free radicals are formed. By increasing the potential to generate a denser plasma, the etch becomes more physical and can to lead loss of selectivity and even to sputtering. However, energy can be inductively coupled into the plasma at lower pressures through a coil carrying rf power. This technique is known as inductively coupled plasma (ICP) and is commonly used for low pressure anisotropic etching with high etch rates [50].

## 3.6 Wirebonding

Wirebonding is a method of integrating chip-scale devices with external electrical connections using thin wire or ribbon [56]. Wirebonders use a combination of heat, pressure and ultrasonic energy to form welds between the wires and bond pads, without the need for a solder. The wires, usually Au, Al or Cu, are commonly  $25 \,\mu\text{m}$  in diameter, allowing for many welds in a small area.

The two most common methods of wirebonding are 'wedge' bonding and 'ball' bonding [57]. When wedge bonding, the wire is fed through a hole in the back of the wedge tool and passes beneath the bonding foot of the tool. There, the wire is pressed between the foot of the tool and a bond pad, which may be heated. Ultrasonic energy is applied to the tool to break down surface impurities at the interface between the wire and the bond pad. The mechanism of wedge bonding is as follows:

- 1. Position wedge over first bond pad.

- 2. Press wire between wedge foot and bond pad and apply ultrasonic energy to wedge.

- 3. Lift wedge and kink wire.

- 4. Move wedge to second bond pad while feeding out wire.

- 5. Make second bond.

#### 6. Lift wedge and tear wire.

The most important parameters to wedge bonding are bond force, ultrasonic power and the duration of the power delivery. Each of these can be controlled by the wirebonder. Wire size can vary from  $< 25 \,\mu\text{m}$  to  $> 500 \,\mu\text{m}$  diameter, depending on the power required for the application. Ribbon is also used, which provides a large bond surface for better impedance matching in high frequency applications.

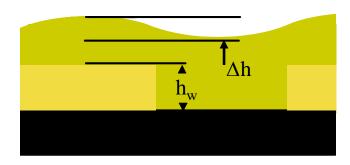

## 3.7 Scanning Electron Microscope

For imaging sub-micron sized features such as the grain structure of the atom chip surface, optical microscopes are no longer sufficient. Electron microscopes replace photons with a beam of electrons to image small features. A scanning electron microscope (SEM) raster scans a focussed beam of electrons across a surface, generating secondary and back-scattered electrons which are re-emitted from the material [58]. As the beam is scanned a portion of these electrons are detected to create a two dimensional image of the surface. SEM can attain images with much more resolution than diffraction-limited optical microscopes.

When a beam of electrons impinges on a surface, elastic and inelastic interactions take place to produce electrons and photons with a range of energies. At the top 1-10 Å, Auger electrons are generated and emitted [59]. Beneath that secondary electrons are formed and, at greater depths, back-scattered electrons. Emitted electrons are detected either off-axis to the incident beam or axially with an in-lens detector.

Most commonly, SEM measures the secondary electrons emitted from the surface at  $< 50 \,\mathrm{eV}$  and back-scattered electrons (energies  $> 50 \,\mathrm{eV}$ ) [60]. Secondary electrons are formed when primary electrons collide with atoms in the surface and lose energy (SE1), or through collisions between atoms and back-scattered electrons (SE2). These atoms emit electrons which have a probability of escaping from the surface of the material. The interaction region has the area of the initial electron beam and

Figure 3.12: Depth profile of interaction regions in SEM to generate Auger electrons (AE), secondary electrons (SE) and back-scattered electrons (BSE) from a beam of primary electrons (PE).

the escape depth,  $z_e$ , of primary electrons is no more than 10 nm, giving secondary electron detection a very high resolution.

Image contrast with SE1 and SE2 electrons is achieved through the dependence of secondary electron yield on the surface topography. At inclined surfaces the incident electrons have a longer path length within the escape depth allowing more secondary electrons to be emitted than at a perpendicular surface. The SE yield has a  $1/\cos\varphi$  dependence with tilt angle,  $\varphi$ . SE2 electrons have an additional material-dependant contrast since the back-scattered electrons that generate them have a probability of reflection that scales with the atomic number, Z [50].

The electron beam is generated either with a filament or by field emission and focussed with a pair of magnetic condenser lenses and apertures [50]. In order to maximize resolution, the astigmatism of the two lenses must be minimized and the two apertures must be aligned.

For the measurements in this thesis I have used two SEMs. The Watlab SEM (LEO 1530, www.smt.zeiss.com/leo) is capable of very high resolution and can be used to image the grain structure of metal surfaces (see Figure 5.16 for an example). The G2N SEM (Hitachi S-3000N,

www.hitachi.com) has lower resolution, but allows for the sample to be tilted up to 90° from horizontal (see Figure 5.6 for an example).

## 3.8 Atomic Force Microscope

An atomic force microscope (AFM) scans a cantilever stylus over a surface and measures the deflection of the cantilever as a result of the force between the stylus tip and atoms in the surface [61]. This information is then used to map the surface topography or other surface features such as magnetic domains [62]. The dominant force used in AFM is from the intermolecular potential that is repulsive at close distances and attractive at larger distances (from van der Waals forces). AFM operates in one of three modes: contact, non-contact and tapping, which are explained below. The cantilever is raster-scanned using x and y-piezos. A laser reflected from the top surface of the cantilever into a position sensitive detector monitors the deflection of the tip [63].

While SEM produces high resolution two-dimensional images, AFM functions in all three dimensions. It is useful in our application for measuring surface roughness and topography.

In contact mode, the tip is dragged across the surface of the sample and the stylus tip is deflected due to the repulsive forces. The topography measurement can be made in either constant height mode or constant force mode. The former scans the tip across the surface and measures the cantilever deflection. The latter employs a feedback loop to keep the tip-surface force constant (i.e. no deflection) by varying a z-piezo. In both cases, an attractive force is present due to capillary action from a thin water layer.

Non-contact mode measures cantilever deflection in the attractive van der Waals regime, tipsurface distances of 50-100 Å. Deflections here are much smaller than in contact mode, so the cantilever is oscillated at its resonant frequency and small variations in resonance from the attractive force are measured instead of measuring deflection directly. Non-contact AFM is useful for soft surfaces that may be damaged by the sharp tip, such as polymer films.

Early AFM styli were made from bonding diamond shards onto glass beams or wires or from

etched wire tips [61], [64]. Today, styli are commonly fabricated from etched Si or Si<sub>3</sub>N<sub>4</sub> with a reflective layer on the backside for optical imaging. The shape of the tip and spring constant of the cantilever is selected for the AFM application. Sharper tips achieve higher resolution for two reasons. First, the narrower width allows them to penetrate deeper into features and the sharper tip has less atoms interacting with the surface. Duller tips are more durable, suitable for larger scan areas. Contact mode uses cantilevers with low spring constants while non-contact mode requires cantilevers with high spring constants for resonant frequencies of hundreds of kHz.

One disadvantage of AFM over SEM is that, while AFM is much more suitable for topographic measurements, SEM images lateral features with more accuracy. The piezos used for raster scanning in AFM have nonlinearity and hysteresis that distort lateral features and when changing scan lengths, one must wait for the piezos to relax before taking an image.

## 3.9 Dektak Surface Profiler

Like an AFM, a Dektak surface profiler is a device for measuring surface topographies. However, it is a simpler device and can scan over larger vertical and horizontal scales. The Dektak, like other profilometers, uses a diamond-tipped metal stylus coupled to a transducer [65]. The sample to be measured sits on a translation stage beneath the tip and, as the sample is scanned, the vertical deflections of the stylus generates an electrical signal. The diamond tips are hemispherical, typically  $12.5 \,\mu\text{m}$  in radius, small enough to measure most microfabricated structures, but blunt enough to minimize scratching soft films such as polymers [66]. Still, the smallest features that can be measured are limited by the tip radius. As an example, to reach the bottom of a groove with a depth of  $1 \,\mu\text{m}$  using a tip with a  $12.5 \,\mu\text{m}$  radius, the edges of the groove must be more than  $10 \,\mu\text{m}$  apart.

## Chapter 4

# Atom Chip Design

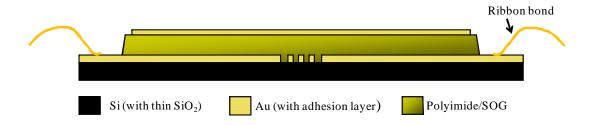

Our Rydberg atom experiments require two atom chip designs to be fabricated, which will be called "Chip 1" and "Chip 2" for the remainder of this thesis. Chip 1 is intended primarily for the development of magnetic trapping, as well as rudimentary Rydberg atom experiments. It consists solely of a set of trapping wires on a substrate. Chip 2 has a metal surface above the trapping wires, separated by a dielectric film. This metal surface is specific to the study of Rydberg atom-surface interactions and has other important uses which are explained in Section 4.5.

To put the role of the atom chips into perspective, this chapter begins with a description of the experimental setup. Following this, the key elements of the chip design are presented along with a review of other groups' work to justify design choices.

## 4.1 Experimental Setup

The atom chip is mounted on a machined Macor block in an ultra-high vacuum (UHV) chamber at a base pressure of about  $1 \times 10^{-9}$  torr. A background of <sup>87</sup>Rb is introduced to the chamber and is cooled and trapped by a magneto-optical trap (MOT) that uses a combination of optical radiation and a magnetic quadrupole field<sup>1</sup>. A conventional MOT uses three pairs of counterpropagating laser

<sup>&</sup>lt;sup>1</sup>A detailed reference for MOTs can be found in [12].

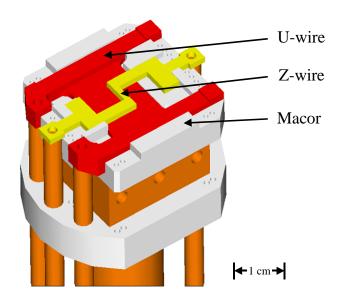

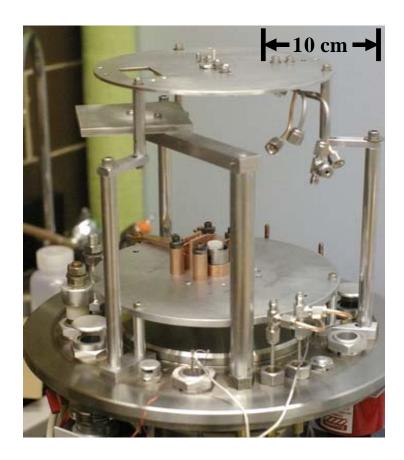

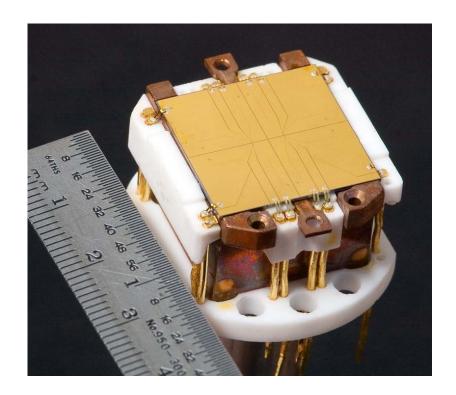

Figure 4.1: Submount for atom chip. Macroscopic U-wire and Z-wire are imbedded in a Macor block.

beams to cool the atoms. However optical access is impeded close (within a few mm) to the chip surface. A solution to this problem is to use the surface of the atom chip to reflect two of the incoming MOT beams. This is known as a reflection MOT, or mirror-MOT (MMOT), a term first used by Reichel *et al.* [5].

The quadrupole field used for the MMOT is formed by combining the fields from two pairs of external coils with a U-shaped copper wire embedded in the Macor beneath the chip (Figure 4.1). The U-wire has a rectangular cross section, optimized for forming a quadrupole field close to the chip's surface, and is based on the design by Wildermuth *et al.* [67].

To load atoms from the MMOT to the magnetic chip trap a process adapted from Kasper et al. [68] is used. The atoms are first optically pumped into a weak field-seeking state and transferred into an intermediate magnetic trap formed by a Z-shaped wire (also embedded beneath the chip) and external coils. The lasers are switched off, leaving a purely magnetic trap. Then the atoms are evaporatively cooled using rf radiation while compressing the trap. The cold atoms that remain are transferred to the chip by ramping down the current in the Z-wire and increasing the currents in the atom chip wires.

Once the atoms have been loaded into the atom chip trap, they can be positioned within a few  $\mu$ m of the chip surface and optically excited to Rydberg states through a combination of lasers and microwave radiation. Interactions between the Rydberg atoms and the surface of the chip can occur, as introduced in Section 2.2. These will be probed using spectroscopy of the initial optical excitation, or by driving further microwave transitions between Rydberg states [69]. Effects of the atom-surface interactions can be detected through selective field ionization (SFI).

## 4.2 Trap Geometry and Layout

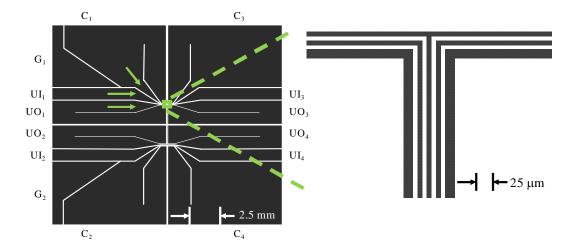

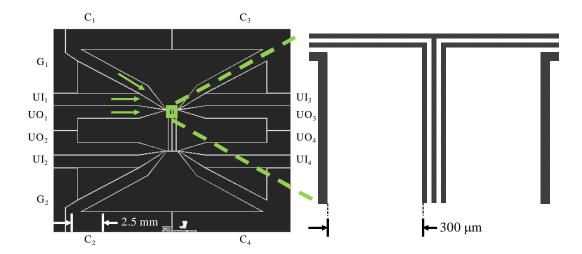

Figure 4.3 and Figure 4.4 show the layout of Chip 1 and Chip 2, respectively. The trapping region is a 4 mm long strip of five parallel wires at the centre of the chip. The centre wire of both Chip 1 and Chip 2 is 7  $\mu$ m wide, sufficiently narrow to form a tight trap close to the wire. It is an H-shaped wire, allowing it to function as either a Z- or U-wire (C<sub>1-4</sub>). A 7  $\mu$ m wide U-shaped wire sits on either side of the centre wire, separated from the centre wire by a 7  $\mu$ m gap (UI<sub>1-2</sub>, UI<sub>3-4</sub>). This pair of wires can be used to generate the bias field when trapping with the centre wire (Figure 4.2b). They can also be used in cooperation with the centre wire to load the chip from the Z-wire trap with the three carrying copropagating currents.

A  $14 \,\mu\text{m}$  wide U-wire neighbours each of the inner U-wires (UO<sub>1-2</sub>, UO<sub>3-4</sub>). On Chip 1 these outer U-wires are separated from the inner U-wires by  $7 \,\mu\text{m}$ . The outer U-wires are used for generating the bias field for loading the atoms from the Z-wire magnetic trap to the chip trap (Figure 4.2a). Chip 2 has an updated design, with the outer U-wires positioned further from the three centre wires (300  $\mu$ m). The larger spacing allows a tighter trap to be formed at distances of > 100  $\mu$ m to facilitate loading the trap from the Z-wire trap. Each of the wires ends in a bond pad at the edge of the chip. The use of the ground pads,  $G_1$  and  $G_2$ , is explained in Section 5.4.

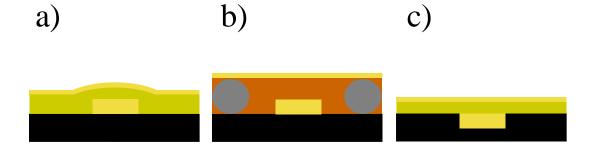

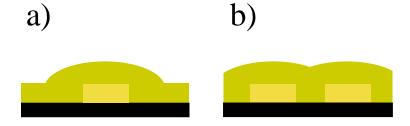

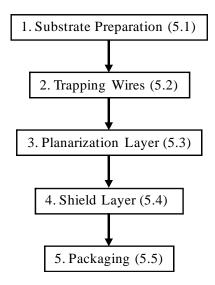

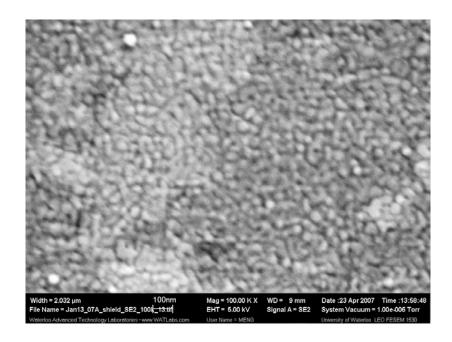

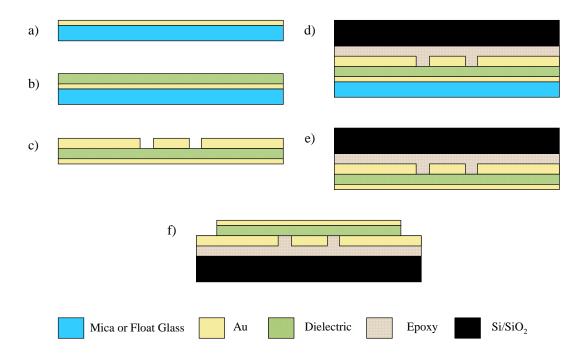

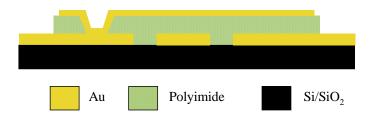

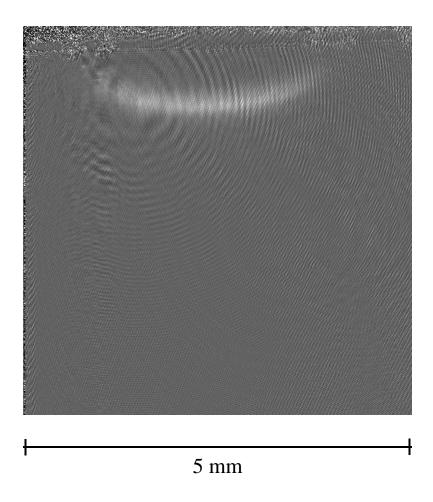

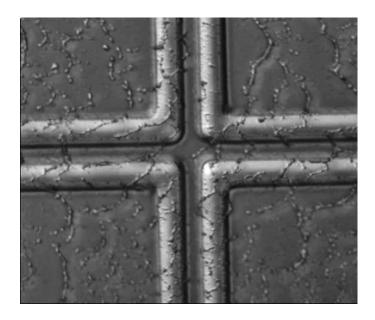

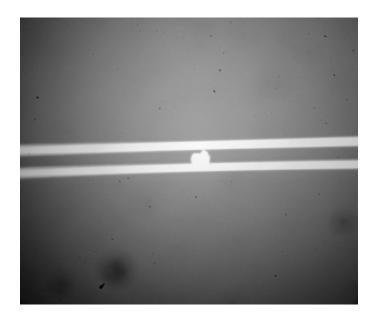

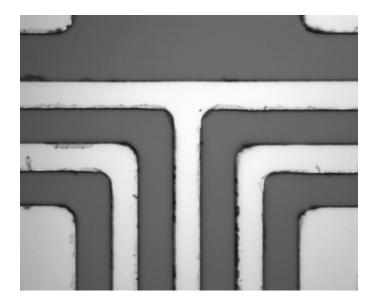

The dimensions of all chips are  $2.02 \times 2.02$  cm, constrained to the largest size that will fit through a 2.75 " Conflat port on the vacuum chamber.