# Active Pixel Sensor Architectures for High Resolution Large Area Digital Imaging

by:

### Farhad Taghibakhsh

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

Electrical and Computer Engineering

Waterloo. Ontario, Canada, 2008

© Farhad Taghibakhsh 2008

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

## **Abstract**

This work extends the technology of amorphous silicon (a-Si) thin film transistors (TFTs) from traditional switching applications to on-pixel signal amplification for large area digital imaging and in particular, is aimed towards enabling emerging low noise, high resolution and high frame rate medical diagnostic imaging modalities such as digital tomosynthesis. A two transistor (2T) pixel amplifier circuit based on a novel charge-gate thin film transistor (TFT) device architecture is introduced to shrink the TFT based pixel readout circuit size and complexity and thus, improve the imaging array resolution and reliability of the TFT fabrication process. The high resolution pixel amplifier results in improved electrical performance such as on-pixel amplification gain, input referred noise and faster readouts.

In this research, a charge-gated TFT that operates as both a switched amplifier and driver is used to replace two transistors (the addressing switch and the amplifier transistor) of previously reported three transistor (3T) APS pixel circuits. In addition to enabling smaller pixels, the proposed 2T pixel amplifier results in better signal-to-noise (SNR) by removing the large flicker noise source associated with the switched TFT and increased pixel transconductance gain since the large ON-state resistance of the switched TFT is removed from the source of the amplifier TFT. Alternate configurations of 2T APS architectures based on source or drain switched TFTs are also investigated, compared, and contrasted to the gate switched architecture using charge-gated TFT.

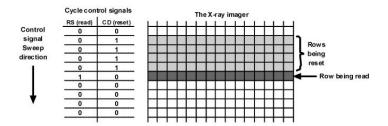

A new driving scheme based on multiple row resetting is introduced which combined with the on-pixel gain of the APS, offers considerable improvements in imaging frame rates beyond those feasible for PPS based pixels.

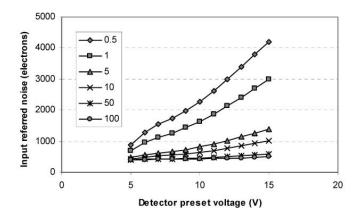

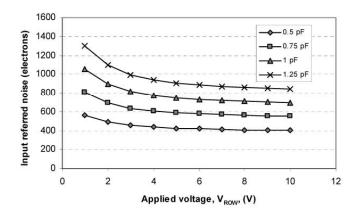

The novel developed 2T APS architectures is implemented in single pixel test structures and in 8×8 pixel test arrays with a pixel pitch of 100 µm. The devices were fabricated using an in-house developed top-gate TFT fabrication process. Measured characteristics of the test devices confirm the performance expectations of the 2T architecture design. Based on parameters extracted from fabricated TFTs, the input referred noise is calculated, and the

instability in pixel transconductance gain over prolonged operation tine is projected for different imaging frame rates.

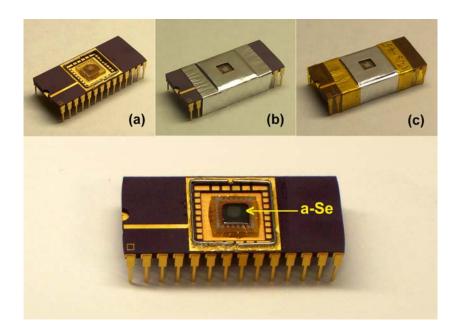

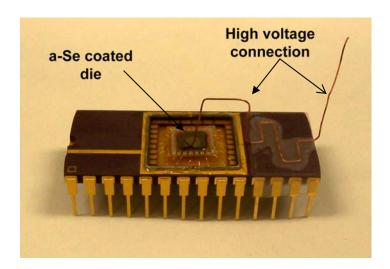

2T APS test arrays were packaged and integrated with an amorphous selenium (a-Se) direct x-ray detector, and the x-ray response of the a-Se detector integrated with the novel readout circuit was evaluated. The special features of the APS such as non-destructive readout and voltage programmable on-pixel gain control are verified.

The research presented in this thesis extends amorphous silicon pixel amplifier technology into the area of high density pixel arrays such as large area medical X-ray imagers for digital mammography tomosynthesis. It underscores novel device and circuit design as an effective method of overcoming the inherent shortcomings of the a-Si material. Although the developed device and circuit ideas were implemented and tested using a-Si TFTs, the scope of the device and circuit designs is not limited to amorphous silicon technology and has the potential to be applied to more mainstream technologies, for example, in CMOS active pixel sensor (APS) based digital cameras.

### **Organization of the Thesis (6 Chapters)**

Chapter 1 presents the general and introductory information on large area digital imaging and x-ray medical diagnostics imaging, followed by Chapter 2 as a short briefing on existing pixel architectures for large area imaging which serves as the intro for Chapter 3 as the core of the thesis on introducing novel pixel architectures for high resolution digital imaging. Chapter 4 explains details of the fabrication process developed for implementing the novel architectures using amorphous silicon technology, followed by Chapter 5 that completes the fabrication process by explaining the integration of the test imager arrays with x-ray amorphous selenium detector and presents results of x-ray response of the developed two-transistor amplified pixel architectures. Finally, the research work is summarized in Chapter 6 with conclusion and contributions of the author to the field of large area digital imaging. Bibliographies are at the end of each chapter.

# Acknowledgments

I am honored to express my deep appreciations to Professor Karim S. Karim for his technical instructions on my projects, his insightful supervision on my research work, and for his extraordinary support of my graduate program; I considerably learned a lot by working for, and with him. Also, I acknowledge my family for their everlasting love, plentiful encouragement and their unconditional support throughout my life, especially for the period of time I was perusing my study programs.

There are a number of individuals whose contributions to this work in terms of helps, insights, discussions and cooperation are gratefully recognized and truly appreciated: Mr. Bill Woods who went too far in letting me use the SFU fabrication facilities 24 – 7, Dr. Xinyu Wang for his assistance in use of CVD cluster tool, Dr. Eva, Professor Karen Kavanagh, and of course, my valued colleague, Michael Adachi for his collaboration in HW-CVD.

I specially thank Professor Safa Kasap and Dr. George Belev from University of Saskatchewan for their collaboration on a-Se photoconductor integration, Professor John Rowlands from University of Toronto for his remarks and guidance regarding the science of medical imaging.

I'd like to thank ALL my friends at the school of Engineering Science, SFU, without whom, the university life would had been half spirited (including): Shirin and Raj Pabla who mentored me when I was applying to SFU; my colleagues at STAR group and other SFU friends: Golnaz, Tony, Hadi, Ida, Amir, Michael, Lidya, Lila, Kourosh, and Esmaiel; specially Ida, for our collaborative work on photoconductors. I also thank Linda for our inspiring collaboration on remote heart beat monitoring system. Not forgetting Reza, of course, remembering our short breaks at the Organic Garden café during our long lab work hours, and for the discussion, every time, on who takes the last piece of the Cardamom cake.

My other friends and mentors to be appreciated are: Sam, Allen, Fay, Sharif, Hossein, Simin, Shahram and Sohrab: one can never forget the joy of numerous and lecture-full hiking, skiing and camping trips, and so many other outdoor activities we all did together in the beautiful province of British Columbia, and of course, the great lessons of life I learned from them.

# To my family,

whose love and supports are the treasure of my life,

and,

# to my teachers,

who nourished me with their knowledge, and patiently guided me along this path.

# Table of Contents

| Abstract                                                               | iii |

|------------------------------------------------------------------------|-----|

| Acknowledgments                                                        | V   |

| 1. Introduction to Digital X-Ray Imaging for Medical Diagnostics       | 1   |

| 1.1 Introduction                                                       | 2   |

| 1.1.1 Solid state electronic imagers                                   | 2   |

| 1.2 Large area imaging                                                 | 3   |

| 1.3 Flat panel imagers                                                 | 4   |

| 1.3.1 Silicon thin film technology                                     | 5   |

| 1.3.2 Amorphous silicon technology                                     | 6   |

| 1.3.3 Polycrystalline silicon technology                               | 7   |

| 1.4 X-ray digital imaging and its applications in medical diagnostics  | 8   |

| 1.4.1 Interaction of x-rays with matter                                | 8   |

| 1.4.2 Direct and indirect x-ray detectors                              | 11  |

| 1.5 X-ray imaging for mammography                                      | 15  |

| 1.5.1 Introduction to breast cancer                                    | 15  |

| 1.5.2 Mammography                                                      | 15  |

| 1.5.3 Tomosynthesis                                                    | 17  |

| 2. Existing Pixel Architectures for Large Area Digital Imaging         | 22  |

| 2.1 Passive Pixel Sensor Architecture                                  | 23  |

| 2.1.1 Introduction                                                     | 23  |

| 2.1.2 PPS operation                                                    | 24  |

| 2.1.3 Characteristic function of PPS architecture                      | 25  |

| 2.1.4 PPS architecture with voltage amplifier                          | 27  |

| 2.1.5 Numeric values and practical considerations for PPS architecture |     |

|   | 2.2      | Active Pixel Sensor Architectures                              | 28             |

|---|----------|----------------------------------------------------------------|----------------|

|   | 2.2.     | I Introduction                                                 | 28             |

|   | 2.2.2    | 2 APS operation and classification                             | 29             |

|   | 2.2.3    | 3 Voltage mediated APS                                         | 29             |

|   | 2.2.4    | 4 Current mediated APS                                         | 32             |

|   | 2.3      | Hybrid pixel designs                                           | 35             |

| 3 | . High   | Resolution Pixel Architectures                                 | 39             |

|   | 3.1      | Charge-Gated Thin Film Transistor                              | 40             |

|   | 3.1.1    | I Introduction                                                 | 40             |

|   | 3.1.2    | 2 Charge-gated TFT                                             | 40             |

|   | 3.1.3    | 8 Experimental results and discussion                          | 45             |

|   | 3.2      | Novel Two-Transistor Pixel Architectures                       | 47             |

|   | 3.2.     | I Introduction                                                 | 47             |

|   | 3.2.2    | 2 Two-Transistor APS Architectures                             | 48             |

|   | 3.<br>3. | 2.2.1 Pixel architecture using a gate-switched amplifier       | 53<br>54<br>56 |

|   | 3.2.4    | Noise Performance of 2T-APS                                    | 60             |

|   | 3.2.5    | 5 Metastability                                                | 65             |

|   | 3.2.6    | 5 Transient Response                                           | 69             |

|   | 3.3      | Summary                                                        | 75             |

| 4 | . Fabri  | cation of Test Arrays                                          | 81             |

|   | 4.1      | Thin Film Circuit Fabrication Process.                         | 82             |

|   | 4.1.1    | Thin Film Deposition                                           | 82             |

|   | 4.1.2    | 2 Thin Film Transistor Structure                               | 83             |

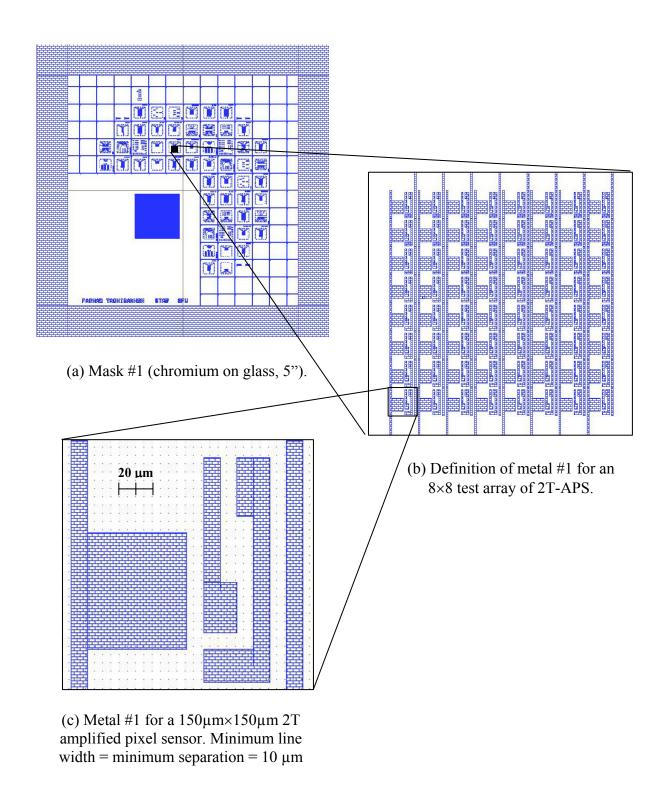

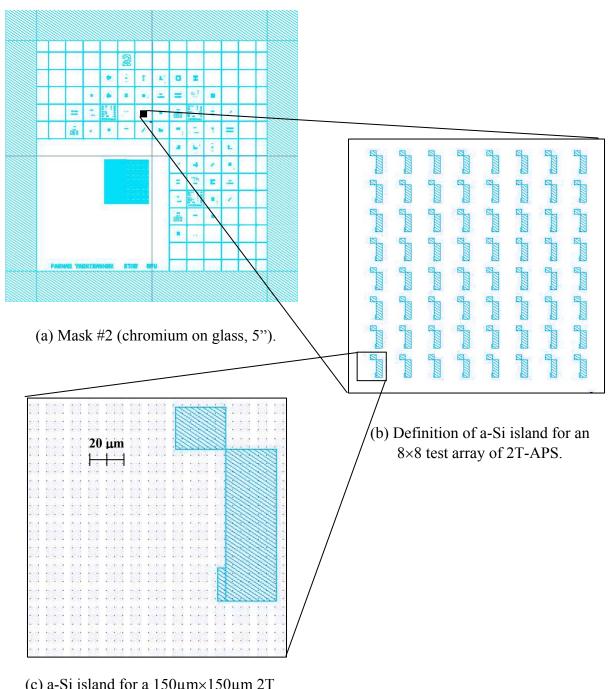

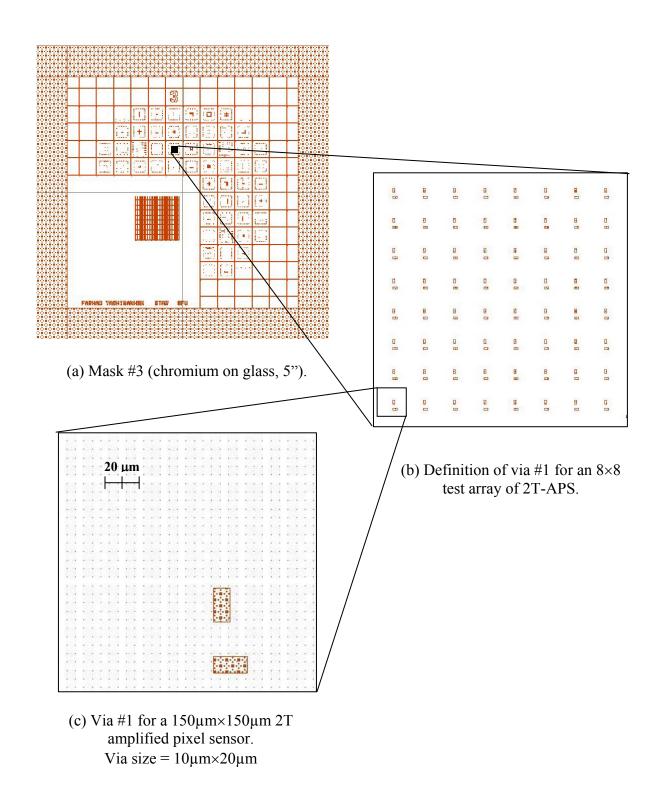

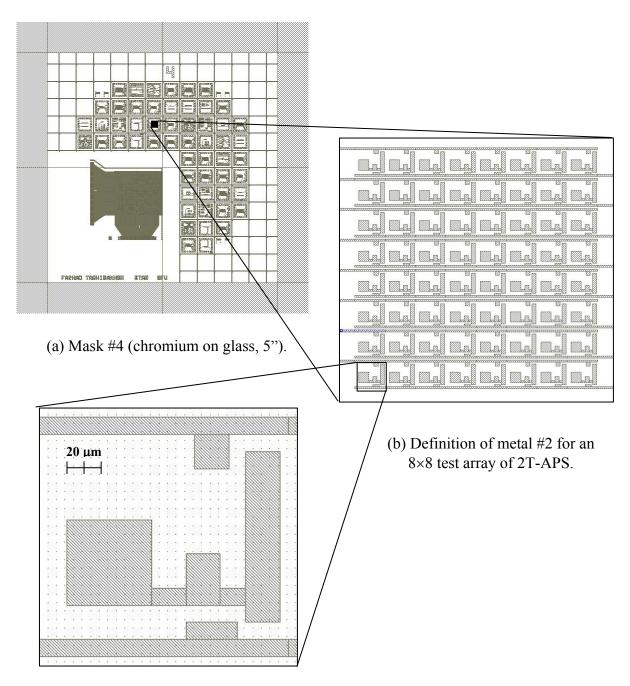

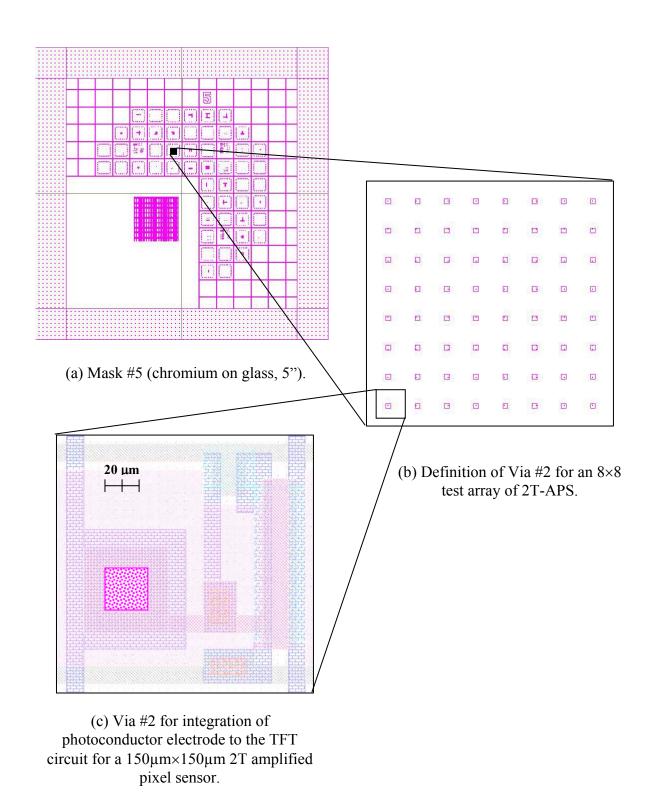

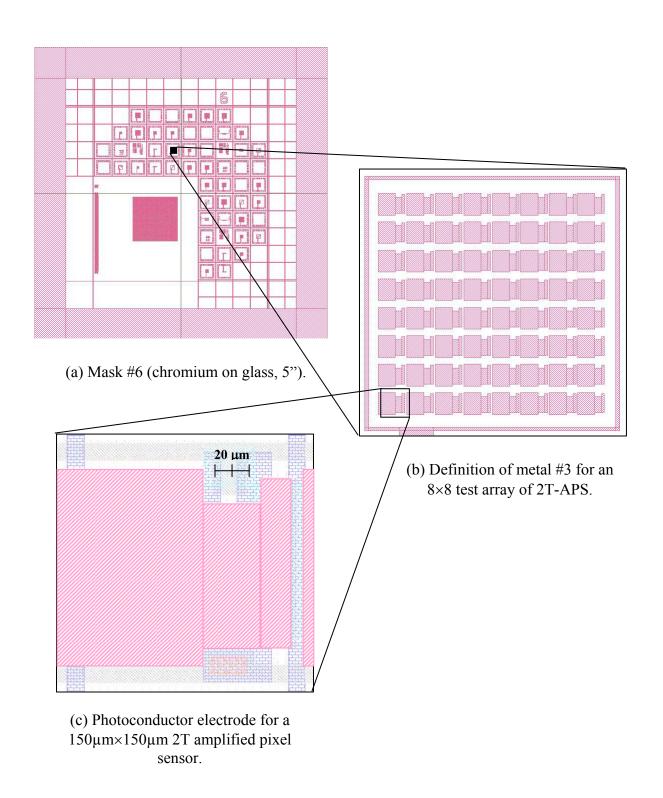

|   | 4.1.3    | 8 Mask Design                                                  | 85             |

|   | 4.1.4    | Fabrication Process                                            | 93             |

|   | 4.2      | Characteristics of Fabricated Thin Film Transistors and Arrays | 96             |

| 4.2            | 2.1 Thin Film Transistor Characterization       | 96  |

|----------------|-------------------------------------------------|-----|

| 4.2            | 2.2 Two-Transistor APS Array                    | 99  |

| <b>5.</b> X-ra | ay Response of the Two-Transistor APS           | 103 |

| 5.1            | Amorphous selenium x-ray photoconductor coating | 104 |

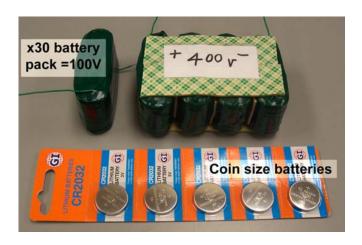

| 5.2            | High Voltage DC Source                          |     |

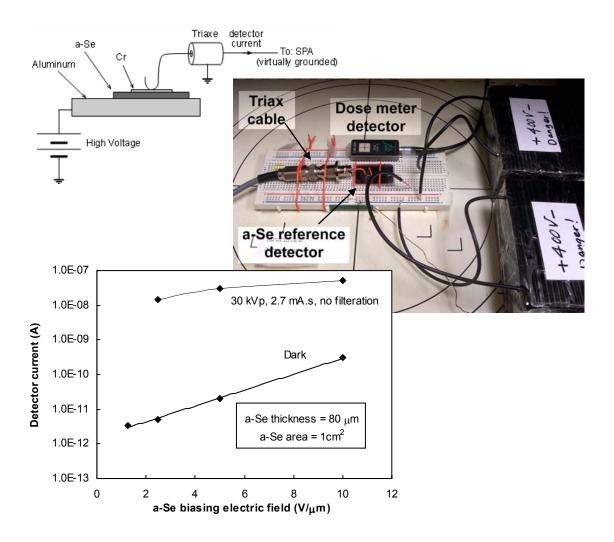

| 5.3            | Dark current measurement                        | 106 |

| 5.4            | X-Ray Measurement                               |     |

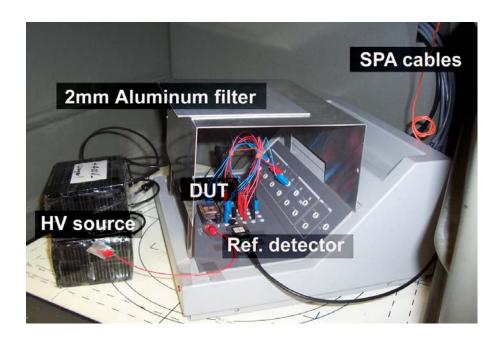

| 5.4            | X-ray cabinet and measurement setup             |     |

| 5.4            | 1.2 X-ray spectrum                              | 110 |

| 5.4            | 1.3 Detective Quantum Efficiency                | 111 |

| 5.4            | 1.4 X-ray response                              | 112 |

| 5.4            | 4.5 X-ray Sensitivity                           | 116 |

| 5.5            | Summary                                         | 117 |

| <b>6.</b> Con  | clusion and Contributions                       | 119 |

| Appen          | dix A                                           |     |

|                | List of Scholarly Contributions                 | 121 |

| Appen          | dix B                                           |     |

|                | Selected Papers                                 |     |

# 1

# Introduction to Digital X-Ray Imaging for Medical Diagnostics

This chapter briefly reviews the history of digital imaging, and introduces principals of x-ray imaging and its applications in medical diagnostics. Because the main focus of this research is to provide an x-ray detector solution for the emerging medical diagnostic modality of mammography tomosynthesis, which requires a high resolution low noise and high speed x-ray imager, this chapter is to provide essential introductory information that helps understanding the importance of the information brought up in the rest of the thesis.

### 1.1 Introduction

### 1.1.1 Solid state electronic imagers

The invention of transistor in 1947 phenomenally accelerated advances in solid state electronics leading to replacement of amplifying and switching vacuum tubes by their more reliable and less expensive solid state counterparts. The electronic imaging tube, known as vidicon, was not exempted and was later replaced by emerging solid state electronic imaging devices, CCDs. Willard Boyle and George E. Smith invented Charge Coupled Devices (CCDs) for memory applications at AT&T Bell Labs when developing semiconductor bubble memory devices in 1969. Although CCD was basically an electric charge shift register, it was immediately understood that the device can receive photo generated charge in the semiconductor substrate to capture images. In 1971 Bell researchers were able to demonstrate simple linear imagers, and therefore CCD for electronic imaging was born. Two dimensional arrays of CCDs have been shown to be of the highest quality imagers, and yet, the most expensive ones. The biggest disadvantage of CCDs is that their fabrication is not compatible with CMOS technology, with which the CCD drivers, image capturing and processing circuits are fabricated. It was apparent that an image detector technology developed using CMOS will dominate the market thanks to more available and less expensive fabrication lines, and less complicated assembly because the imager and driving/processing circuits are fabricated on the same substrate; a system on a chip.

The idea of Active Pixel Sensor (APS) arrays was developed separately by Nobel [1] and Chamberlain [2] in late 60s, when they were able to demonstrate image capturing using sensor arrays and active MOS readout amplifiers per pixel. In 1992 it was predicted that APS will commercially appear as the successor of CCDs [3] and between 1993 and 1995 Jet Propulsion Laboratory (JPL) developed a number of prototype CMOS imagers and demonstrated the key features of the technology. APS provides faster imaging with less image lag and considerably lower power consumption compared to CCDs, although it suffers from high fixed pattern noise. In 1995 Photobit corporation span off the JPL and

successfully commercialized APS technology for different applications such as web cams, digital cameras, digital radiography and many more.

### 1.2 Large area imaging

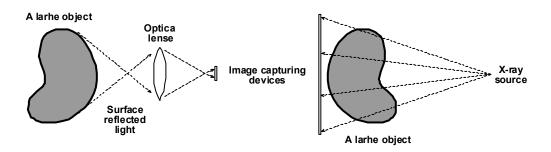

Optical imaging, no matter digital or analog, is usually tied up with optical lenses to project a reflectance image of large objects on to small capturing devices such as CCDs or emulsion films. The imaging principals and techniques fundamentally change when it comes to high penetrating x-rays, which are absolutely difficult, if not impossible, to focus them on a small image recording device. In case of x-rays therefore, a straight line configuration of source-object-imager is formed to cast a shadow of the object, or a transmission image, on to the imager which is as large as the object itself (Fig. 1.1).

Figure 1.1. In optical imaging (left) using lens and a small image capturing device, versus x-ray imaging (right) using a large area imager.

As in office scanners or x-ray security baggage checking systems, scanning large objects using a linear imager is a low cost solution at the expense of lower imaging speed and/or more complex mechanical systems for large area imaging. However, such methods are not used for medical x-ray imaging, except for computed tomography, because of the potentially high dose the patient can receive as the result of excessive exposure to radiation.

Thanks to the modular nature of CMOS imagers it is possible to tile a number of imaging modules together to assemble a large area imager [4]. However, the high price of large area processed silicon and challenges of tiling and assembling has proved the mosaic large area imagers technology to be expensive.

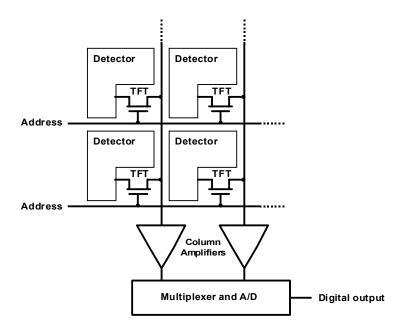

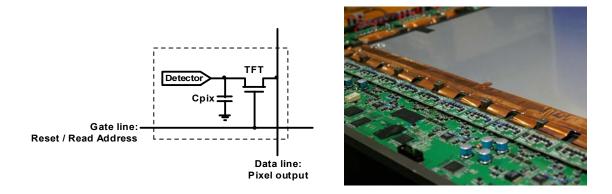

### 1.3 Flat panel imagers

Large area electronics was developed mainly in attempt to replace bulky CRTs with flat panel displays, which require a matrix of switching elements deposited on glass or plastic; an active matrix. Such switching devices, known as Thin Film Transistors, TFTs, are connected to passive display elements such as liquid crystal cells [5], or active devices such as Light Emitting Diodes LEDs [6]. Once the active matrix is developed, a large area flat panel imager is obtained if the active matrix is connected to light sensing elements such as *pin* diodes (Fig. 1.2). To have x-ray imaging capability, the imager is coated with a phosphor or scintillator materials such as gadolinium oxisulfide or cesium iodide that convert energetic x-rays photons to optical photons. As a result, a large area x-ray imager suitable for applications such as radiology or non destructive inspections is developed.

Figure 1.2 .Schematic diagram of a flat panel imager based on PPS architecture

X-ray imaging method explained above is called indirect method, because the x-ray photon is first converted to visible photons, and then these visible photons are converted to electric signal by the photo-sensing element such as the *pin* diode. Diffusion of light in the phosphor or scintillator layer renders blurred images, especially if thicker layers are needed to stop high energy x-rays. Direct detection scheme has been proposed and developed to solve this problem by using a photocoducting material such as amorphous selenium (a-Se) that generates electric charge upon absorbing x-rays. The generated charge is directed toward collecting electrode under very high biasing electric field which prevent diffusion of charge and blurring. Both direct and indirect flat panel x-ray imagers fabricated using hydrogenated amorphous silicon (a-Si:H) active matrix on glass substrates are commercially available today. They are based on passive pixel sensor (PPS) architecture (Fig. 1.2) a predecessor of the APS. Although x-ray imaging using APS has been extensively researched [7-11], commercial products have not yet been reported.

### 1.3.1 Silicon thin film technology

It is well accepted that thin film field effect devices were first introduced solid state transistors [12], and first tried. Although the problem of high interface states redirected thin film device research to the invention of point contact transistor, however the work on TFTs continued using compound semiconductors such as cadmium sulfide and cadmium selenide, under the motivation from display industry, and resulted in development of many Active Matrix LCD (AMLCD) prototypes [13]. Although CdSe based TFTs show very high electron mobility, the display industry and device physicists preferred amorphous silicon TFTs (mobility ≤1 cm²/V.s) upon introduction [14] basically because of its amorphous and amphoteric nature, compared to polycrystalline and reactive nature of CdSe to environmental conditions. Silicon thin film technology is now the work horse of the today's \$80B flat panel display market, which is projected to be a \$100B business by 2009.

### 1.3.2 Amorphous silicon technology

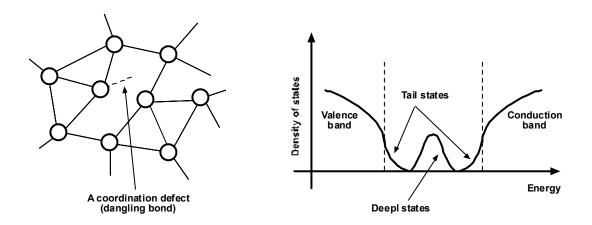

Amorphous silicon (a-Si) is an allotropic form of silicon known to have a random network of atoms with only short range order (Fig. 1.3). In a-Si, not all atoms in a-Si have four-fold coordination, which results in dangling bonds for some atoms. Presence of dangling bonds introduces trap level energies between the valance and the conduction band of a-Si; diminishing a clear cut between the two to have a bandgap. Passivation of dangling bonds using hydrogen, considerably reduces density of states, resulting in a bandgap-like structure that makes it possible to dope the material using phosphor and boron to produce n-type and p-type s-Si:H for device applications; the deep level, and band tail states are the main characteristics of the electronic structure of a-Si:H with an optical bandgap of ~1.8 eV.

Plasma Enhanced Chemical Vapor Deposition (PECVD) is the most common method for depositing a-Si:H thin films using Silane (SiH<sub>4</sub>) and hydrogen as precursor gases. The structural and electronic quality of the deposited film is controlled by a number of PECVD chamber parameters such as chamber pressure, gases flow rate, plasma power and frequency, the distance between plasma electrode and substrate temperature [15].

Figure 1.3. Diagram of amorphous silicon network (left), and resulting band energy (right)

Hydrogenated amorphous silicon is a metastable form of polycrystalline silicon. Re arrangement of bonding configuration Si-Si weak bonds and Si-Hi bonds are accelerated under external excitement. The bonding energy of hydrogen to silicon dangling bonds is low, especially in Si-H<sub>2</sub> form. Such weak bonds easily break under moderate applied electric field, or absorption of light which causes defect creation, leading to the known metastability problem in a-Si:H devices. For passivation of dangling bonds, only hydrogen atoms incorporated in form of Si-H bonds (and not Si-H<sub>2</sub>) are considered suitable for device quality films [16].

Table 1.1. Properties of device quality a-Si:H [17]

| Material constant                           | Typical value                          |

|---------------------------------------------|----------------------------------------|

| Dark conductivity                           | 10 <sup>-11</sup> S/cm                 |

| Conductivity activation energy              | 0.82 eV                                |

| Photoconductivity (100 mW/cm <sup>2</sup> ) | 10 <sup>-4</sup> S/cm                  |

| Optical bandgap                             | 1.7-1.8 eV                             |

| Electron mobility                           | $0.5-1.0 \text{ cm}^2/\text{V.s}$      |

| Hole mobility                               | $\sim 10^{-3} \text{ cm}^2/\text{V.s}$ |

| Refractive index                            | 4.3                                    |

| Hydrogen content                            | 18 at.%                                |

| Densiy                                      | $2.2 \text{ g/cm}^3$                   |

| Valence-band tail slope                     | 42–50 meV                              |

| Conduction-band tail slope                  | 25 meV                                 |

### 1.3.3 Polycrystalline silicon technology

While amorphous silicon TFTs offer a low cost solution for large area electronics such as display applications, a-Si:H technology seriously suffer from two major drawbacks: 1) very low electron mobility of about 1 cm<sup>2</sup>/V.s that limit a-Si:H TFTs applications to low speed electronics, and 2) much lower hole mobility that makes it very challenging

development of a-Si:H complementary devices like CMOS circuits for low power low cost processing applications. Polycrystalline silicon (p-Si) technology was developed to overcome such shortcomings of amorphous silicon technology [18]. The technology provides an electron mobility as high as a couple of hundreds cm²/V.s, and complementary NMOS and PMOS devices which enables manufacturers to integrate driving circuits of an active matrix on the same substrate to considerably reduce the product assembly cost and complication [19]. However, fabrication of polycrystalline silicon devices requires higher thermal budget and expensive facilities such as lasers or ion implantation for lengthy processes like re-crystallization or doping, which adds up to the manufacturing cost, and lowers the throughput [18].

Non-uniform characteristic of micron-sized devices heavily challenges process scientists and engineers when dimensions of the polycrystalline silicon device become comparable to the grain size. Such non-uniformities root back in uncertainties in the grain size, and the number of grain boundaries that may appear within the channel of a p-Si TFT [14]. While polysilicon TFTs are considered to be the next generation of devices for thin film electronics, intermediate phases of silicon like nanocrystalline silicon (nc-Si) also show promising future [20].

# 1.4 X-ray digital imaging and its applications in medical diagnostics

### 1.4.1 Interaction of x-rays with matter

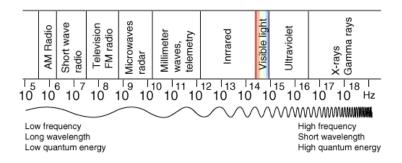

Electromagnetic waves of wavelength around 10 nm or shorter are called X-rays. They are subdivided into soft and hard x-rays, where the latter overlaps a range of long-wavelength gamma rays (Fig. 1.4). While there is no difference in their wavelengths or radiation properties, the distinction between the two types, i.e., hard x and gamma rays, comes from the source of radiation. In case of x-rays, deceleration of electrons, or

transition of electrons in atomic orbital is responsible for radiation, however, inter nuclei energy state transitions generate gamma rays.

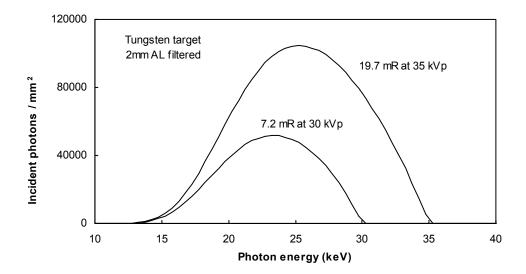

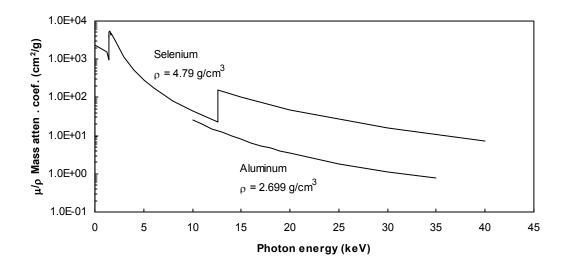

Figure 1.4. Span of electromagnetic wave, and associated labels

The basic generation of x-rays is by accelerating electrons in order to collide with a heavy metal target (copper, molybdenum or tungsten usually). Here the electrons suddenly decelerate upon colliding with the metal target and continuous spectrum of x-ray energies are emitted which is called bremsstrahlung. If enough energy is contained within the electron it is able to knock out an electron from the inner shell of the metal atom and as a result electrons from higher energy levels then fill up the vacancy and characteristics x-ray photons are emitted which their energy is depended to the metal target. Nowadays, for many applications, x-ray production is achieved by synchrotrons. However because of high complexity and cost synchrotron x-ray imaging has limited applications.

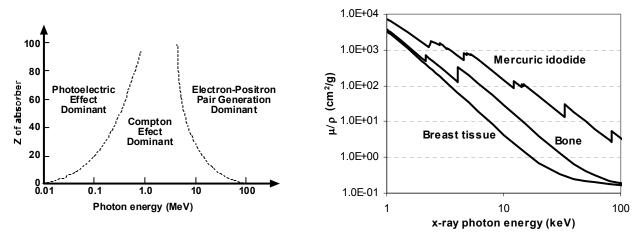

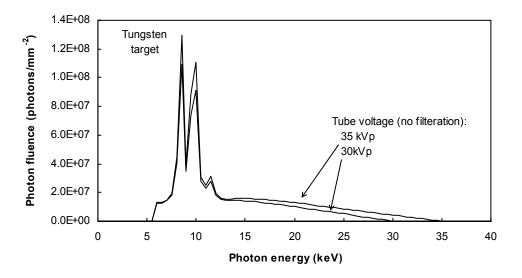

X-rays are high penetrating radiation, e.g., 37% of a 60 keV radiation will pass through 3 centimeter of a material like bone. The intensity of the radiation at any given depth of the absorbing material is given by equitation 1.1.1 which shows the absorption exponentially increases as the radiation penetrates through the material with an absorption coefficient which is energy and material depended (Fig. 1.5).

$$I(x) = I_0 \exp\left[\left(-\frac{\mu}{\rho}\right)\rho x\right]$$

(1.1)

Depending on the incident photon energy and the material, X-rays interact with mater in three different mechanisms; photoelectric, Compton and pair generation (Fig. 1.5). In the first method, the X-ray gives its energy to an orbital electron and kicks it out. Where in the second, virtually same thing happens but not all the incoming photon energy is consumed; therefore the X-ray loses part of its energy and changes its wavelength. In pair generation, the X-ray energy is higher than two times the rest mass of electron, so, its quantum energy is converted to an electron-positron pair.

Figure 1.5. Different mechanisms of x-ray absorption in material (left), graph of mass attenuation coefficient for different materials versus x-ray photon energy (data compiled from: physics.nist.gov)

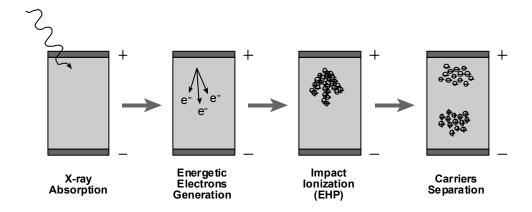

Although the absorption of an X-ray quantum is a single and momentary event, conversion of an X-ray to electric charge is a sequential process. For energies lower than 150 keV which is basically used for medical imaging, photoelectric effect is the dominant mechanism of X-ray absorption in materials. Upon absorption, the energy of the X-ray quantum is transferred to an electron which will produce numbers of electron-hole pairs or other energetic electrons through impact ionization. Secondary X-ray radiation my also happen if the incoming radiation quantum is stopped by an inner shell orbital electron. Secondary radiations will be absorbed the same way as the original incident X-ray and generate numbers of electron-hole pairs depending on the energy of the incoming radiation quantum and type of the absorbing material. The amount of energy required to

produce one electron hole pair in different materials is named as W. If an x-ray photon is absorbed, the number of generated electron hope pairs, N, would therefore be E/W, with E representing the energy of the absorbed X-ray photon.

Because the generated x-ray from an x-ray tube, for example, contains photons of different energy with different fluence,  $\phi(E)$ , the total absorbed x-ray energy,  $E_{ab}$ , in a detector with area of A is calculated as [21]:

$$E_{ab} = \sum_{E} \phi(E) A \eta(E) \frac{\mu_{ab}(E)}{\mu(E)} E \tag{1.2}$$

in which, E is the x-ray energy,  $\mu(E)$  and  $\mu_{ab}(E)$  are the x-ray attenuation, and absorption coefficients, and  $\eta(E)$  is the x-ray quantum efficiency (QE) determined from:

$$\eta(E) = 1 - \exp[-\mu(E)d]$$

(1.3)

where, d is the depth of the detector material. The x-ray spectra used in calculations of the fluence are obtained from a computer model. From this, the generated charge in the detector material  $Q_{gen}$  is determined by the ratio of absorbed energy per pixel  $E_{ab}$  and the energy W needed to create an electron-hole pair in the target material:

$$Q_{gen} = \frac{E_{ab}}{W}. (1.4)$$

#### 1.4.2 Direct and indirect x-ray detectors

Different detector materials are used for X-ray detection. If generated electron hole pairs have enough high mobility and long recombination life time they could be collected by applying a DC electric field to the detector. Such detectors are called photoconductor or semiconductor photodetectors, and the mechanism of X-ray detection using photoconductors is called direct detection (Fig. 1.6) because the X-ray energy is directly converted to electric charge. Direct detection of X-rays in photoconductors depends on

how many electron-hole pairs (EHPs) are generated upon absorption of X-rays and how effectively they are collected (charge collection efficiency). Therefore, any detector with lower value of (W) (equivalent to higher number of EHPs generated by an X-ray quantum) and higher carrier mobility-time product ( $\mu\tau$ ) would be considered better, if the dark current is sufficiently low and the detector has a low image lag. Image lag is related to the memory effect of photoconductors which is primarily caused by slow de-trapping of trapped charges upon absorption of X-ray. Properties of a few of common photoconductors are listed in Table 1.1 among which amorphous selenium is the most common.

An ideal photoconductor for X-ray detection should have very small absorption thickness (less material and less applied voltage), high bandgap energy to have less dark current, and low value of W to generate more electron hole pairs, and high (and matched) value of mobility-life time constant for both electrons and holes to maintain efficient charge collection and fast imaging.

Figure 1.6. Different steps of direct x-ray detection using a biased photoconductor detector

Table 1.2. Common semiconductor x-ray detectors and their specifications [22]

| Photoconductor | Absorption<br>depth for 60<br>keV(µm) | Eg (eV) | W±<br>(eV) | $\frac{\mu_e \tau_e}{(cm^2/V.s)}$  | $\frac{\mu_h\tau_h}{(cm^2/V.s)}$  |

|----------------|---------------------------------------|---------|------------|------------------------------------|-----------------------------------|

| a-Se           | 976                                   | 2.3     | 45         | $0.3 - \frac{3}{6} \times 10^{-6}$ | $0.6 - \frac{6}{5} \times 10^{-}$ |

| HgI2           | 252                                   | 2.1     | 5          | 1.5×10 <sup>-5</sup>               | $10^{-7}$                         |

| CdZnTe         | 280                                   | 1.7     | 5          | $5 \times 10^{-4}$                 | $10^{-4}$                         |

| Desired to be  | Low                                   | high    | Low        | High                               | High                              |

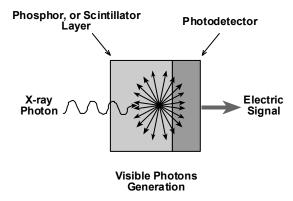

Phosphorescent (and/or fluorescent) materials are widely used as X-ray detectors in which, generated electron hole pairs can quickly recombined in a direct band to band (or band-trap or trap-trap) transition and emit UV or visible photon of a specific wavelength; they are called phosphors and/or scintillators. In order to detect X-rays using scintillators, the visible photons emitted by the scintillator are next detected by a photodetector such as a pin diode, optically coupled to the scintillator (Fig. 1.7). Such detection mechanism is called indirect detection because of the two step conversion involved. Decay time and after glow are among most important and limiting factors of scintillators; short decay time and no afterglow are requited for high speed detection for real time applications. The disadvantage of scintillators is the fact that visible photons once generated scatter everywhere in the detector and therefore the spatial resolution would be poor compared to direct detection where high biasing electric field in the photoconductor reduces lateral diffusion of generated charge carriers. Special types of columnar scintillators, or composite materials should be used in order to improve the image resolution captured through indirect X-ray detection. Common scintillator materials are listed in Table 1.3.

Figure 1.7. Indirect x-ray detection mechanism involves generation of visible photons in a phosphor (or scintillator) layer, and detection of those photons by a photodetector

Table 1.3. Common scintillator x-ray detectors (phosphors / scintillators) and their specifications (wikipedia.org)

| Phosphor / Scintillator                  | Color (wavelength)   | Decay to 10% | Afterglow |

|------------------------------------------|----------------------|--------------|-----------|

| Gd <sub>2</sub> O <sub>2</sub> S:Tb      | Green (545 nm)       | 1.5 ms       | Low       |

| Gd <sub>2</sub> O <sub>2</sub> S:Pr,Ce,F | Green (513 nm)       | 4 μs         | No        |

| $Y_2O_2S$ :Tb                            | Light green (513 nm) | 7 μs         | No        |

| $CaWO_4$                                 | Blue (410 nm)        | 20 μs        | No        |

| CsI:Tl                                   | Green (454 nm)       | 5 μs         | High      |

| CdS:In*                                  | Green (525 nm)       | <1 ns        | No        |

<sup>\*</sup> Basically used for detection of energetic electrons.

### 1.5 X-ray imaging for mammography<sup>1</sup>

#### 1.5.1 Introduction to breast cancer

Breast cancer is caused when the body loses its control over proliferation of glandular cells in the breast. A death rate of 24.3% is reported among 179,000 women diagnosed with breast cancer in US in 1998. Breast cancer is considered one of the major killers of women. While some specific mutated genes are recognized to be responsible for at least 4% of breast cancer occurrence, the exact cause of breast cancer is still unknown to a large extent. Lack of sufficient information abut the cause of breast cancer has considerably increased the importance of mammography to detect breast cancer in its very early stages (in situ, or minimally invasive) as the only effective way to control it; i.e., before it reaches the point (metastasis) when treatment is ineffective.

### 1.5.2 Mammography

Mammography, or the X radiology of the breast is used for different purposes including a) investigating symptomatic patients (those who have been diagnosed with breast cancer), or screening of women in different ages, or to locate suspicious areas prior to a surgery or biopsy. Detection of breast cancer depends on identification of following traces in a mammogram:

- Appearance of a tumor mass

- Detection of certain amount of mineral deposits which is called microcalcification

- Distortion in normal tissue pattern

- Asymmetry between corresponding regions of left and right breast

<sup>1</sup> Information of this section is adapted or compiled from "Digital Mammography" by M. J. Yaffe, in "Handbook of Medical Imaging", Volume 1. Physics and Psychophysics, ch. 5, pp. 331-367, Edited by J. Beutel, SPIE publications, 1999

A mammography imaging system must be capable of visualizing above listed main features of the disease, encoded in minor changes in tissue x-ray attenuation associated with breast cancer. The imaging system should be able to perform following tasks with the least amount of patient delivered dose:

- Accurately measure intensity of transmitted x-ray through all regions of the breast.

- Amplify small contrast differences resulting from subtle differences in x-ray attenuation coefficient of the breast tissue.

- Provides high spatial resolution to visualize fine details of microcalcification

Because of these stringent requirements digital mammography is one of the most demanding but challenging medical x-ray modalities. General specifications of a mammography imager are listed in Table 1.4 [7].

Table 1.4. General requirements and specifications of a mammographic imager

| Imager size (cm)                | Small & medium: 18×24   |

|---------------------------------|-------------------------|

|                                 | Large: 24×30            |

|                                 | Best: 50                |

| Dell pitch (μm)                 | Typical: 75             |

|                                 | Max: 100                |

| X-rar spectrum (kVp)            | 30                      |

| Exposure range (mR)             | 0.6 - 240               |

| Image charge per pixel for a-Se |                         |

| direct photoconductor detector  | $1.68 \times 10^5$      |

| (e <sup>-</sup> /dell/mR)       |                         |

| Dynamic range (e <sup>-</sup> ) | $10^5 - 40 \times 10^6$ |

In addition to the previous list of tough requirements of digital mammography, an imager with high dynamic range is needed with pixel architecture capable of holding up to 40 million electrons, as well as providing linear response.

### 1.5.3 Tomosynthesis

Blurring tomography technique involves in moving both x-ray source and the detector during exposure, in such a manner that anatomical structures out of a plane of interest are blurred; rendering a relatively sharp image of that particular plane. This technique has been adapted to digital imaging and is refined to tomosynthesis in which, a series of 2D images are taken from different viewing angles. These images are then digitally processed to render tomographic images. Digital imaging has made it possible to extract tomographic images of different planes from the same set of images. In addition to that, tomosynthesis can be performed without breast compression, and therefore it can provide better Z information of suspicious tissues, and reduced structure noise compared to normal mammography.

Patient dose is a critical aspect of tomosynthesis. While certain amount of dose is required to obtain sufficiently high contrast mammograms, tomosynthesis should not delivered more than that dose, independent of the number of frames captured. If the dose is taken to be the same for mammography and tomosynthesis, it means less dose is available for each frame as the number of images is increased. Low noise imaging is therefore required to render sufficiently high contrast images with the reduced dose per frame in tomosynthesis. Fast imaging is the other requirement of tomosynthesis. While the total exposure time is limited, and should be kept as short as practical to eliminate image blurring due to patient's movements, taking a large number of frames in a limited short time requires high frame rate. Table 1.5 compares and contrasts general specifications and detector requirements of regular mammography and mammography tomosynthesis.

Table 1.5. Requirements of a tomosynthesis imager with pixel pitch of 100  $\mu m$

|                                                                                  | Tomosynthesis                     | Mammography                       |

|----------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|

| Imager size (cm)                                                                 | 18×24                             | 18×24                             |

| Pixel pitch (µm)                                                                 | 100                               | 100                               |

| X-ray spectrum (kVp)                                                             | 30                                | 30                                |

| Number of frames                                                                 | 100                               | 1                                 |

| Frames per second                                                                | High: $50 - 100$                  | -                                 |

| Exposure range (mR)                                                              | 0.006 - 0.24 /frame               | 0.6 - 240                         |

| Image charge per pixel<br>for a-Se direct detector<br>(e <sup>-</sup> /pixel/mR) | 6.72×10 <sup>5</sup>              | 6.72×10 <sup>5</sup>              |

| Dynamic range (e <sup>-</sup> )                                                  | $4 \times 10^3 - 1.6 \times 10^6$ | $4 \times 10^5 - 1.6 \times 10^7$ |

| Quantum noise level (e <sup>-</sup> )                                            | ~1264                             | ~12,640                           |

It is expected that a digital imagers has the following features for mammography, in general, and mommography tomosynthesis, in particular:

- High resolution

- High dynamic range

- High gain and low noise

- High frame rate for fast imaging

### **Bibliography**

- [1]: P. J.W. Noble "Self-Scanned Silicon Image Detector Arrays", *IEEE Journal of Electron Devices*, vol. 15, no. 4, pp. 202–209, April 1968.

- [2]: S. G. Chamberlain, "Photosensitivity and Scanning of Silicon Image Detector Arrays", *IEEE Journal of Solid-State Circuits*, vol. 4, no. 6, pp. 333–342, December 1969.

- [3]: E. Fossum, "Charge-Coupled Devices and Solid State Optical Sensors", Proc. SPIE vol. 1900, p. 2-14,

- [4]: K. Spariotis et. al, "Novel direct digital modular x-ray device and system", Proc. SPIE vol. 3336, pp. 529-536, Medical Imaging 1998.

- [5]: B. J. Lechner, F. J. Marlowe, E. O. Nester, and J. Tults, "Liquid Crystal Matrix Displays," Proceedings of IEEE vol. 59, pp. 1566, (1971).

- [6]: A. Nathan et al, "a-Si AMOLED display backplanes on flexible substrates", MRS Spring Meeting, Flexible Electronics-Materials and Device Technology, vol. 814, p.I3.1, (2004).

- [7]: K.S. Karim, A. Nathan, J.A. Rowlands, "Alternate Pixel Architectures for Large Area Medical Imaging," in Medical Imaging 2001: Physics of Medical Imaging, L. Antonuk, M. Yaffe, Editors, SPIE vol. 4320, pp. 35-46, February 2001.

- [8]: Karim, K.S., Nathan, A., Rowlands, J.A., Kasap, S.O., 'X-ray detector with on-pixel amplification for large area diagnostic medical imaging,' IEE Proceedings on Circuits, Devices and Systems, 2003, **150**, (4), pp. 267-273.

- [9]: Karim, K.S., Sanaie, G., Ottaviani, T., Izadi, M.H., Taghibakhsh, F., 'Amplified pixel architectures in amorphous silicon technology for large area digital imaging applications,' Journal of Korean Physical Society, 2006, 48, (1), pp. 585-591.

- [10]: Karim, K.S., Nathan, A., Rowlands, J.A., 'Amorphous silicon pixel amplifier with VT compensation for low noise digital fluoroscopy', IEEE International Electron Devices Meeting (IEDM) Technical Digest, 2002, pp. 215-218.

- [11]: F. Taghibakhsh, K. S. Karim, 'High Dynamic Range 2-TFT Amplified Pixel Sensor Architecture for Digital Mammography Tomosynthesis', IET Circuits Devices and Systems, vol. 1, issue 1, pp. 87-92, February 2007

- [12]: J. E. Lilienfeld, "Device for Controlling Electric Current," US Pat. 1,900,018 (1933).

- [13]: M. Dobler, R. Bunz, E. Lueder, and T. Kallfass, "Fabrication of CdSe-TFTs with High Mobility of 300 cm<sup>2</sup>/V-s for a 140,000-pel AMLCD," op. cit.

- [14]: P. G. LeComber, W. E. Spear, and A. Ghaith, "Amorphous Silicon Field-Effect Device and Possible Application," Electronic Letters, vol. 15, pp. 179, (1979).

- [15]: P. G. LeComber, W. E. Spear, and A. Ghaith, "Amorphous Silicon Field-Effect Device and Possible Application," Electron. Lett. 15, 179 (1979).

- [16]: W. M. M. Kessels, A. H. M. Smets, D. C. Marra, E. S. Aydil, D. C. Schram, and M. C. M. van de Sanden, "On the growth mechanism of a-Si:H," Thin Solid Films, vol. 383, pp. 154–160, 2000.

- [17]: J. Jang, "Preparation and Properties of Hydrogenated Amorphous Silicon Thin-Film Transistors", chap. 2, sec. 2, in "Thin Film Transistors", 1<sup>st</sup> edition, Marcel Dekker, Inc., NY, 2003, edited by C.R. Kagan and P. Andry.

- [18]: A.T. Voutsas, M.K. Hatalis, "Thechnology of Polysilicon Thin-Film Transistors", chap. 4 in "Thin Film Transistors", 1<sup>st</sup> edition, Marcel Dekker, Inc., NY, 2003, edited by C.R. Kagan and P. Andry.

- [19]: M. Lee, J. Yoo; M. Han, "Low-temperature polysilicon TFT with counter-doped lateral bodyterminal", Electronics Letters, vol. 38, no. 5, pp. 255 256, (2002).

- [20]: M. Fonrodona, J, Escarre, F. Villar, D. Soler, J. Bertomeu, J. Andreu, A. Saboundji, N. Coulon, N. Mohammed-Brahim, 2005 Spanish Conference on Electron Devices, 183-186, (2005).

- [21]: W. Zhao and J. A. Rowlands, "X-ray imaging using amorphous selenium: Feasibility of a flat panel self-scanned detector for digital radiology," *Medical Physics*, 22(10), pp. 1595-1604, 1995.

- [22]: M. Yunus, "Monte Carlo Modeling of the Sensitivity of X-ray Photoconductors", Master of science thesis, Department of Electrical Engineering, Saskatoon, University of Saskatchewan, April 2005.

2

# Existing Pixel Architectures for Large Area Digital Imaging

This chapter describes various existing pixel architectures for large area digital imaging to provide the background information [1] for the next chapter where novel architectures for high resolution digital imaging are introduced. Transfer function of existing architectures are calculated, using which different pixel architectures are compared and contrasted based on their performances such as conversion gain, and readout speed, as well as pixel complexity, size and fabrication reliability.

### 2.1 Passive Pixel Sensor Architecture

### 2.1.1 Introduction

The passive pixel sensor (PPS) is possibly the simplest architecture for large area imaging [2, 3], and provides the most compact pixel design for high resolution imaging. The architecture of a PPS as shown in Fig. 2.1 consists of a detector connected to a transistor switch. It is called "passive" because in PPS architecture the transistor operates as passive switch rather than an active amplifying device. Large area two dimensional arrays of passive pixel sensors employing direct or indirect x-ray detectors have been developed and are commercially available, known as, flat panel imagers (FPIs) or flat panel detectors (FPDs) [4]. Today, the PPS is the industry standard architecture for large are x-ray imagers for both direct and indirect x-ray detectors.

Figure 2.1. Architecture of a passive pixel sensor (left), close-up picture of a corner of a Samsung (039-s) PPS based 45 cm × 45 cm indirect detection flat panel detector with 149µm pixel pitch (http://www.gizmag.com/samsung-digital-x-ray-detector/8396)

The detector can be either a photo diode, such as a-Si pin diode coupled to a scintillator layer for x-ray detection, or a photoconductor such as amorphous selenium (a-Se) for direct x-ray detection. In case a photodiode is used, the junction capacitance of the diode would be the large enough, so that there would be no need of a physical pixel capacitor.

In case of using a photoconductor such as a-Se, because of the large a-Se thickness required to stop x-ray, the detector capacitance would be small, so that a physical capacitance is needed to hold the detector charge.

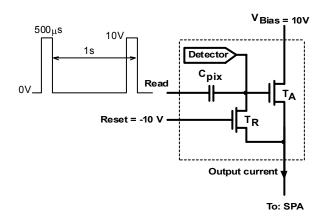

### 2.1.2 PPS operation

Capturing images using PPS architectures consists of two steps: 1) *Integration*, and 2) readout/reset [1, 2]. During *Integration* mode, the TFT switch is OFF, and the electric charge generated in the detector as the result of incident radiation, is deposited on  $C_{pix}$ . In the *Readout/Reset* mode the TFT switch is turned ON and the stored charge on the  $C_{pix}$  is transferred to the charge amplifier via data line, where it is converted to an equivalent voltage,  $V_{out}$ . Figure 2.1 shows the circuit diagram of a PPS connected to the column charge amplifier via data line. When the charge is read out at the end of the readout mode,  $C_{pix}$  charge is reset to zero and the pixel is ready for the next *Integration*.

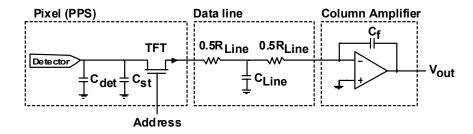

Figure 2.2. The circuit diagram representing a passive pixel sensor connected to the column charge amplifier via the data line

Figure 2.3. The circuit model of one PPS pixel connected to the column charge amplifier

#### 2.1.3 Characteristic function of PPS architecture

The circuit model of a passive pixel connected to a charge amplifier via a resistive/capacitive data line is shown in Fig. 2.3, where the switching TFT is simply modeled by its gate overlap capacitances and drain-source resistance. The pixel capacitance  $C_{pix}$ , is the sum of detector capacitance,  $C_{det}$ , the pixel storage capacitance,  $C_{st}$ , and the drain-gate capacitance,  $C_{dg}$  [1]

$$C_{pix} = C_{det} + C_{st} + C_{dg} \tag{2.1}$$

The data line is simply modeled by a line resistance and capacitance,  $R_{Line}$  and  $C_{Line}$  respectively. For each column, the parasitic line capacitance,  $C_{Line}$ , has three major components: 1) the source-gate capacitance of all TFTs connected to the column, 2) the cross-over capacitances of the said column data line with all the gate lines, and 3) pissible cross-over capacitance of the data line with detector bias line or other metal layers depending on the design. Assuming the voltage gain of the charge amplifier is  $A_v$ , the miller capacitance of the feedback capacitor  $C_f$ , i.e.,  $(1+A_v)C_f$  appears at the input of the charge amplifier. At the end of a very long readout time, the detector deposited signal charge,  $Q_{sig}$ , is distributed over all capacitors of the system, and a steady state  $V_{out}$  is generated.

$$V_{out} = A_{\nu}V_{x} = \frac{A_{\nu}Q_{sig}}{C_{Pix} + C_{Line} + (1 + A_{\nu})C_{f}}$$

(2.2)

Therefore, for finite readout time, when  $Q_{sig}$  is not fully distributed over all capacitances, the output voltage is approximated to:

$$V_{out} = \frac{\eta_{TR} Q_{sig}}{C_f}$$

(2.3)

where  $\eta_{TR}$  is the charge transfer efficiency of the readout cycle, i.e., the ratio of transferred to detector deposited charge due to finite readout time. In the rest of this

section we attempt to evaluate  $\eta_{TR}$  based on response time of the PPS architecture to calculate the output voltage of the PPS architecture with charge amplifier.

Figure 2.4. The circuit model for estimation of charge transfer time constant of PPS architecture

Zero time constant approximation is used to estimate the time constant associated with transfer of charge from pixel detector to the integrator capacitor. Given the fact that the input of the charge amplifier is virtually grounded (Fig. 2.2), there would be three time constants associated with each of  $C_{Line}$ ,  $C_{GS}$  and  $C_{Pix}$  independently as:  $\tau_1 = C_{Line} R_{Line}/2$ ,  $\tau_2 = C_{GS} R_{Line}$ ,  $\tau_3 = C_{Pix} (R_{ON} + R_{Line})$ . The charge transfer time constant  $\tau_{TR}$  is then calculated as:

$$\tau_{TR} \approx \sqrt{\tau_1^2 + \tau_2^2} = \sqrt{C_{Pix}^2 (R_{ON} + R_{Line})^2 + C_{Line}^2 R_{Line}^2 / 4}$$

(2.4)

Because of the large value of  $R_{ON}$  compared to  $R_{Line}$ ,  $\tau_2$  is the much larger than  $\tau_2$ , and it dominates the time constant.

$$\tau_{TR} \approx C_{Pix} \left( R_{ON} + R_{Line} \right) \tag{2.5}$$

The ON state resistance of a switch TFT, derived from its linear characteristic region, depends on its geometry as well as its gate-source voltage, and is defined by the following equation:

$$R_{ON} = [K(V_{read} - V_t)]^{-1}$$

(2.6)

Here, K is the gain factor of the TFT equal to the product of field effect mobility,  $\mu_{FE}$ , gate capacitance per unit area,  $C_0$ , and the aspect ratio, W/L of the switch TFT, with  $V_t$  representing its threshold voltage.  $V_{read}$  is the voltage applied to the gate line, and should

be high enough to  $R_{ON}$  as low as practical When the pixel is read out for  $t_{Read}$  seconds, the charge transfer efficiency is calculated as follow:

$$\eta_{TR} = \frac{A_{v} \left( 1 - \exp\left(-t_{\text{Re}\,ad} / \tau_{TR}\right) \right)}{1 + A_{v} + \left(C_{Pix} + C_{Line}\right) / C_{f}}$$

(2.7)

Equation 2.7 clearly shows the role of different components of the PPS architecture in charge transfer efficiency which determines the output voltage as stated in Eqn. 2.3 Also, it shows that high value of  $A_{\nu}$  and enough long readout time are necessary to have close to unity charge transfer efficiency. Substituting Eqn. 2.7 in 2.3 results in characteristic equation of PPS with charge gain as follow:

$$V_{out\ PPS} = \frac{Q_{sig}}{C_f} \frac{A_{\nu} (1 - \exp(-t_{\text{Re}\,ad}/\tau_{TR}))}{1 + A_{\nu} + (C_{Pix} + C_{Line})/C_f}$$

(2.9)

### 2.1.4 PPS architecture with voltage amplifier

In PPS architecture, non-inverting voltage amplifiers (with voltage gain of  $A_v$ , and high input impedance), or inverting voltage amplifiers [1] can also be used in place of charge amplifiers, which are considered to be expensive components. Assuming large enough input impedance column amplifier for no loss of charge,  $Q_{sig}$  will be distributed over  $C_{pix}$  and  $C_{Line}$ , and the output voltage is calculated to be:

$$V_{out\ V-PPS} = \frac{Q_{sig}}{C_{pix} + C_{Line}} A_v \left( 1 - \exp(-t_{Re\ ad}/\tau_{TR}) \right)$$

(2.10)

Although Eqn. 2.10 shows that the charge to voltage conversion gain could be considerably large with large enough  $A_v$ , but because  $C_{Line}$  is much larger than  $C_{pix}$ , the input voltage at the column voltage amplifier would be very small, making this readout approach vulnerable to noise, especially for low input signal values [1].

# 2.1.5 Numeric values and practical considerations for PPS architecture

To compare the two different readout schemes of PPS architecture discussed, the charge to voltage conversion gain, or, the ratio of  $V_{out}/Q_{sig}$  is calculated [1] based on nominal values of parameters as listed in table 2.1.

Table 2.1. Nominal values of parameters for PPS architecture

| Parameter        | Value                        | Parameter         | Value                  |

|------------------|------------------------------|-------------------|------------------------|

| $\mu_{FE}$       | $0.5 \text{ cm}^2/\text{Vs}$ | $C_{pix}$         | 0.5 pF                 |

| $C_{0}$          | $20.0 \text{ nF/cm}^2$       | $C_{Line}$        | 50.0 pF                |

| W                | 50 μm                        | $R_{Line}$        | $1.0~\mathrm{k}\Omega$ |

| L                | 10 μm                        | $	au_{TR}$        | 1.0 μs                 |

| $V_{read} - V_t$ | 10.0 V                       | $C_f$             | 0.5 pF                 |

| $R_{ON}$         | $2.0~\mathrm{M}\Omega$       | $A_{v}$           | 100                    |

| Vout PPS / Qsig  | 0.99 V/pC                    | Vout V-PPS / Qsig | 1.98 V/pC              |

## 2.2 Active Pixel Sensor Architectures

#### 2.2.1 Introduction

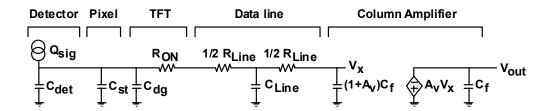

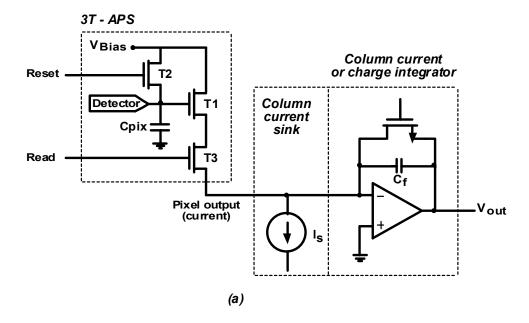

As introduced in chapter 1, the Active Pixel Sensor (APS) architecture appeared succeeding CCDs as an electronic imaging device fully compatible with the CMOS technology to provide low-power and low-cost solution for digital imaging. The classical APS architecture consists of a pixel detector and three transistors (Fig. 2.5), and is known as three-transistor (3T) APS. In contrast to PPS where the pixel output signal is the original detector integrated charge, in APS the sensor value is converted to an equivalent voltage or current using an on-pixel amplifier. This results in improved noise and/or readout speed performance [5-7].

Figure 2.5. Standard three-transistor APS architecture

# 2.2.2 APS operation and classification

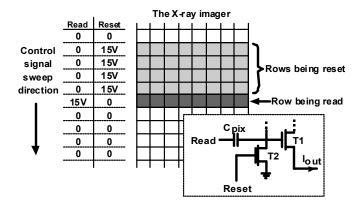

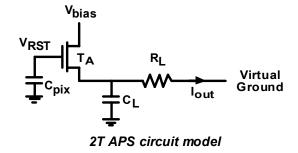

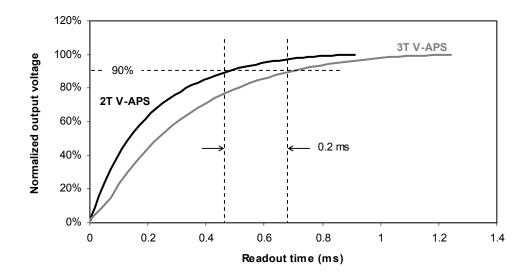

The operation of APS consists of three steps: *Reset*, *Integration*, and *Readout* [1]. A transistor switch, T2, is used to reset the pixel sensor to a preset voltage prior to integration. The collected charges during integration are deposited on the pixel capacitor,  $C_{pix}$ , modulating its preset voltage. To read the pixel value, transistor T3 is switched on and the voltage of the pixel sensor is buffered out by transistor T1. Depending on the type of column amplifier connected to the APS imager, the output of the APS circuit can be read either in terms of voltage, which is called voltage mediated APS (V-APS), or in terms of current, in which case, the APS pixel is called current mode (or current mediated) APS (C-APS).

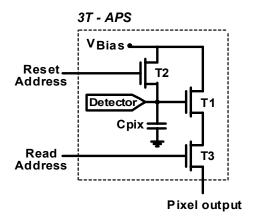

# 2.2.3 Voltage mediated APS

A voltage buffer (or a voltage amplifier) is used as the column amplifier of a V-APS imager, with a load resistance across which the output voltage is dropped (Fig. 2.4) [8]. During readout when transistor T3 is switched on, the drain current of T1 charges up the parasitic line capacitance of the data line and the voltage at the input of the column

voltage buffer reaches the value of  $\frac{R_{load}}{R_{load} + R_{ON}} (V_{pix} - V_t)$ . The time variation of the output voltage is approximated with a single pole system having a single the constant of  $(R_{ON} \parallel R_{Load})$   $C_{Line}$ . Therefore the output voltage of the V-APS is approximated by:

$$V_{out V-APS} \approx \frac{R_{load}}{R_{load} + R_{ON}} \left( V_{RST} - V_t - \frac{Q_{sig}}{C_{Pix}} \right) \left( 1 - e^{-t/R_{ON} ||R_{load}C_{Line}} \right)$$

(2.11)

Here, the  $V_{RST} - Q_{sig}/C_{Pix}$  is the pixel voltage at the end of the integration period when  $Q_{sig}$  has been deposited on the pixel capacitor  $C_{Pix}$ , and t is the readout time. As (2.11) shows,  $R_{Load}$  should be much higher than  $R_{ON}$  to have high enough output voltage. In that case, the time constant is mostly determined by  $R_{ON}$ . For readout times much larger than the time constant, the output voltage of the V-APS approaches  $V_{RST} - V_t - Q_{sig}/C_{Pix}$ ; gain of  $-1/C_{Pix}$ , and offset value of  $V_{RST} - V_t$ . The offset value is corrected by subtracting the image from a dark frame, which is called *Double Sampling*. That is, the output voltage containing image information is subtracted from a previously read value of the output voltage with no radiation (i.e., when  $Q_{sig} = 0$ ). Double sampling makes the output independent of inevitable variations in  $V_t$  across the large area imager. Therefore, the final DS corrected value of the output voltage for V-APS architecture is described as:

$$\Delta V_{outV-APS} = V_{out} \Big|_{Qsig=0} - V_{out} \Big|_{Qsig\neq0} = \frac{Q_{sig}}{C_{Pix}}$$

(2.12)

$$Gain_{V-APS} = \frac{\Delta V_{out\ V-APS}}{Q_{sig}} = \frac{1}{C_{Pix}}$$

(2.13)

As described by Eqn. 2.13, the V-APS charge to voltage conversion gain of  $1/C_{Pix}$  would be high if the pixel sensor capacitance is kept as low as possible, which enables detection of very weak signal charges, while the architecture is amenable to noise because the voltage at the input of the column voltage buffer is not attenuated. However, because of

the long RC time constant associated with the high ON state resistance of T3 a-Si TFT,  $R_{ON}$ , and large value of parasitic capacitance of the data lines,  $C_{Line}$ , the readout time of V-APS architecture is long, and therefore the architecture is not suitable for fast imaging if the large area FPI is fabricated using a-Si technology. The most important aspect of V-APS is that, the voltage at the input of the column amplifier is almost equal to the detector node voltage and is not attenuated the way it is in PPS with voltage amplifier. This provides the possibility of using inexpensive voltage buffers in place of charge integrators for column amplifier without comprising the noise performance of the imager. Equation 2.13 shows that the charge to voltage conversion gain of the V-APS is 1 V/pC in the best scenario [8].

Figure 2.6. (a): Diagram of a V-APS architecture. (b): The circuit model in *Readout* mode

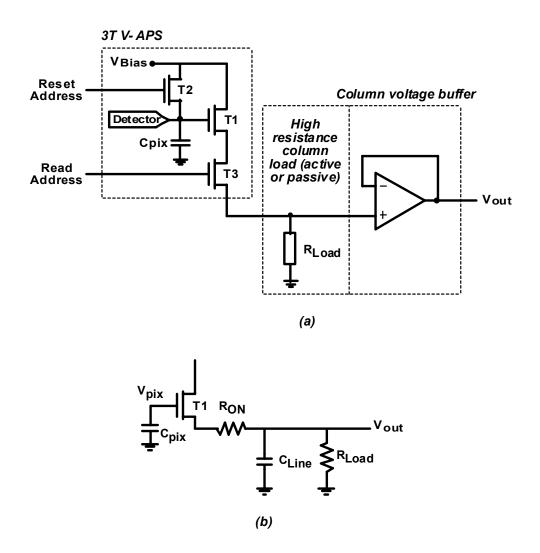

## 2.2.4 Current mediated APS

In order to suppress the long time-constant associated with the V-APS readout, current mediated active pixel sensor is developed [9] in which the data line is virtually grounded by a high gain charge amplifier or a trans-impedance amplifier more or less the same as in PPS described previously (Fig. 2.2).

Figure 2.7. (a): Illustration of C-APS architecture with current integrator. (b) Transimpedance amplifier that can be used in place of the current integrator as the column amplifier. (c): The pixel circuit model in *Readout* mode

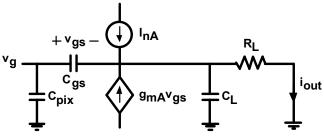

Figure 2.7 shows the C-APS pixel circuit connected to the column amplifier which can be a current integrator or a transimpedance amplifier. The pixel output current of a C-APS architecture (Fig. 2.7.c) is derived as a function of pixel sensor voltage at the pixel sensor capacitance,  $V_{pix}$  [9].

$$i_D = \frac{1 + KR_{ON}(V_{Pix} - V_t) - \sqrt{1 + 2KR_{ON}(V_{Pix} - V_t)}}{KR_{ON}^2}$$

(2.14)

In which K is the gain factor ( $C_0 \mu_{FE} W/L$ ) of the AMP TFT, and  $V_{Pix}$  is equal to  $V_{RST} - Q_{sig}/C_{Pix}$ . With double sampling, the change in the drain current is attributed to  $Q_{sig}$  and can be expressed as a linear function for small variations in  $Q_{sig}$ .

$$\Delta i_{D} = i_{D} \Big|_{Qsig=0} - i_{D} \Big|_{Qsig\neq0} = \frac{1}{R_{ON}} \left( 1 - \frac{1}{\sqrt{1 + 2KR_{ON}(V_{RST} - V_{t})}} \right) \frac{Q_{sig}}{C_{Pix}}$$

(2.15)

In case a trans-impedance amplifier is used, the change in output current is converted to a voltage change at the output of the trans-impedance amplifier.

$$\Delta V_{out} = \frac{R_f}{R_{ON}} \left( 1 - \frac{1}{\sqrt{1 + 2KR_{ON}(V_{RST} - V_t)}} \right) \frac{Q_{sig}}{C_{Pix}}$$

(2.16)

The gain of the APS architecture, with a trans-impedance amplifier here, is defined as the ratio of changes in the output voltage to the signal charge, or:

$$Gain_{C-APS} = \frac{\Delta V_{out}}{Q_{sig}} = \frac{R_f}{C_{Pix}R_{ON}} \left( 1 - \frac{1}{\sqrt{1 + 2KR_{ON}(V_{RST} - V_t)}} \right)$$

(2.17)

Compared to the gain of V-APS from Eqn. 2.13 which is  $1/C_{Pix}$ , by proper choice of feed back resistor and proper design of the READ and AMP transistor, the C-APS gain could be larger than pixel gain of V-APS.

Charge amplifiers can also be used for column readout circuitry, in that case, the output current is integrated over the readout time to build the output voltage on the feedback capacitor of the charge amplifier. The gain of the C-APS with charge amplifier Eqn. 2.16, is derived similar to Eqn. 2.17.

$$Gain_{C-APS} = \frac{\Delta V_{out}}{Q_{sig}} = \frac{t_{int}}{C_{Pix}C_{f}R_{ON}} \left(1 - \frac{1}{\sqrt{1 + 2KR_{ON}(V_{RST} - V_{t})}}\right)$$

(2.18)

Equation (2.18) shows a time varying gain, which is interesting from static and real time imaging applications point of view, for providing a method of linear gain control.

Table 2.2. Nominal values of parameters for C-APS architecture

| Parameter                                                    | Value                            | Parameter                            | Value                  |

|--------------------------------------------------------------|----------------------------------|--------------------------------------|------------------------|

| $\mu_{\mathit{FE}}$                                          | $0.5 \text{ cm}^2/\text{Vs}$     | $C_{pix}$                            | 0.5 pF                 |

| $C_{	heta}$                                                  | 20.0 nF/cm <sup>2</sup>          | $C_{Line}$                           | 190 pF                 |

| W/L                                                          | $100~\mu\text{m}/10~\mu\text{m}$ | $R_{Line}$                           | $1.0~\mathrm{k}\Omega$ |

| $R_f$                                                        | 1 MΩ                             | $	au_{TR}$                           | 0.5 μs                 |

| $V_{read} - V_t$                                             | 10.0 V                           | $C_f$                                | 0.5 pF                 |

| $R_{ON}$                                                     | $1.0~\mathrm{M}\Omega$           | $V_{RST} - V_t$                      | 10.0 V                 |

| K                                                            | $0.1 \ \mu A/V^2$                | $t_{int}$                            | 5 μs                   |

| $V_{out\ C-APS}/	extbf{	extit{Q}}_{sig} \ 	ext{(Eqn. 2.17)}$ | 2.0 V/pC                         | $V_{out\ C-PPS}/Q_{sig}$ (Eqn. 2.18) | 8.45 V/pC              |

Comparing this result with those for V-APS and PPS, we see that we have on-pixel gain. The fact is that increasing the integration time will increase the gain. For example, in tint is taken to be  $10~\mu s$ , then the C-APS gain would be 16.9~V/pC resulted from Eqn. 2.18. This high value of the pixel gain helps detection of weak signals.

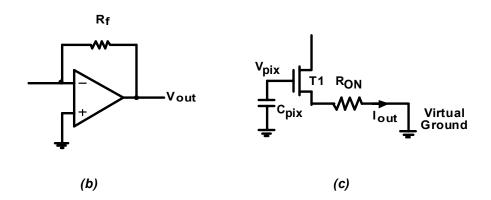

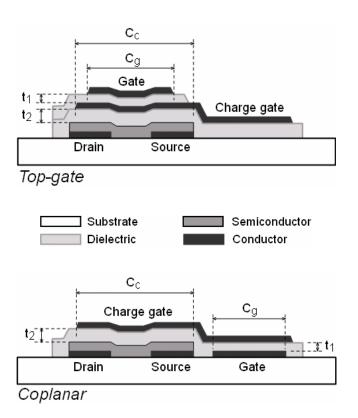

# 2.3 Hybrid pixel designs

Because of providing gain, APS is particularly a suitable architecture for low dose applications, such as fluoroscopy. However, for higher dose modalities such as chest radiography and mammography where the changes in the sensor signal is large, the inherent nonlinearity of C-APS becomes a big issue. Hybrid passive-active pixel architectures are one solution for this problem (Fig. 2.8) [10]. Depending on dose level, it is possible to read the pixel output both in PPS or APS, providing high gain for low

dynamic range modalities such as fluoroscopy, and linear response and high dynamic range for high dose modalities such as mammography.

Figure 2.8. Hybrid pixel architecture, employing both PPS and APS

Because of increased transistor and line counts per pixel [11] which inversely affect pixel size and resolution as well as fabrication reliability, four-transistor hybrid designs are not considered for high resolution large area digital imaging applications here in this thesis.

# **Bibliography**

- [1]: K.S. Karim, "Pixel Architectures for Digital Imaging Using Amorphous Silicon Technology", Ph.D. Thesis, University Of Waterloo, 2002.

- [2]: I. Fujieda, R.A. Street, R.L. Weisfield, S. Nelson, P. Nylen, V. Perez-Mendez, and G. Cho, "High Sensitivity Readout of 2D a-Si Image Sensors," Japan Journal of Applied Physics, 32, pp. 198-204, 1993.

- [3]: W. Zhao and J. A. Rowlands, "Digital radiology using active matrix readout of amorphous selenium: Theoretical analysis of detective quantum efficiency," Medical Physics, 24(12), pp. 1819-1833, 1997.

- [4]: <a href="http://www.japancorp.net/Article.Asp?Art\_ID=5742">http://www.japancorp.net/Article.Asp?Art\_ID=5742</a>, accessed on: Thursday, May 01, 2008.

- [5]: Karim, K.S., Nathan, A., Rowlands, J.A., Kasap, S.O., 'X-ray detector with on-pixel amplification for large area diagnostic medical imaging,' IEE Proceedings on Circuits, Devices and Systems, 2003, 150, (4), pp. 267-273.

- [6]: Karim, K.S., Nathan, A., Rowlands, J.A., 'Amorphous silicon pixel amplifier with VT compensation for low noise digital fluoroscopy', IEEE International Electron Devices Meeting (IEDM) Technical Digest, 2002, pp. 215-218.

- [7]: street Poly APS

- [8]: K.S. Karim, A. Nathan, J.A. Rowlands, "Active pixel sensor architectures in a-Si:H for medical imaaging," Journal of Vacuum Science and Technology A, 20(3), pp. 1095-1099, May 2002.

- [9]: K.S. Karim, A. Nathan, J.A. Rowlands, "Amorphous silicon active pixel sensor readout circuit for digital imaging," IEEE Transactions on Electron Devices: Special Issue on Image Sensors, 50(1), pp.200-208, January 2003.

- [10]: M.H. Izadi, K.S. Karim, A. Nathan, J.A. Rowlands, "Low-Noise Pixel Architectures for Advanced Diagnostic Medical X-ray Imaging Applications," in SPIE Medical Imaging 2006: Physics of Medical Imaging, Feb 2006.

- [11]: M.H. Izadi, K.S. Karim, "High dynamic range pixel architecture for advanced diagnostic medical X-ray imaging applications," Journal of Vacuum Science and Technology A, 24(3), pp 846-849, May 2006.

# 3

# High Resolution Pixel Architectures

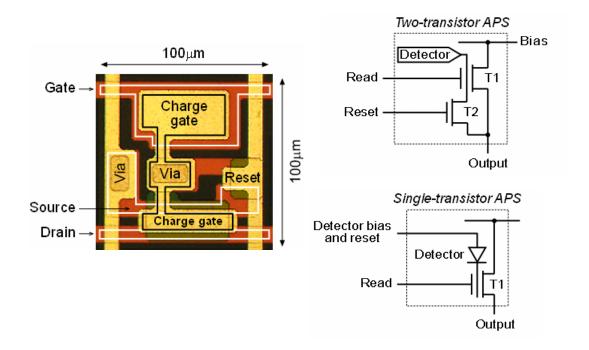

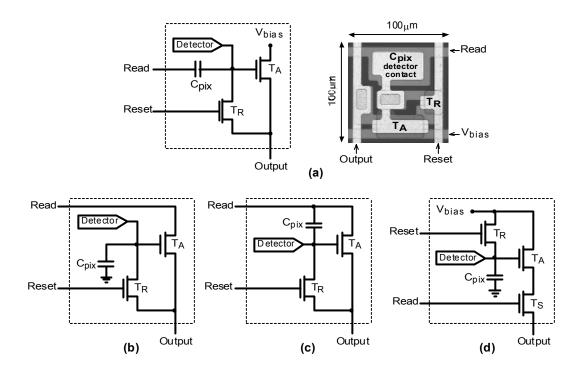

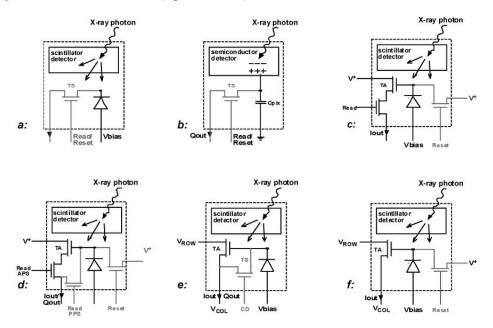

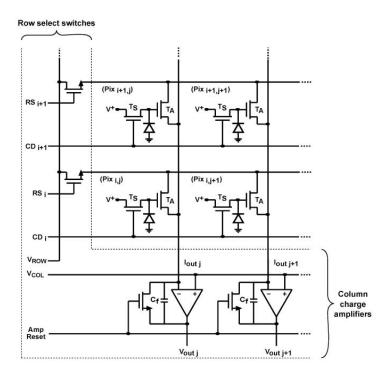

This chapter which is in fact the summary of a few publications (see Appendix B), introduces a new generation of pixel architectures for high resolution low noise large area imagers as the core of this thesis on pixel circuit design. The novel architectures are designed based on a two-transistor (2T) hybrid active/passive architecture where the main thin film transistor of the pixel circuit operates switched amplifier, eliminating the need for a row-select (or read) transistor that appears in the standard APS architecture. This has been made possible by employing a novel charge-gated thin film transistor. Different 2T pixel architectures are compared and contrasted with existing architectures (previously studied in chapter 2) based on their performance, fabrication reliability and imager system complexity. Criteria such as on-pixel gain, input referred noise and pixel size are used for performance evaluation, whereas, architecture complexity, density of transistors and number of lines per pixel are the measures for fabrication reliability. Finally, circuit requirements for operating the imager such as driving and signal processing circuits and their compatibility with the existing flat panel technology are discussed to evaluate system complexity of images fabricated using such pixel architectures.

# 3.1 Charge-Gated Thin Film Transistor

### 3.1.1 Introduction

Thin film transistors (TFTs) originally developed as switching elements for large area active matrix liquid crystal displays (AMLCDs) and flat panel imagers [1, 2] are finding analog applications such as current drivers in Organic LED displays [3] or as amplifiers in active pixel sensor (APS) imaging arrays [4]. The analog implementation is a result of advances in amorphous silicon (a-Si) fabrication technology, as well as use of innovative circuits to overcome speed, stability and noise shortcomings in the a-Si material [5].

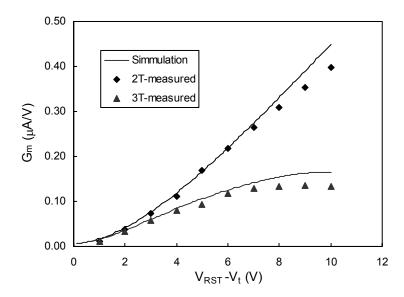

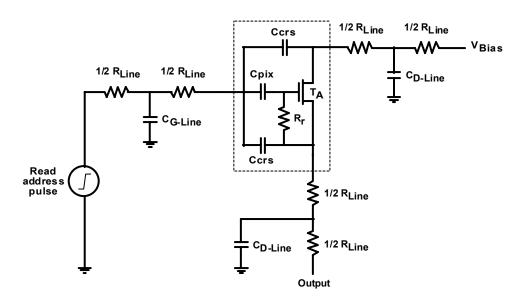

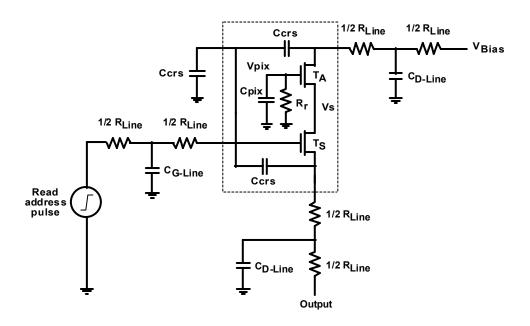

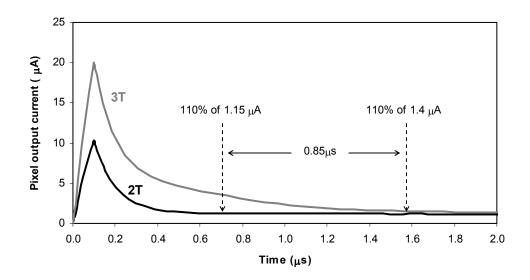

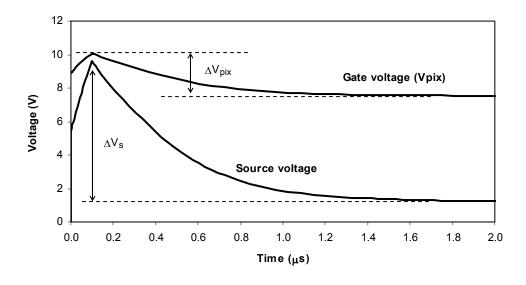

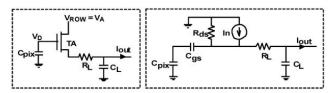

Compared to crystalline silicon transistors implemented a-Si TFTs are large in size. Therefore, employing TFT circuits at the pixel level requires minimizing pixel transistor counts for high resolution applications, as well as reducing gate/data line interconnections to reduce reliability issues in large area fabrication. In large area sensor arrays using a classic three transistor (3T) APS architecture for example [6], electric charge generated in the pixel detector, e.g., an amorphous selenium photoconductor, is deposited on the pixel storage capacitor connected to the gate of an amplifying transistor. The amplifying transistor is connected to the column output line by an addressing switch transistor and yet another switch transistor is used to reset the sensor node voltage.

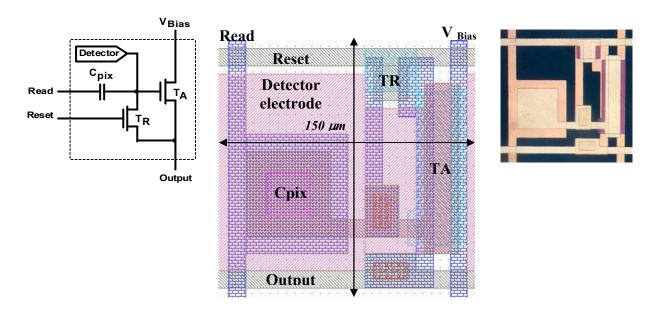

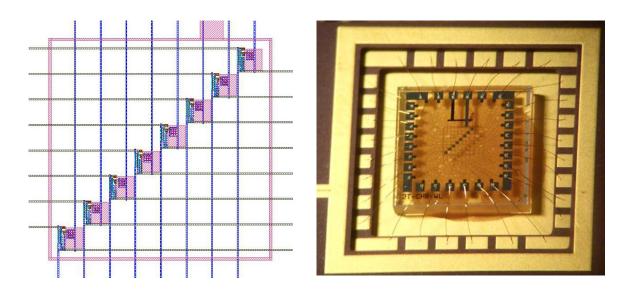

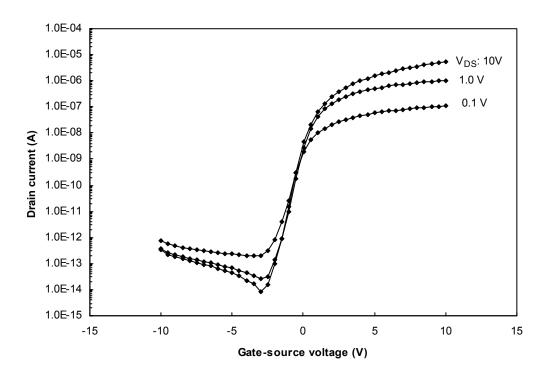

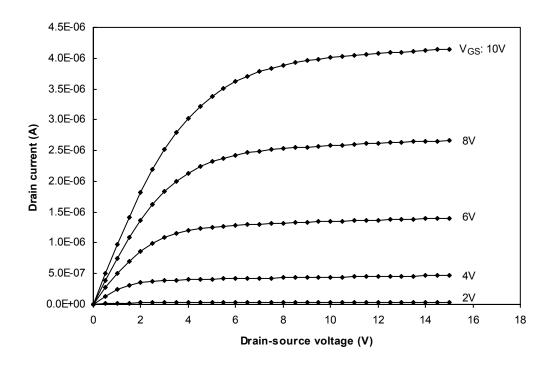

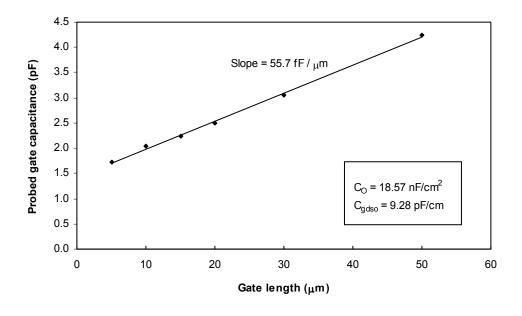

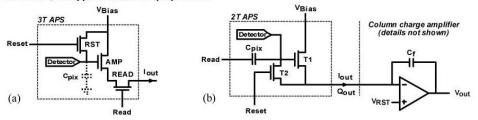

In this section, a charge-gated TFT (CG-TFT) capable of integrating the sensor charge as well as switching its output current ON and OFF is introduced to replace the amplifier and readout TFT in the 3T APS architecture; The readout circuit fabricated using CG-TFT was reported to IEEE International Electron Devices Meeting (IEDM 2007) [7].

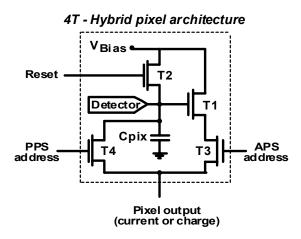

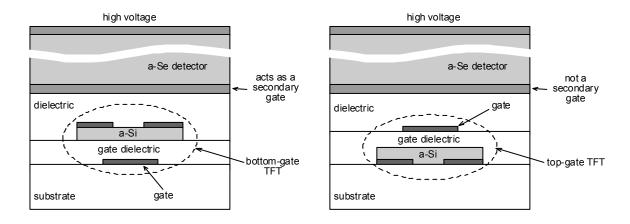

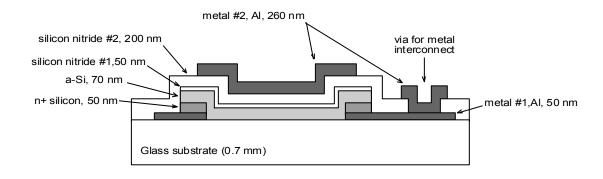

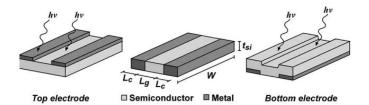

# 3.1.2 Charge-gated TFT

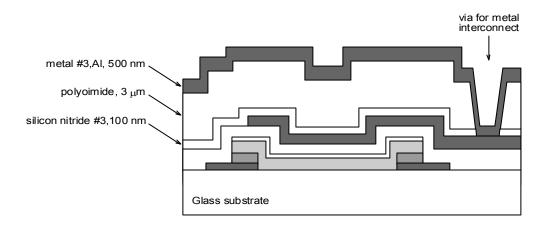

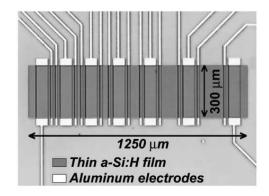

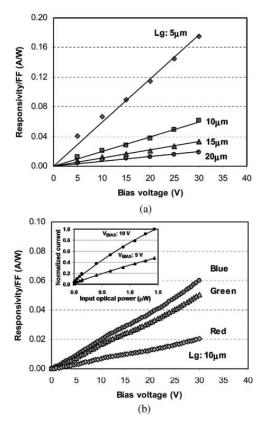

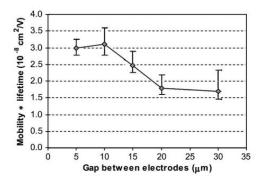

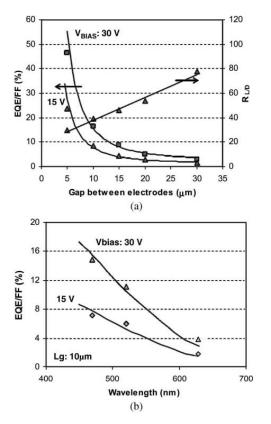

A charge gated transistor is obtained when a second gate (i.e. the charge gate) is introduced between the traditional gate and semiconductor layer of a field effect transistor. Fig. 3.1 shows two configurations of a staggered top gate TFT with the charge gate between the gate and the semiconducting channel. The charge gate is electrically

floating, i.e., it is embedded inside the insulating gate dielectric, and connected to a high resistance, low parasitic capacitance photoconductive detector, e.g., amorphous selenium. Fig. 3.1 shows two implementations of the charge gated TFT, the latter, a bottom gate coplanar configuration is sometimes preferable because it requires fewer masks and fabrication steps, as well as providing a completely exposed charge gate electrode for direct contact to an overlying detector. Because the charge gate is electrically conductive, the two device configurations shown in Fig. 3.1 are electrically identical. In either case, the gate is capacitively coupled to the TFT channel via the charge gate. The coupling capacitance between the gate and the charge gate is  $C_g$ , and the capacitance between the charge gate and the channel (including overlap) is  $C_c$ . The dielectric thickness for these capacitances is not necessarily the same and can be optimized independently. For example, in the coplanar configuration of Fig. 3.1,  $t_I$  is always smaller than  $t_2$  when a fabrication process using double dielectric deposition is used [8].

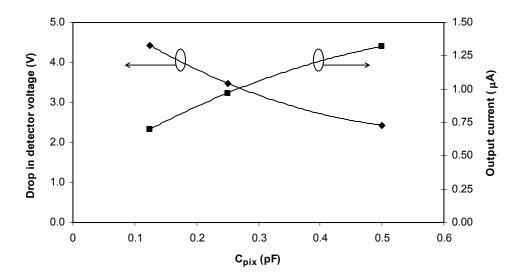

Fig. 3.1. Cross-section of charge-gated field effect transistors in a top gate and coplanar configuration - the two devices are electrically identical

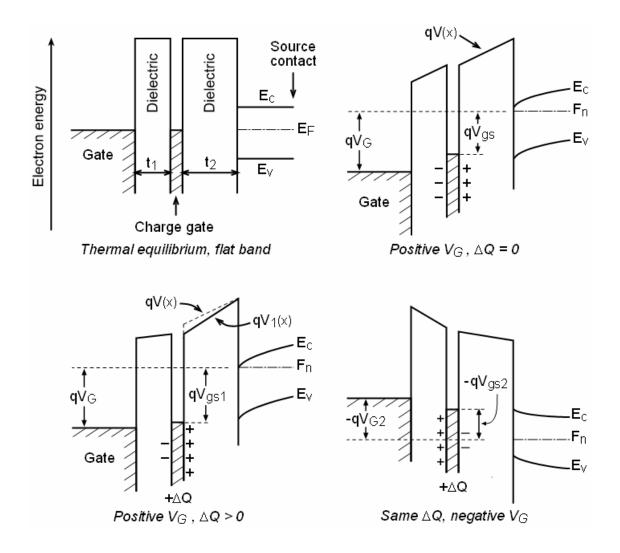

The electronic band diagrams of the device are shown in Fig. 3.2. Assuming zero flat band voltage when gate and source voltages are zero and the same area for  $C_g$  and  $C_c$ , the device is normally biased as a conventional TFT and the potential of the floating charge gate with respect to source,  $V_{gs}$ , follows the potential induced by the gate due to the applied gate voltage,  $V_G$ . When  $F_n$ , the quasi Fermi level for electrons, is close to the conduction band, we neglect small variations of semiconductor surface potential (since  $F_n$  is effectively pinned due to the channel screening effect) compared to the large changes in applied  $V_G$ . Thus,  $V_{gs}$  is approximated as:

$$V_{gs} \approx \frac{C_g}{C_g + C_c} V_G \tag{3.1}$$

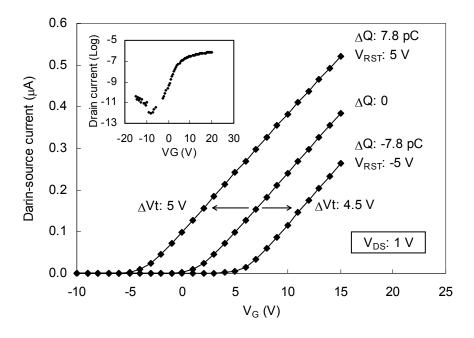

A large enough  $V_G$  increases  $V_{gs}$  to allow accumulation of carriers in the channel for the device to turn ON. When positive electric charge is deposited on the charge gate, as shown in Fig. 3.2,  $V_{gs}$  increases to  $V_{gsI}$ , and subsequently increases the carrier concentration in the channel, in spite of the constant gate voltage,  $V_G$ . Deposition of negative charge results in a reduction of carrier concentration in the channel, which allows the current conduction in the channel to be modulated by charge deposited on the charge gate. Even with positive charge on the charge gate, the device can be turned OFF (non-conducting) by applying a negative voltage to the gate as shown in Fig. 3.2.

The voltage difference between the charge gate and the source can be expressed as a function of  $V_G$ , and deposited charge,  $\Delta Q$ . Using the current equation for field effect transistors, the drain current of the CG-TFT can be obtained. The equivalent capacitance at the charge gate node is  $C_c + C_g$ , where  $C_c$  is approximately constant and given as,  $C_c \approx C_0 W(L_g + L_{ov})$ ,  $C_0 = \frac{\mathcal{E}_0 \mathcal{E}_r}{t_2}$ . Here,  $\mathcal{E}_r$  is the relative permittivity of the dielectric, W

and  $L_g$  are the channel width and length of the device and  $L_{ov}$  is the total overlap length of the charge gate on drain and source contacts. The amount of voltage change as the result of depositing  $\Delta Q$  on the gate charge is:

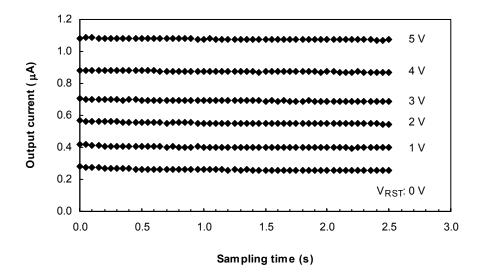

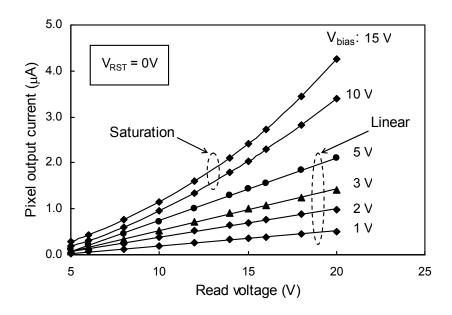

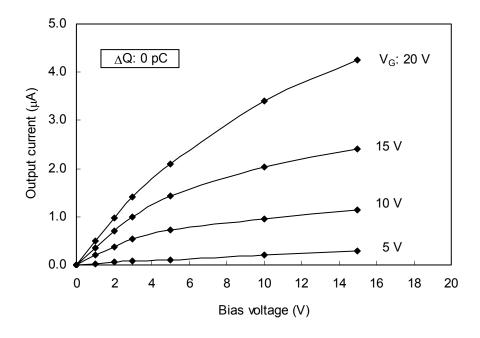

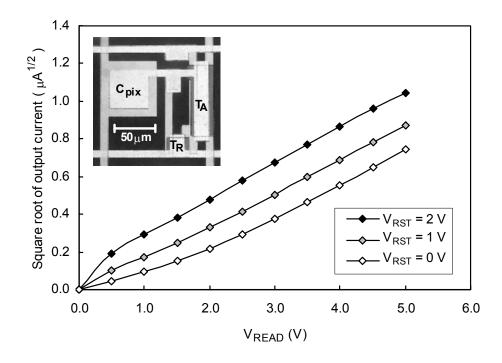

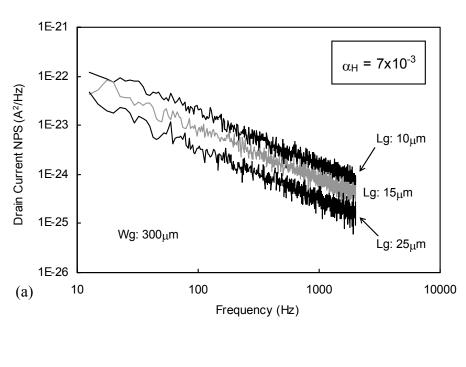

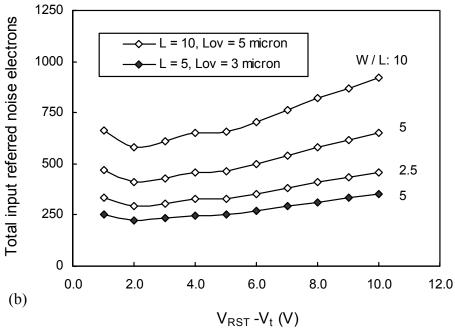

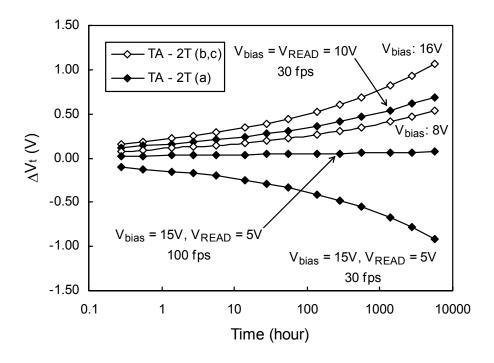

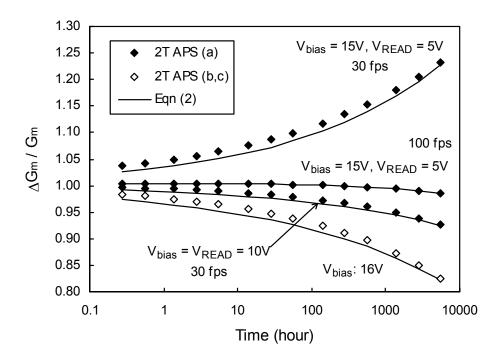

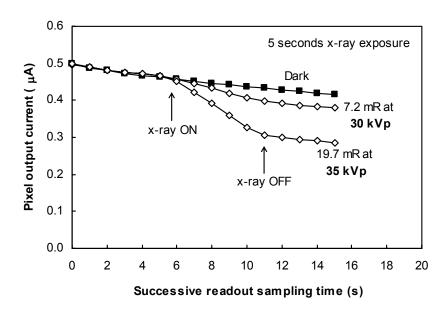

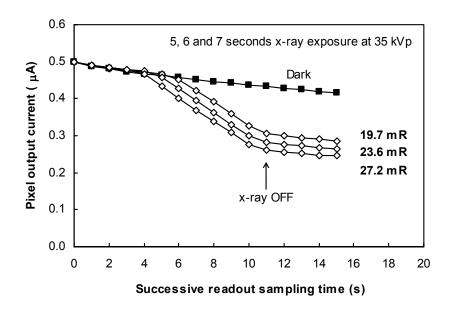

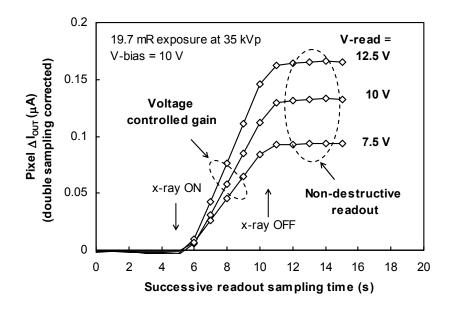

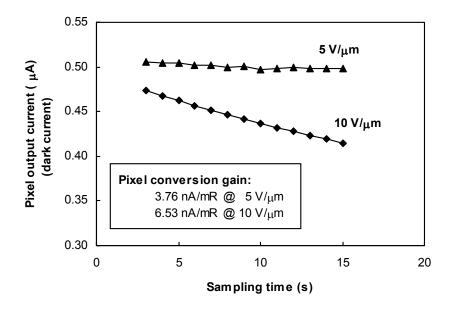

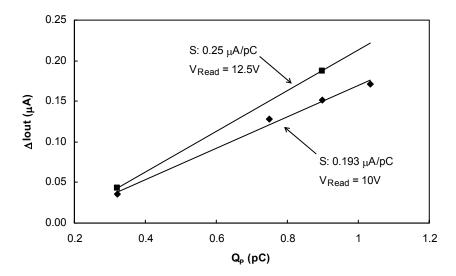

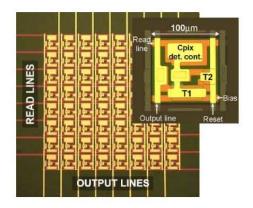

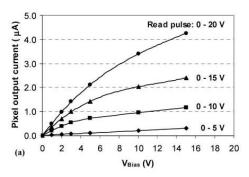

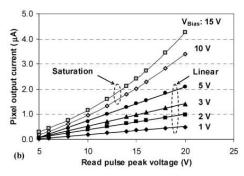

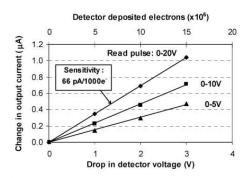

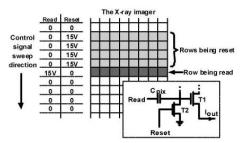

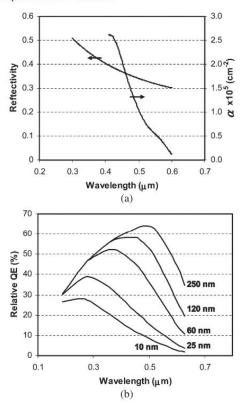

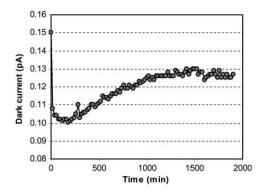

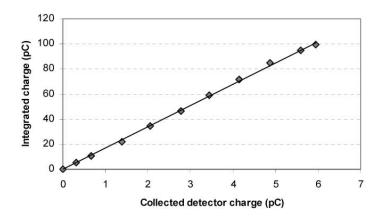

Fig. 3.2. Electronic band diagrams of a CG-TFT under different bias conditions (flat band, positive VG, positive VG with deposited charge,  $\Delta Q$  on the charge gate, negative VG with  $\Delta Q$  on charge gate).