# Nanocrystalline Silicon Thin Film Transistor

by

Mohammad-Reza Esmaeili-Rad

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Mohammad-Reza Esmaeili-Rad 2008

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

Mohammad-Reza Esmaeili-Rad

I understand that my thesis may be made electronically available to the public.

Mohammad-Reza Esmaeili-Rad

#### Abstract

Hydrogenated amorphous silicon ( $\alpha$ -Si:H) thin film transistor (TFT) has been used in active matrix liquid crystal displays (LCDs) and medical x-ray imagers, in which the TFT acts as pixel switches. However, instability of  $\alpha$ -Si:H TFT is a major issue in applications where TFTs are also required to function as analogue circuit elements, such as in emerging organic light emitting diode (OLED) displays. It is known that  $\alpha$ -Si:H TFT shows drain current degradation under electrical operation, due to two instability mechanisms: (i) defect creation in the  $\alpha$ -Si:H active layer, and (ii) charge trapping in the gate dielectric. Nanocrystalline silicon (nc-Si) TFT has been proposed as a high performance alternative. Therefore, this thesis focuses on the design of nc-Si TFT and its outstanding issues, in the industry standard bottom-gate structure.

The key for obtaining a stable TFT lies in developing a highly crystalline nc-Si active layer, without the so-called amorphous incubation layer. Therefore, processing of nc-Si by plasma enhanced chemical vapor deposition (PECVD) is studied and PECVD parameters are optimized. It is shown that very thin (15 nm) layers with crystallinity of around 60% can be obtained. Moreover, it is possible to eliminate the amorphous incubation layer, as transmission electron microscope (TEM) images showed that crystalline grains start growing immediately upon deposition at the gate dielectric interface.

The nc-Si TFT reported in this work advances the state-of-the-art, by demonstrating that defect state creation is absent in the nc-Si active layer, which is deduced by performing several characterization techniques. In addition, with the proper design of the nitride gate dielectric, i.e. by using a nitrogen-rich nitride, the charge trapping instability can be minimized. Thus, it is shown that the nc-Si TFT is much more stable than the  $\alpha$ -Si:H counterpart.

Another issue with nc-Si TFT is its high drain leakage current, i.e. off-current. It is shown that off-current is determined by the conductivity of nc-Si active layer, and also affected by the quality of the silicon/passivation nitride interface. The

off-current can be minimized by using a bi-layer structure so that a thin (15 nm) nc-Si is capped with a thin (35 nm)  $\alpha$ -Si:H, and values as low as 0.1 pA can be obtained.

The low off-current along with superior stability of nc-Si TFT, coupled with its fabrication in the industry standard 13.56 MHz PECVD system, make it very attractive for large area applications such as pixel drivers in active matrix OLED displays and x-ray imagers.

#### Acknowledgements

I am very grateful to my advisors, Professor Arokia Nathan and Professor Andrei Sazonov, for their sincere guidance through my time in the group. They provided me the freedom to do the research I was willing to, and the knowledge and support to make it successful. I would like to sincerely express my gratitude to Professor Tong Leung, Professor Amir Hamed Majedi, Professor Michael Shur, and Professor Siva Sivoththaman, in alphabetical order, for serving on my dissertation committee and reviewing my work.

I am indebted to many nice people who helped me to get my work done in the lab successfully. Dr. Czang-Ho Lee was my trainer who taught me the basics of PECVD and TFT fabrication. I sincerely thank my prolonged friends and research colleagues, Dr. Mahdi Farrokh Baroughi and Dr. Majid Gharghi, for their assistance and helpful discussions during the course of my work. We spent a lot of time chatting on lab issues such as not-working equipments and devices !. As well, sincere efforts of Richard Barber, Robert Mullins, and Randy Fagan in the Giga-to-Nanoelectronics Centre to keep equipments up and running are greatly appreciated.

I have non-erasable memories with wonderful friends such as Reza, Nader, Saeed, Arash, Kambiz, and Shahin. Having 3-4 cups of coffee a day is not recommended for health, but we did it for several years. There are many students and group-mates who have shaped my memories and experience in Waterloo, including Dr. Isaac Chan, Dr. Yuriy Vygranenko, Afrin Sultana, Flora Li, Hassan El-Gohary, Hyun Jung Lee, Dr. Jackson Lai, Dr. Jeff Hsin Chang, Kai Wang, Maryam Moradi, Ehsan Fathi, Khadijeh Bayat, Shah M. Jahinuzzaman (Jahin), and Dr. Denis Striakhilev. I have had the pleasure to spend my time with them.

I have enjoyed working with Flora during the development of nitride layers and also organizing the *Ontario Nano Symposium* in 2006. I am very grateful to Jahin and Afrin for providing data, on amorphous silicon TFTs, used in my 2007 APL paper. I am also very grateful to Mr. Fred Pearson of the Brockhouse Institute

for Materials Research, the McMaster University, for training me on TEM sample preparation and performing TEM on my nc-Si samples.

Special thanks go to the sponsors of my research, the Natural Sciences and Engineering Research Council of Canada (NSERC), the University of Waterloo, and the Government of Ontario. My Ontario Graduate Scholarship was partially supported by the Savvas Chamberlain Graduate Scholarship. Thus, I am very grateful to Dr. Savvas Chamberlain, from DALSA Corp., Waterloo, for providing this invaluable scholarship. It really helped me to focus on my research, instead of worrying about financial matters.

Finally, I would like to thank my wonderful parents for their unconditional love and support. I am particularly grateful to my angel, Zahra, for her endless patience, support, and love.

#### Dedication

To my parents and wife, Zahra

## Contents

| 1 | Intr | roducti | ion                                                     | 1  |

|---|------|---------|---------------------------------------------------------|----|

|   | 1.1  | Macro   | pelectronics                                            | 1  |

|   | 1.2  | Active  | e Matrix Arrays                                         | 2  |

|   | 1.3  | Thin 1  | Film Materials and Transistor Technologies              | 6  |

|   |      | 1.3.1   | Hydrogenated Amorphous Silicon                          | 6  |

|   |      | 1.3.2   | Polycrystalline Silicon                                 | 9  |

|   |      | 1.3.3   | Nanocrystalline Silicon                                 | 12 |

|   | 1.4  | Challe  | enges for Nanocrystalline Silicon Thin Film Transistors | 14 |

|   |      | 1.4.1   | Top-gate Structure                                      | 14 |

|   |      | 1.4.2   | Bottom-gate Structure                                   | 15 |

|   | 1.5  | Objec   | tives of the Research                                   | 17 |

|   | 1.6  | Thesis  | s Organization                                          | 18 |

| 2 | Thi  | n Film  | Transistors                                             | 19 |

|   | 2.1  | Introd  | luction                                                 | 19 |

|   | 2.2  | Fabric  | eation of Thin Film Transistors                         | 20 |

|   | 2.3  | Opera   | tion and Physics of Thin Film Transistors               | 22 |

|   |      | 2.3.1   | Mechanisms of Drain Leakage Current                     | 25 |

|   | 2.4                      | Electrical Instability of Thin Film Transistors                                 | 28                   |

|---|--------------------------|---------------------------------------------------------------------------------|----------------------|

|   |                          | 2.4.1 Metastability of Amorphous Silicon                                        | 28                   |

|   |                          | 2.4.2 Thermalization Energy Concept                                             | 30                   |

|   |                          | 2.4.3 Charge Trapping in Silicon Nitride Dielectric                             | 32                   |

|   |                          | 2.4.4 Constant Voltage and Constant Current Stressing                           | 35                   |

|   | 2.5                      | Summary                                                                         | 37                   |

| 3 | Ma                       | terials Optimization for Nanocrystalline Silicon Thin Film                      |                      |

|   | Tra                      | nsistors                                                                        | 40                   |

|   | 3.1                      | Introduction                                                                    | 40                   |

|   | 3.2                      | Nanocrystalline Silicon Active Layer                                            | 41                   |

|   | 3.3                      | Silicon Nitride Gate Dielectric                                                 | 51                   |

|   | 3.4                      | Summary                                                                         | 56                   |

| 4 | Nar                      | nocrystalline Silicon Thin Film Transistor Structures                           | 59                   |

|   | 4.1                      | Introduction                                                                    | 59                   |

|   | 4.2                      | TFT Fabrication                                                                 | 60                   |

|   | 4.3                      |                                                                                 |                      |

|   |                          | Results and Discussion                                                          | 61                   |

|   | 4.4                      | nc-Si TFT Modeling and Simulation of Transfer Characteristics                   |                      |

|   |                          |                                                                                 | 63                   |

|   | 4.4                      | nc-Si TFT Modeling and Simulation of Transfer Characteristics                   | 63<br>72             |

|   | 4.4                      | nc-Si TFT Modeling and Simulation of Transfer Characteristics Optimum Structure | 63<br>72<br>79       |

| 5 | 4.4<br>4.5<br>4.6<br>4.7 | nc-Si TFT Modeling and Simulation of Transfer Characteristics Optimum Structure | 63<br>72<br>79       |

| 5 | 4.4<br>4.5<br>4.6<br>4.7 | nc-Si TFT Modeling and Simulation of Transfer Characteristics Optimum Structure | 63<br>72<br>79<br>84 |

|              |       | 5.2.1   | Threshold Voltage Shift under Constant Current Stress | 87              |  |  |

|--------------|-------|---------|-------------------------------------------------------|-----------------|--|--|

|              |       | 5.2.2   | Relaxation of Threshold Voltage Shift                 | 93              |  |  |

|              |       | 5.2.3   | Threshold Voltage Shift under Constant Voltage Stress | 96              |  |  |

|              | 5.3   | Summ    | ary                                                   | 103             |  |  |

| 6            | Con   | clusio  | ns                                                    | 106             |  |  |

|              | 6.1   | Conclu  | usions and Contributions                              | 108             |  |  |

|              | 6.2   | Recom   | amendations for Future Work                           | 111             |  |  |

| $\mathbf{A}$ | List  | of Pu   | blications                                            | 113             |  |  |

|              | A.1   | Journa  | als                                                   | 113             |  |  |

|              | A.2   | Refere  | ed Conference Papers                                  | 114             |  |  |

|              | A.3   | Confer  | rence Presentations                                   | 114             |  |  |

| В            | Med   | lici Co | de for TFT Simulation                                 | 116             |  |  |

| Bi           | bliog | graphy  |                                                       | ibliography 121 |  |  |

## List of Tables

| 1.1 | Attributes of poly-Si and $\alpha$ -Si:H TFT technologies. From Ref. [9].                                                              | 11 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | The PECVD parameters for nine experiments, based on the Taguchi orthogonal array [56]                                                  | 43 |

| 3.2 | The results of measurements and characterizations performed on the thin films where their PECVD parameters are given in Table $3.1.$ . | 44 |

| 3.3 | The PECVD parameters for the three silicon nitride films                                                                               | 53 |

| 4.1 | Summary of measurement and simulation parameters                                                                                       | 71 |

| 4.2 | Summary of performance parameters of the three TFTs                                                                                    | 83 |

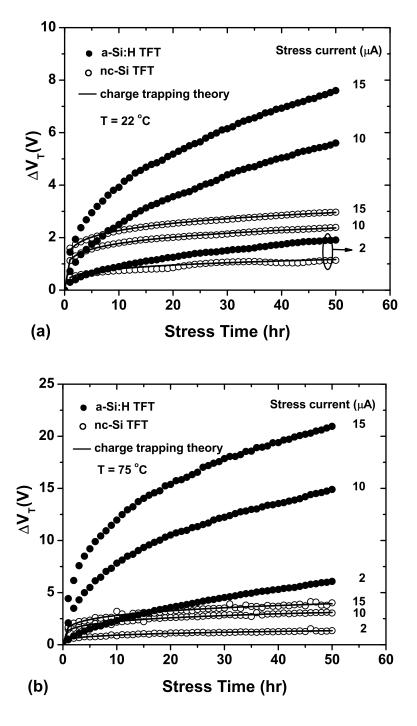

| 5.1 | Parameter values for equation (2.6) resulting from fit to measured data indicated in Figs. 5.1 (a) and (b)                             | 89 |

## List of Figures

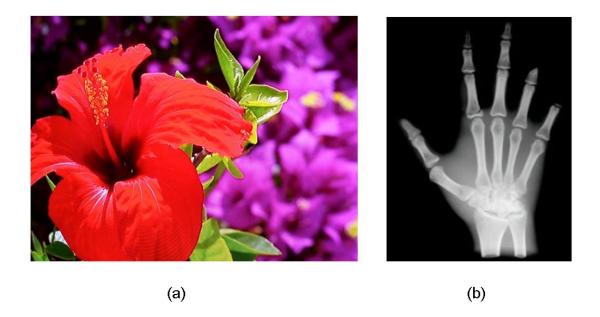

| 1.1 | The panel outputs generated by an (a) OLED display and (b) x-ray imager. Pictures are from [6] and [7]                                           | 3  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

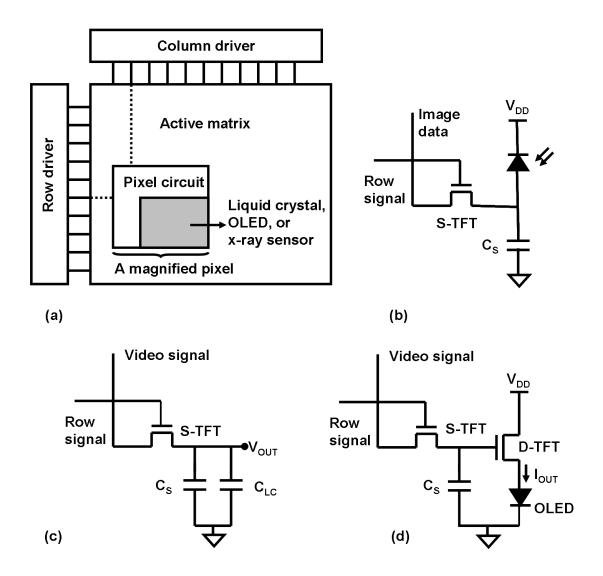

| 1.2 | (a) The concept of active matrix array, and basic pixel circuits in (b) x-ray imager, (c) liquid crystal display, and (d) organic light emitting |    |

|     | diode display                                                                                                                                    | 4  |

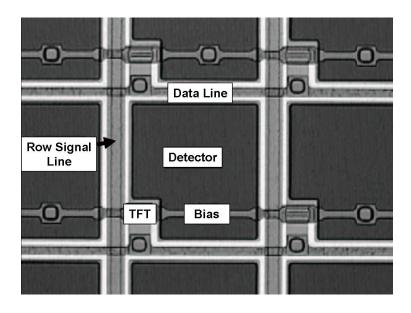

| 1.3 | Photomicrograph of an x-ray active matrix array. From Ref. [7]                                                                                   | 5  |

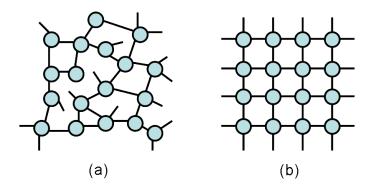

| 1.4 | Two dimensional representation of atomic bonding in (a) $\alpha$ -Si:H and                                                                       |    |

|     | (b) crystalline silicon (adapted from [10])                                                                                                      | 6  |

| 1.5 | Distribution of density of states in (a) $\alpha$ -Si:H and (b) crystalline                                                                      |    |

|     | silicon. Adapted from [10, 12]                                                                                                                   | 7  |

| 1.6 | Representative 2D atomic bonding in poly-Si (adapted from [10])                                                                                  | 10 |

| 1.7 | Two dimensional representation of atomic bonding in nc-Si (adapted                                                                               |    |

|     | from [24])                                                                                                                                       | 13 |

| 1.8 | Material structure of nc-Si. It is inhomogeneous and comprises of                                                                                |    |

|     | small grains near the substrate and larger grains when thickness                                                                                 |    |

|     | increases (adapted from [22])                                                                                                                    | 14 |

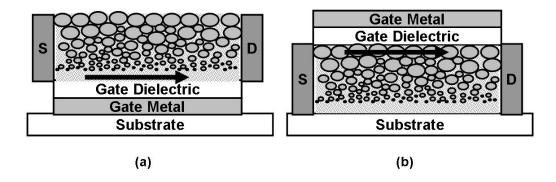

| 1.9 | Two nc-Si TFT structures, (a) bottom-gate and (b) top-gate. The                                                                                  |    |

|     | arrow represents the conduction path                                                                                                             | 14 |

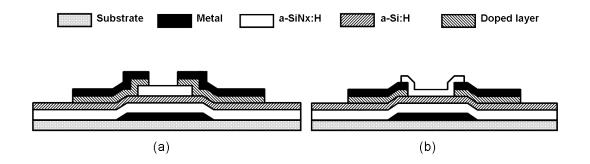

| 2.1 | Bottom-gate inverted-staggered TFT structures, (a) trilayer and (b)                                                                              |    |

|     | back channel etched. Adapted from [10, 40]                                                                                                       | 21 |

|     |                                                                                                                                                  |    |

| 2.2 | Fabrication sequence of the structure shown in Fig. 2.1 (a)                                                                                                                                          | 21 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.3 | Illustration of operation of a bottom-gate TFT when gate and drain biases are applied. Adapted from [13]                                                                                             | 22 |

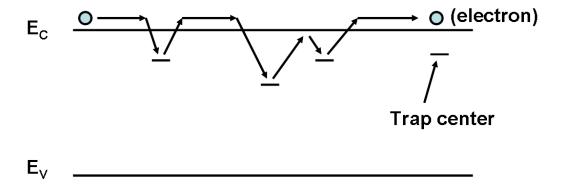

| 2.4 | A one-dimensional model showing the motion of electrons that are frequently trapped in and released from band tail states. Adapted from Ref. [11]                                                    | 23 |

| 2.5 | Typical I-V curve of a bottom-gate nc-Si or $\alpha$ -Si:H TFT                                                                                                                                       | 24 |

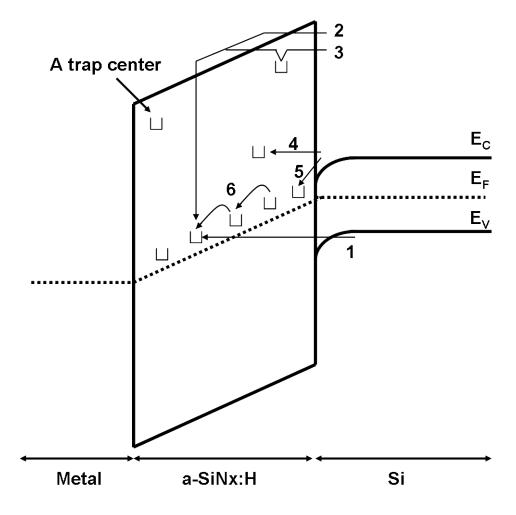

| 2.6 | The band diagrams for two models illustrating several mechanisms of leakage current. From Ref. [42].                                                                                                 | 27 |

| 2.7 | Threshold voltage shift of an $\alpha$ -Si:H TFT as a function of the thermalization energy. From Ref. [49]                                                                                          | 32 |

| 2.8 | Charge trapping mechanisms in silicon nitride. Adapted from Ref. [51]                                                                                                                                | 34 |

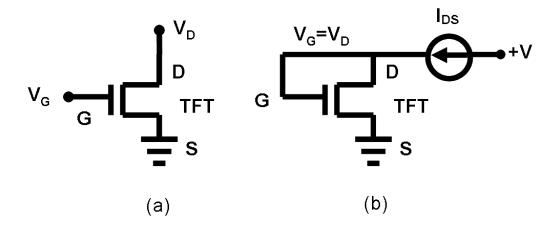

| 2.9 | A simple representation of the experimental setup, (a) constant voltage stressing and (b) diode connected configuration for constant current stressing                                               | 36 |

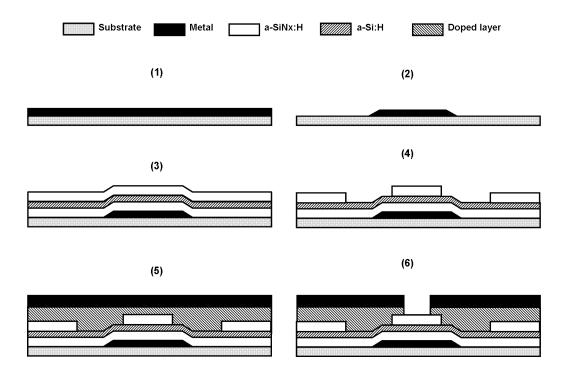

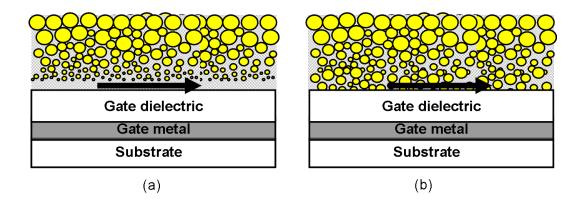

| 3.1 | The nc-Si active layer in a simplified bottom-gate TFT structure,  (a) with and (b) without amorphous incubation layer at the gate dielectric interface                                              | 42 |

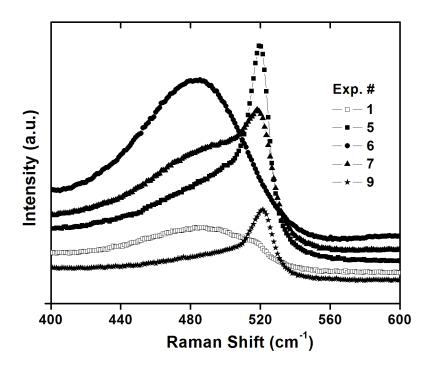

| 3.2 | Raman spectra of several thin films obtained from the experiments listed in Table 3.1                                                                                                                | 45 |

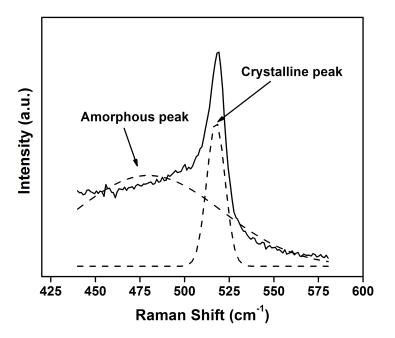

| 3.3 | Decomposing a Raman signal (solid line) into two Gaussian peaks (dashed lines) centered around $517 - 520cm^{-1}$ and $480cm^{-1}$ , which are due to crystalline and amorphous phases, respectively | 46 |

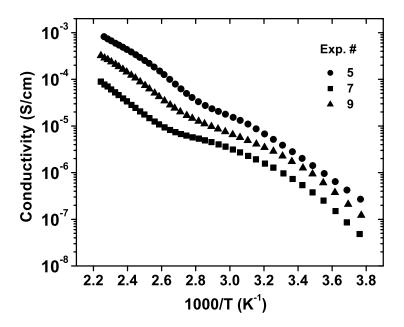

| 3.4 | Temperature dependence of the conductivity of several nc-Si layers, processed based on Table 3.1                                                                                                     | 47 |

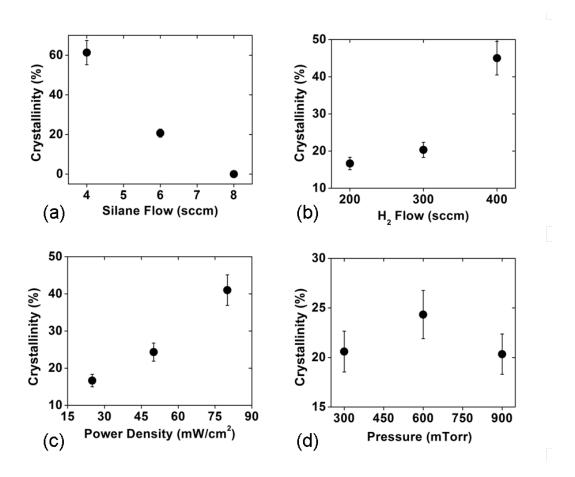

| 3.5 | The average crystallinity versus PECVD parameters                                                                                                                                                    | 48 |

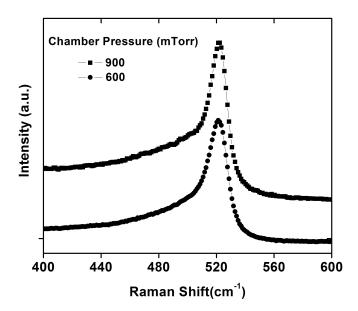

| 3.6  | Raman spectra of two nc-Si layers deposited at two chamber pressures (900 and 600 mTorr)                                                                                                                                                                 | 49 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

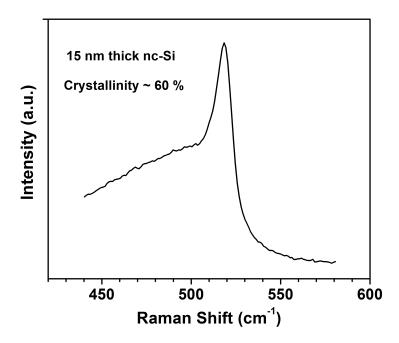

| 3.7  | Raman spectrum of a 15 nm thick nc-Si film. Its crystallinity is approximately 60%                                                                                                                                                                       | 50 |

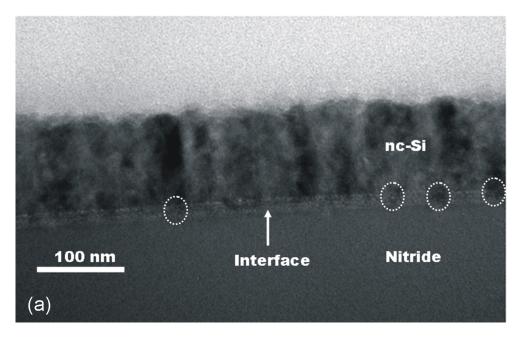

| 3.8  | Transmission electron microscope (TEM) cross section image of the nc-Si film                                                                                                                                                                             | 52 |

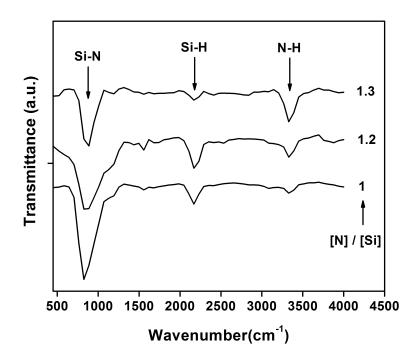

| 3.9  | FTIR spectra of various nitride films with [N]/[Si] of 1.3, 1.2, and 1, processed at $NH_3$ to $SiH_4$ of 20, 10, and 5, respectively                                                                                                                    | 54 |

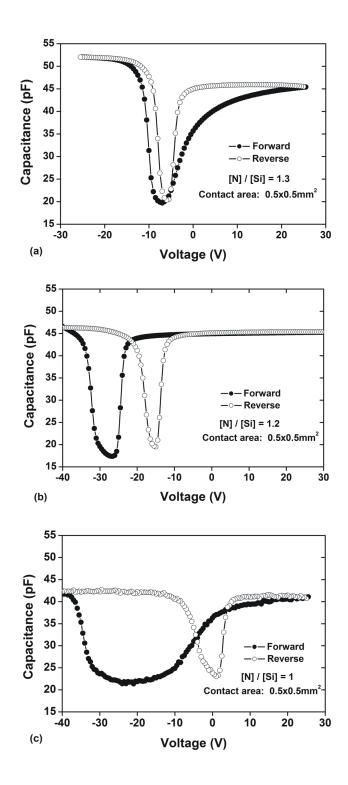

| 3.10 | Capacitance-voltage (C-V) characteristics of nitrides with [N]/[Si], (a) 1.3, (b) 1.2, and (c) 1. The curves were obtained by sweeping the voltage across MIS capacitors in forward (negative to positive) and reverse (positive to negative) directions | 55 |

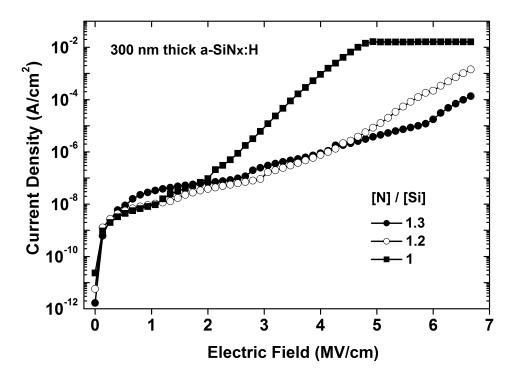

| 3.11 | Leakage current density as a function of electric field, for the silicon nitrides with [N]/[Si] of 1.3, 1.2, and 1, processed at $NH_3$ to $SiH_4$ of 20, 10, and 5, respectively                                                                        | 57 |

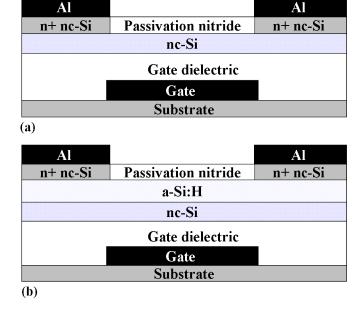

| 4.1  | Cross section of the inverted-staggered TFT structure, (a) single nc-Si channel layer in TFT A, (b) nc-Si capped with $\alpha$ -Si:H in TFT B                                                                                                            | 61 |

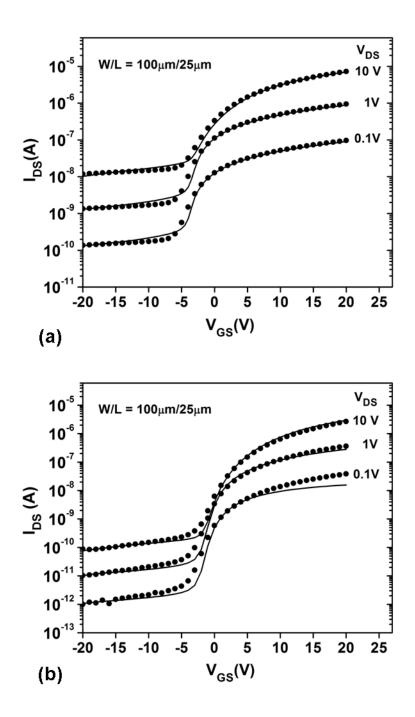

| 4.2  | Transfer characteristics of (a) TFT A with an all nc-Si channel layer of thickness $65nm$ and (b) TFT B with $65nm$ nc-Si channel layer capped with $100nm$ $\alpha$ -Si:H                                                                               | 62 |

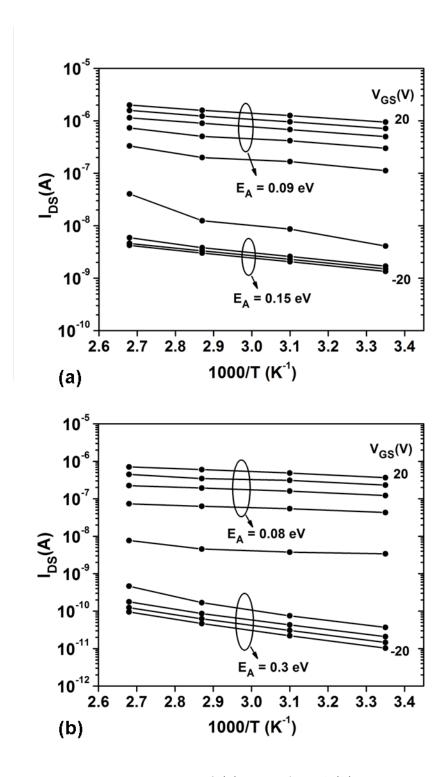

| 4.3  | Drain-source current of (a) TFT A and (b) TFT B, measured in the range of 25 to 100 °C at a drain voltage of 1 V, and different gate voltages                                                                                                            | 64 |

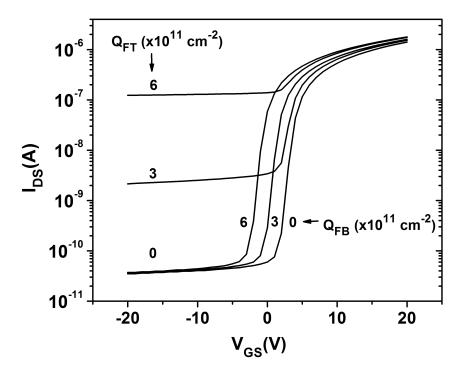

| 4.4  | Transfer characteristics computed at $V_{DS} = 1V$ , when the density of fixed charges at the gate dielectric interface and at the passivation nitride interface vary                                                                                    | 66 |

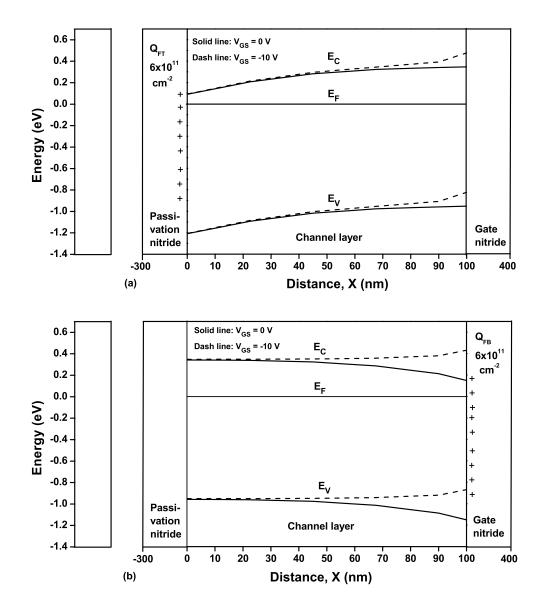

| 4.5  | Computed band bending profile in the TFT channel layer, (a) $Q_{FT} =$               |    |

|------|--------------------------------------------------------------------------------------|----|

|      | $6 \times 10^{11}  cm^{-2}$ and (b) $Q_{FB} = 6 \times 10^{11}  cm^{-2}$             | 68 |

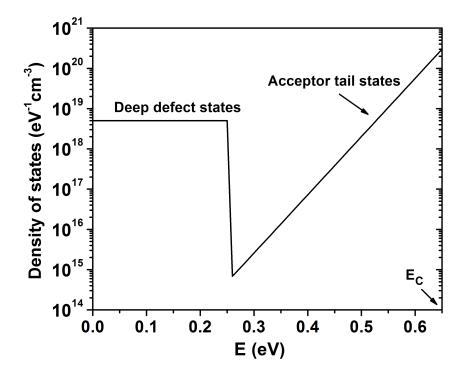

| 4.6  | Profile of density of states in the nc-Si active layer                               | 70 |

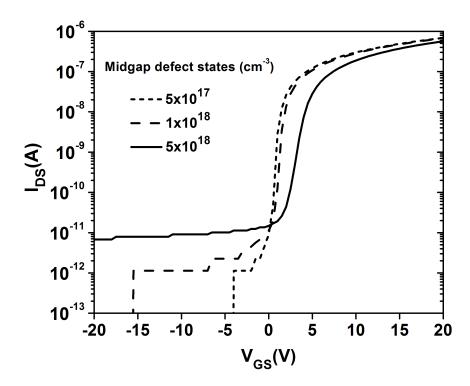

| 4.7  | Transfer characteristics of a TFT computed as a function of density                  |    |

|      | of midgap defect states $(N_T)$                                                      | 71 |

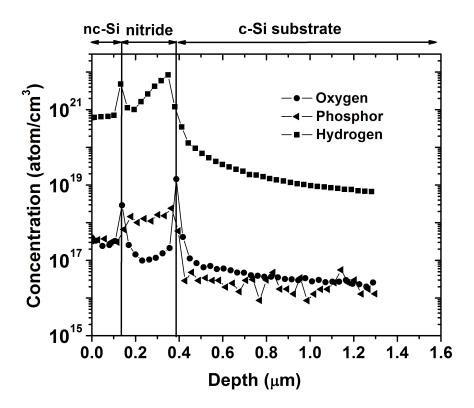

| 4.8  | Concentration of several impurities in the nc-Si active layer, obtained              |    |

|      | from Secondary Ion Mass Spectroscopy (SIMS)                                          | 73 |

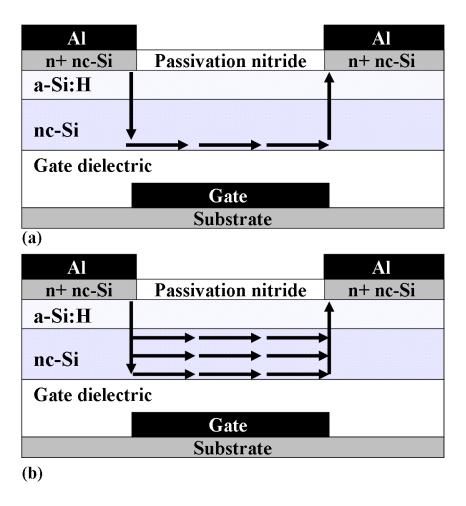

| 4.9  | Arrows represent the tentative transistor current path, (a) in the                   |    |

|      | on-state and (b) in the off-state                                                    | 74 |

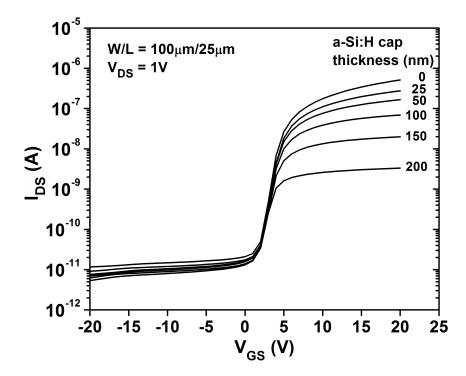

| 4.10 | Transfer characteristics computed as a function of the $\alpha\textsc{-Si:H}$ thick- |    |

|      | ness. The nc-Si layer is 65 nm thick                                                 | 75 |

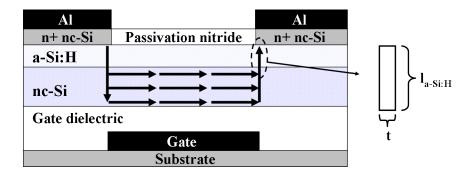

| 4.11 | Modeling the $\alpha$ -Si:H cap as a resistor when TFT is in the off-state.          | 76 |

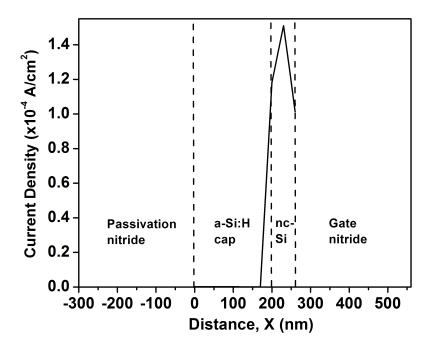

| 4.12 | Current density computed as a function of distance from the passi-                   |    |

|      | vation nitride                                                                       | 77 |

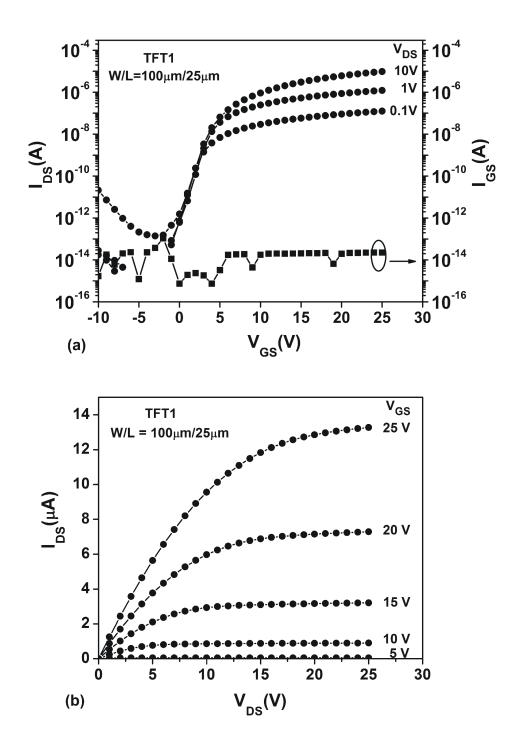

| 4.13 | (a) Transfer and (b) output characteristics of TFT1. The aspect                      |    |

|      | ratio is $100\mu m/25\mu m$ .<br>The gate dielectric [N]/[Si] is 1.3                 | 78 |

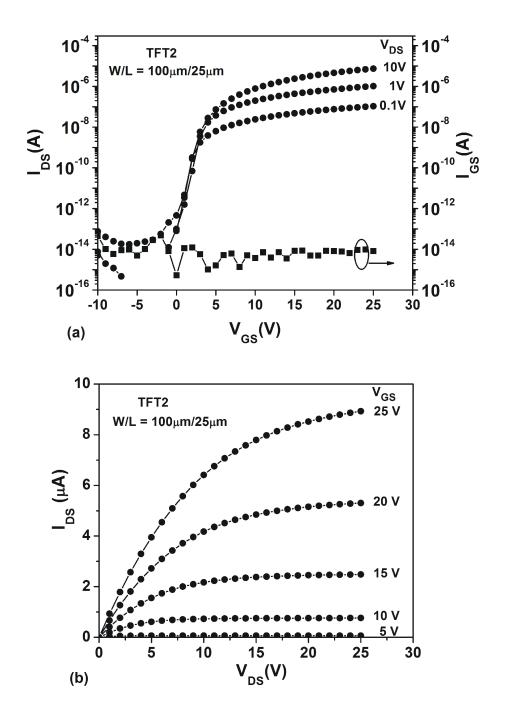

| 4.14 | (a) Transfer and (b) output characteristics of TFT2. The aspect                      |    |

|      | ratio is $100  \mu m/25  \mu m$ . The gate dielectric [N]/[Si] is 1.2                | 81 |

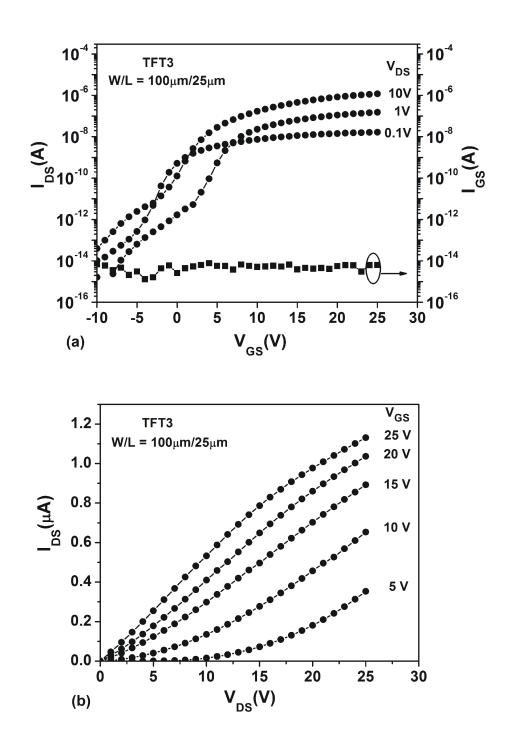

| 4.15 | (a) Transfer and (b) output characteristics of TFT3. The aspect                      |    |

|      | ratio is $100 \mu m/25 \mu m$ . The gate dielectric [N]/[Si] is 1                    | 82 |

| 5.1  | Threshold voltage shift as a function of time for different stress cur-              |    |

| 0.1  | rents and temperatures                                                               | 90 |

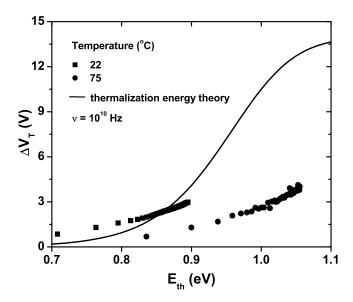

| 5.2  | Threshold voltage shift of the nc-Si TFT at different temperatures                   |    |

| 0.2  | as a function of the thermalization energy                                           | 92 |

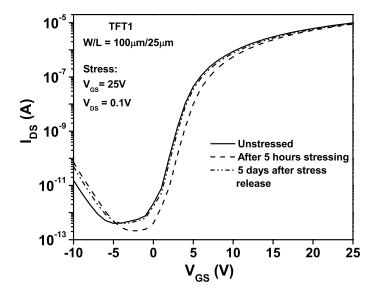

| 5.3  | Transfer characteristics of TFT1 in three different states: unstressed,              | _  |

| 5.5  | stressed for 5 hours at 25 V gate bias, and 5 days after stress release              |    |

|      | at room temperature                                                                  | 94 |

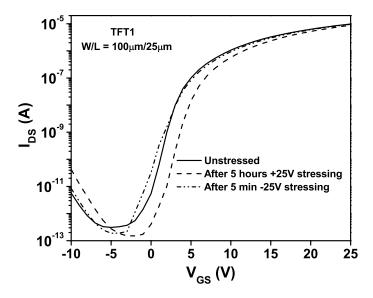

| 5.4 | Transfer characteristics of TFT1 in three different states: unstressed, |     |

|-----|-------------------------------------------------------------------------|-----|

|     | stressed for 5 hours at $+25$ V gate bias, and subsequently biased at   |     |

|     | -25 V gate voltage for 5 minutes                                        | 95  |

| 5.5 | Threshold voltage shift as a function of stress time for a gate voltage |     |

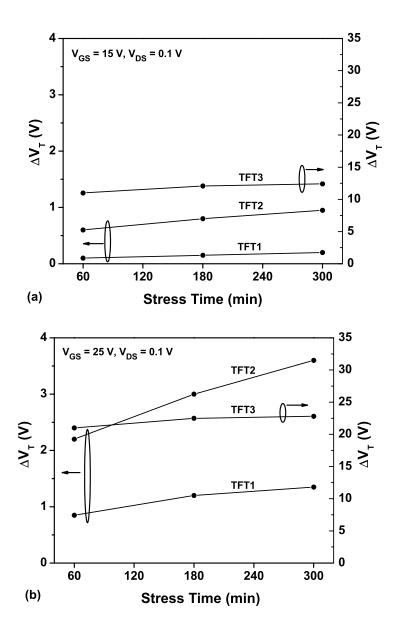

|     | of (a) 15 V, and (b) 25 V in the linear regime                          | 97  |

| 5.6 | Threshold voltage shift as a function of stress time for a gate voltage |     |

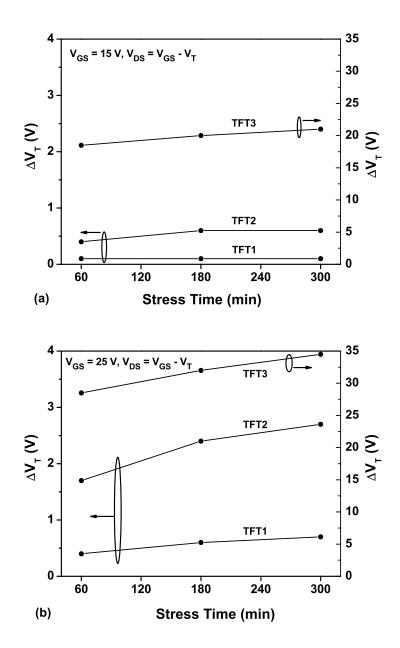

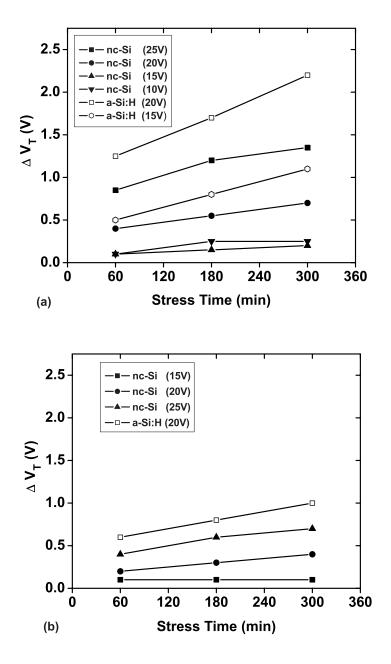

|     | of (a) 15 V, and (b) 25 V in the saturation regime                      | 98  |

| 5.7 | Threshold voltage shift as a function of stress time for several gate   |     |

|     | biases at (a) linear and (b) saturation regime                          | 101 |

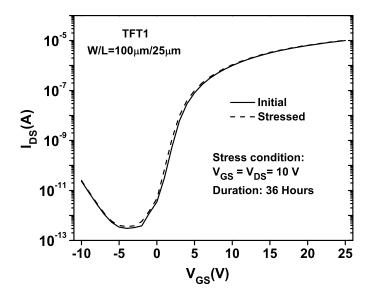

| 5.8 | Transfer characteristics of the nc-Si TFT1 before and after bias stress |     |

|     | for 36 hours $(V_{DS} = V_{GS} = 10 V)$                                 | 103 |

## Chapter 1

## Introduction

#### 1.1 Macroelectronics

Microelectronics technology based on crystalline semiconductors, mainly silicon, has revolutionized human life style by offering uncountable products in communication, computation, health, space, and entertainment sectors, to name a few. In microelectronics, the trend has been to follow the Moore's law of scaling by shrinking the length of transistors from several micrometers to several tens of nanometers, in order to increase the speed of transistors and also the number of transistors per unit area. However, there are applications in which sophisticated transistors are not required and low-speed, micrometer-size transistors are sufficient, with the goal to spread electronic components over large area substrates at low fabrication cost. These applications are known as large-area electronics as well as macroelectronics [1, 2]. For example, in a flat panel display, electronics are required to control the operation of individual pixels over areas as large as  $1 m^2$ . For comparison, the current crystalline silicon technology is limited to substrate area of around  $0.3 m^2$ . Medical x-ray imager is also another important application of macroelectronics.

Implementing macroelectronics using the conventional microelectronics, based on crystalline technologies, becomes cost-prohibitive [2]. Therefore, in response to this shortcoming, thin film technologies have been developed to deposit and process

electronic materials over non-crystalline substrates such as glass, plastics, and metal foils. Among them, several forms of thin film silicon, namely, hydrogenated amorphous silicon ( $\alpha$ -Si:H) and polycrystalline silicon (polysilicon), and their associated thin film transistors (TFTs) play a key role in macroelectronics [3].

Thin film technologies and macroelectronics have already grown to a big industry, which is currently centered around flat panel electronics and liquid-crystal displays (LCDs). For example, it has been forecasted that the worldwide market for LCDs will reach \$118 billion in 2010 [4]. On the other hand, the market for a new generation of displays, i.e. organic light emitting diode (OLED) displays, will reach about \$2.5 billion by 2012 [5].

Figures 1.1 (a) and (b) show images produced by an OLED display and an x-ray imager, respectively. On these panels, TFTs control the operation of individual pixels forming the image. Usually, the display or imager panel is designed as a matrix so that pixels are located at row and column intersections and controlled by their dedicated pixel circuit. In this case, the panel is called an *active matrix array*. The concept is the same for both display and imager cases, the only difference is the detail of pixel circuits. In what follows, the concept of an *active matrix array* is discussed in further details.

#### 1.2 Active Matrix Arrays

Figure 1.2 (a) illustrates an active matrix array. It may represent an x-ray imager, LCD, or OLED display. Here, rows are sequentially scanned and activated by row driver circuitry and picture information (video signal) is transferred to pixel circuits row by row, by column driver circuits in the case of a display. If it is an x-ray imager, the image data is read out via column drivers once a row is selected. Row driver circuitry is essentially the same in both display and imager cases.

On the other hand, pixel circuits are application specific as shown in Figs. 1.2 (b),(c), and (d) for x-ray imager, LCD, and OLED display, respectively. In Fig.

Figure 1.1: The panel outputs generated by an (a) OLED display and (b) x-ray imager. Pictures are from [6] and [7].

1.2 (b), when x-rays are incident on the detector, electrical charges are created and integrated on the storage capacitor  $(C_S)$ . After a charge integration period, the TFT, labeled as S-TFT, is turned on by the row voltage and the generated signal is passed to the readout (column driver) circuitry. The TFT is then turned off for next integration cycle [8]. Figure 1.3 shows a photomicrograph of a real x-ray active matrix array, showing several rows and columns along with detection area and TFTs [7].

In LCDs, Fig. 1.2 (c), each pixel is a capacitor, labeled as  $C_{LC}$ , since liquid crystal (LC) molecules are sandwiched between two transparent electrodes. When the row voltage goes high, the TFT is turned on and the video voltage is transferred to the pixel. The  $C_S$  helps to stabilize the voltage across the pixel. Subsequently, the liquid crystal modulates the intensity of light coming from the backlight proportional to its voltage  $(V_{OUT})$  [9]. Here, we notice that the pixel TFT (S-TFT) is simply acting as a switch, and that LCDs are driven by a voltage signal.

In contrast to LCD, which is voltage-driven, OLED is a current-driven device. Hence, the video voltage should be converted into a current signal, which is done by

Figure 1.2: (a) The concept of active matrix array, and basic pixel circuits in (b) x-ray imager, (c) liquid crystal display, and (d) organic light emitting diode display.

Figure 1.3: Photomicrograph of an x-ray active matrix array. From Ref. [7].

the current-driver transistor (D-TFT) in Fig. 1.2 (d), showing a basic pixel circuit in OLED displays. The other components, i.e.  $C_S$  and switching TFT (S-TFT), function similar to those in the LCD pixel circuit. When the row voltage goes high, S-TFT is turned on and the video voltage signal is transferred to the  $C_S$ . Subsequently, the D-TFT converts the video voltage to an output current ( $I_{OUT}$ ) for the OLED pixel. The generated light by OLED is proportional to  $I_{OUT}$  and thus to the applied video signal [9].

In this thesis, we will be only discussing TFTs that are used in pixel circuits, shown in Figs. 1.2 (b),(c), and (d). The subject of row/driver circuitry is out of the scope of this research. Pixel transistors usually operate at low frequencies and thus moderate and low performance characteristics, e.g. mobility, are sufficient, since the refresh rate of displays is slow and in the range of 60-120 frames per second. In the next section, several TFT technologies that are under research and development or already matured are introduced, in order to make it clear that what kind of transistors can be used in various pixel circuits on active matrix arrays.

## 1.3 Thin Film Materials and Transistor Technologies

#### 1.3.1 Hydrogenated Amorphous Silicon

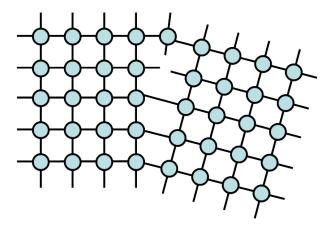

Hydrogenated amorphous silicon ( $\alpha$ -Si:H) is deposited by plasma enhanced chemical vapor deposition (PECVD), using silane ( $SiH_4$ ) or a mixture of silane and hydrogen ( $H_2$ ) source gases at temperatures of less than 300 °C. This low temperature process along with the amorphous nature of used substrates, e.g. glass, lead to formation of amorphous materials lacking structural order like that of crystalline silicon [11]. Figures 1.4 (a) and (b) show a two-dimensional representation of atomic bonding in  $\alpha$ -Si:H and crystalline silicon, respectively [10].

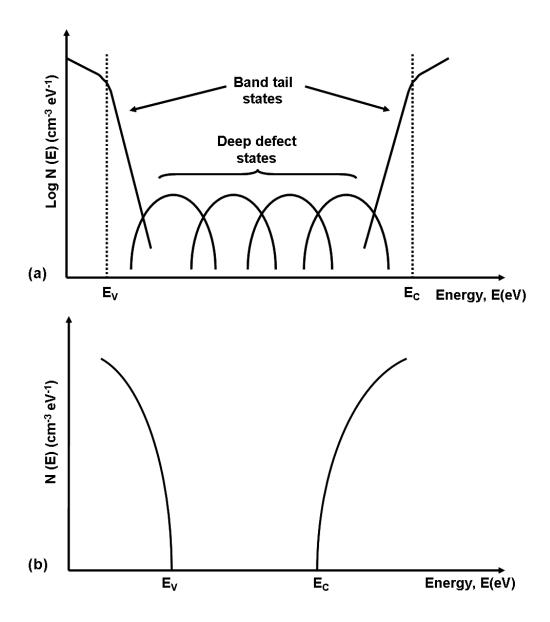

In the crystalline structure, silicon atoms occupy specified locations with a uniform bond length and angle, while in the amorphous case, there are missing atoms and slight variation in bond length and angle. This structural disorder has a strong bearing on electrical properties of the  $\alpha$ -Si:H. For example, deep defect states in the energy gap of  $\alpha$ -Si:H are associated with missing atoms, i.e. dangling bonds, and the deviation in bond length and angle results in states below the conduction band, commonly known as band tail states. Figure 1.5 (a) shows an example of distribution of states in the energy gap of the  $\alpha$ -Si:H [10, 11].

Figure 1.4: Two dimensional representation of atomic bonding in (a)  $\alpha$ -Si:H and (b) crystalline silicon (adapted from [10]).

Figure 1.5: Distribution of density of states in (a)  $\alpha$ -Si:H and (b) crystalline silicon. Adapted from [10, 12]. N(E) is in log scale in (a), and scaling is not accurate.

The density of deep defect states in  $\alpha$ -Si:H is in the range  $10^{15}-10^{18}\,cm^{-3}eV^{-1}$ , which is largely dependent on PECVD conditions. Fortunately, atomic hydrogen that is generated during PECVD passivates a portion of dangling bonds, reducing the density of defect states [10, 11].

When  $\alpha$ -Si:H is used in TFTs as the active layer, the resulting field-effect mobility ( $\mu_{FE}$ ) is in the range of  $0.1 - 1 \frac{cm^2}{V.s}$ . The low  $\mu_{FE}$  is attributed to large density of band tail states; Indeed, electrons are frequently trapped into and released from band tail states leading to the low mobility [11]. This concept will be explained in further details, in chapter two. Consequently,  $\alpha$ -Si:H TFTs are inferior to crystalline silicon (c-Si) transistors, although their low mobility is sufficient for LCDs and they are being used in commercial products [13].

Another drawback of  $\alpha$ -Si:H TFT is its instability. When it is subject to a prolonged gate voltage, the drain-source current  $(I_{DS})$  is observed to gradually decrease over time, associated with a shift in its threshold voltage  $(\Delta V_T)$ . The causes of  $\Delta V_T$  will be discussed in chapter two. The instability issue is not a major concern in LCD and x-ray imager pixel circuits, shown in Figs. 1.2 (b) and (c), due to the fact that their TFTs are not subject to prolonged gate voltages. Here, TFTs act as simple switches with a short duty cycle, i.e. they are turned on for several tens of microseconds to pass the video signal and turned off for around ten milliseconds, subsequently. On the other hand, it is very difficult to use  $\alpha$ -Si:H TFTs as analog circuit elements, as in this case they have to operate continuously, i.e. they are subject to prolonged gate biases. One particular area of interest is OLED displays. Referring to Fig. 1.2 (d), the D-TFT is an analog current driver. The D-TFT should be able to provide a stable current for OLED for generating a uniform and stable output light. Currently, the instability of  $\alpha$ -Si:H TFT is the major issue against implementation of active matrix arrays for OLED displays [14], to which we hope to contribute.

#### 1.3.2 Polycrystalline Silicon

When amorphous silicon is subject to an annealing process, it can be transformed into polycrystalline silicon (poly-Si). Crystallization can be performed either by thermal annealing in furnace at temperatures around  $600 - 700\,^{\circ}\text{C}$  or by laser annealing. Poly-Si can also be formed by a variety of other methods. For example, it can be directly deposited by thermal decomposition of  $SiH_4$  at approximately  $600\,^{\circ}\text{C}$  by a process known as low-pressure chemical vapor deposition (LPCVD), and also by metal induced crystallization process at temperatures lower than  $600 - 700\,^{\circ}\text{C}$  [10, 13].

In general, poly-Si is viewed as a network of randomly oriented crystalline grains interconnected by thin (only 1-2 atomic layers) grain boundaries, illustrated in Fig. 1.6. Here, the quality of grains can be high and virtually defect-free, while grain boundaries possess large concentration of defects, dangling bonds. The grain size is dependent on the crystallization method and varies from tens of nanometers to several micrometers [13]. From the standpoint of device mobility, larger grains are preferred as the average defect density is smaller [10]. In addition, for a given TFT length, a larger grain size results in fewer grain boundaries across the channel, leading to less trapping of carriers at grain boundaries and, hence, higher mobility. Overall, when an annealing method results in fewer intragrain defects, device mobility is higher [13].

For example, electron mobilities in the range  $10 - 50 \frac{cm^2}{V.s}$  and  $50 - 300 \frac{cm^2}{V.s}$  are easily obtained by thermal and laser annealing, respectively [13]. Developing advanced laser annealing techniques, mobilities as high as  $450 - 566 \frac{cm^2}{V.s}$  and  $200 \frac{cm^2}{V.s}$  have been achieved for electrons and holes, respectively, approaching those of c-Si transistors [15, 16].

Therefore, high mobility poly-Si TFTs can be used for integration of row and column drivers on display panel, as they provide sufficient electron and hole mobilities in n-type and p-type devices for CMOS operation. The integration of row and column drivers is not feasible by  $\alpha$ -Si:H TFTs, as carrier mobilities much greater

Figure 1.6: Representative 2D atomic bonding in poly-Si (adapted from [10]).

than that of  $\alpha$ -Si:H TFT is required [10]. In addition, poly-Si devices are much more stable than the  $\alpha$ -Si:H counterpart [14].

Unfortunately, poly-Si technology is not without issue. For example, it is more expensive than  $\alpha$ -Si:H, as it needs expensive tools such as excimer laser for annealing, ion implanter for making source/drain doped contacts, and rapid thermal annealing tool for dopant activation. These tools are specific to poly-Si technology. Poly-Si is also suffering from poor spatial uniformity, mainly because of the crystallization step and random positioning of grain boundaries along the transistor channel. For example, one poly-Si TFT may have one grain boundary across its channel, while another one may have three grain boundaries. This non-uniformity leads to mobility and threshold voltage non-uniformity over large area substrates. Currently, this technology has been applied to active matrix arrays of  $\leq 11$ " in diagonal, due to the cost and non-uniformity drawbacks [9, 13].

Table 1.1 summarizes the attributes of poly-Si and  $\alpha$ -Si:H technologies [9]. We notice that poly-Si is able to provide n-type and p-type TFTs, while in  $\alpha$ -Si:H technology, the only usable device is n-type. Here, the hole mobility is around two orders of magnitude smaller than that of electrons, which is practically useless. As mentioned earlier, poly-Si TFTs have been used in smaller panels ( $\leq$  11" in diagonal) since the overall cost is lower and row/column drivers can be integrated on the panel. However, for larger panels it is preferred to use  $\alpha$ -Si:H TFTs as the

Table 1.1: Attributes of poly-Si and  $\alpha$ -Si:H TFT technologies. From Ref. [9].

| TFT Attribute        | Poly-Si                | $\alpha	ext{-Si:H}$    |

|----------------------|------------------------|------------------------|

| Type                 | N-MOS and P-MOS        | N-MOS                  |

| Electron Mobility    | 10-500                 | 0.1-1                  |

| $(cm^2/V.s)$         |                        |                        |

| Cost (array only)    | High                   | Low                    |

| Cost                 | Low (Built-in          | High                   |

| (module)             | row/column driver)     | (External driver)      |

| Overall Cost         | Lower for small panels | Lower for large panels |

| Equipment Investment | High                   | Low                    |

| Uniformity           | Worse                  | Better                 |

| Current stability    | High                   | Low                    |

production cost is lower. In this case, we have to use external row/column drivers, which are usually crystalline silicon CMOS chips and mounted on the periphery of the active matrix array.

There have been continuous efforts to improve the performance characteristics of these two technologies. For example, advanced laser annealing methods are being developed in order to increase the carrier mobility of poly-Si TFTs as well as to improve the uniformity over larger areas [15, 16]. For the case of  $\alpha$ -Si:H, further improvement seems to be impossible. Thus, research efforts have been directed to newer technologies such as nanocrystalline silicon, also called microcrystalline silicon, in order to boost device parameters such as mobility and electrical stability [3, 17, 18].

Indeed,  $\alpha$ -Si:H technology has several appealing attributes; it does not need costly tools such as ion implanter and excimer laser, and can be processed over large areas (over  $2m \times 2m$ ) [19]. For example, currently, eight 46" LCD panels are produced on a single piece of glass by PECVD processes, so called generation (Gen) 8 [20]. Therefore, if a technology compatible with  $\alpha$ -Si:H, in terms of fabrication

and facilities, could provide higher mobility and stability, it would be easily adopted by industry. In the next section, we introduce nanocrystalline silicon technology and review its properties.

#### 1.3.3 Nanocrystalline Silicon

Nanocrystalline silicon (nc-Si) technology is fully compatible with the  $\alpha$ -Si:H and employs the same tools for device processing. The logical way for boosting device performance parameters is to change the material microstructure and move from the amorphous phase without any structural order, and towards crystalline or polycrystalline phases with some degree of structural order. To preserve compatibility with  $\alpha$ -Si:H, one approach is to only modify the plasma chemistry and PECVD processes. In this case, we avoid using laser annealing as used in poly-Si TFTs and, thus, its associated issues.

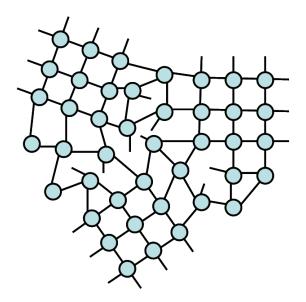

Earlier we noted that  $SiH_4$  and  $H_2$  source gases are used in PECVD for  $\alpha$ -Si:H deposition. It was found that if the  $H_2/SiH_4$  gas flow ratio becomes large (e.g.  $\geq 10$ ), the material microstructure changes and comprises of crystalline grains of less than  $50\,nm$  in diameter embedded in an amorphous matrix [21, 22]. Figure 1.7 shows a 2-D representation of atomic bonding in nc-Si. This material is known as nc-Si due to size of crystalline grains. It is interesting to note that although nc-Si contains amorphous phase, it was observed that its electrical stability was significantly improved when the volume fraction of crystalline grains exceeds  $60\,\%$  [17, 23].

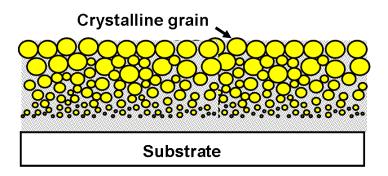

In designing nc-Si TFTs, we should consider an important feature of nc-Si regarding its structure, shown in Fig. 1.8. When nc-Si grows on an amorphous substrate such as glass, its structure is not highly crystalline in the beginning. It may be entirely amorphous or comprised of very small grains of just a few nanometers with dominant amorphous phase. When the film grows thicker, the grain size increases and the film becomes highly crystalline with very little amorphous phase [22]. This structural difference at the bottom and at the top of the film has

Figure 1.7: Two dimensional representation of atomic bonding in nc-Si (adapted from [24]).

implications for device design.

If one makes a nc-Si TFT with gate metal and gate dielectric at the bottom, as shown in Fig. 1.9 (a), the device performance is determined by the quality of bottom layers of nc-Si, where the conduction channel is formed. Alternatively, it is possible to put the gate dielectric and gate metal on the top and make the so called *top-gate* TFT, shown in Fig. 1.9 (b). In this case, the conduction channel will be formed in the highly crystalline part of the nc-Si film. Hence, it is expected that top-gate nc-Si TFTs render better performance than bottom-gate devices [3].

For top-gate devices, Cheng et al. [25] and Lee et al. [18] have reported field-effect mobility of 40 and 150  $cm^2/V.s$ , respectively. For bottom-gate TFTs, mobilities in the range  $0.5 - 3 cm^2/V.s$  have been reported [26, 27]. In the next section, we review issues and challenges of nc-Si TFTs.

Figure 1.8: Material structure of nc-Si. It is inhomogeneous and comprises of small grains near the substrate and larger grains when thickness increases (adapted from [22]).

Figure 1.9: Two nc-Si TFT structures, (a) bottom-gate and (b) top-gate. The arrow represents the conduction path.

## 1.4 Challenges for Nanocrystalline Silicon Thin Film Transistors

#### 1.4.1 Top-gate Structure

In top-gate structure, Fig. 1.9 (b), the gate dielectric can be either silicon dioxide  $(SiO_2)$  or hydrogenated amorphous silicon nitride  $(\alpha\text{-SiNx:H})$ . Thus far, high mobility TFTs have been achieved using  $SiO_2$ , not  $\alpha\text{-SiNx:H}$ . Reported mobilities are in the range of  $11 - 150 \, cm^2/V.s$  [18, 25, 28, 29, 30] and  $0.5 - 2 \, cm^2/V.s$  [17, 31, 32] for  $SiO_2$  and  $\alpha\text{-SiNx:H}$  gate dielectrics, respectively. Hence,  $SiO_2$  is the preferred dielectric for top-gate configuration, as it is for poly-Si and crystalline

silicon transistors, too.

Unfortunately, a major issue with  $SiO_2$ , which is deposited by PECVD at temperatures below 300 °C, is its poor insulating quality that leads to high gate leakage current and severe charge trapping in  $SiO_2$  and, thus, device instability [18, 33]. In other words,  $SiO_2$  forms a good interface with nc-Si that results in a high mobility, but its bulk insulating quality is poor [33]. On the other hand,  $\alpha$ -SiNx:H forms a low quality interface with nc-Si that leads to a low mobility, although it has a good bulk insulating property. For this reason,  $\alpha$ -SiNx:H is widely used in bottom-gate  $\alpha$ -Si:H TFTs and display industry and has yielded low gate leakage current and device-grade insulating quality.

Another problem is that the top-gate structure, shown in Fig. 1.9 (b), is not commonly used in industrial production lines. Usually, industry is very reluctant to change its working setup, which is currently based on bottom-gate configuration, unless they see a significant shift in performance and benefits.

#### 1.4.2 Bottom-gate Structure

The bottom-gate structure, Fig. 1.9 (a), is the current industrial standard and widely used in the manufacturing of LCDs. For this reason, bottom-gate nc-Si TFT with improved performance compared to its  $\alpha$ -Si:H counterpart, would be easily adopted by industry [27].

A major issue with this configuration is the quality of initial layers of nc-Si close to the gate dielectric interface. Often times, it is found that initial layers are fully amorphous, so called amorphous incubation layer [27]. The incubation layer thickness depends on PECVD conditions and could be as thick as several tens of nanometers. Above this layer, small crystalline grains grow and their size gradually increases when the film becomes thicker [22].

If the amorphous incubation layer of considerable thickness exists, the nc-Si TFT behaves the same as  $\alpha$ -Si:H devices, since the conduction channel is within  $10\,nm$

from the gate dielectric interface [34]. For example, the amorphous incubation layer leads to device instability, similar to that observed in  $\alpha$ -Si:H TFTs. Thus, it should be eliminated and crystallinity of initial layers should be high to achieve stable TFTs [27].

Bottom-gate nc-Si TFTs have been reported by several groups [26, 27, 32, 35]. However, there are no comprehensive information on the nc-Si active layer. Indeed, it is unclear whether the amorphous incubation layer exists in the reported TFTs, and what is the relationship between the structure of conduction channel and device performance. Although it is often claimed that nc-Si TFTs are more stable than their  $\alpha$ -Si:H counterpart, instability mechanisms are ill-understood and have not been analyzed.

A common issue in both top- and bottom-gate structures is the high drainsource leakage current, when TFT is off  $(I_{OFF})$ . This leakage current is important in macroelectronics applications, in which image or video information are stored in pixel circuits and should not be lost. For example, consider the pixel circuit of an OLED display shown in Fig. 1.2 (d). When the video voltage has been transferred to the  $C_S$ , the S-TFT is turned off until the next cycle that the video signal is rewritten. During that period, the voltage on  $C_S$  should be constant, ideally. However, S-TFT with a high  $I_{OFF}$  acts as a charge leakage path that leads to loss of signal and, thus, to a change in the output light intensity.

The required  $I_{OFF}$  depends on the application. Calculations show that it should be less than  $10\,pA$  in OLED displays [14, 36]. In x-ray imagers, it should be as low as possible and comparable to that of  $\alpha$ -Si:H TFTs ( $\leq 0.1pA$ ) [37]. Values in the range  $50\,pA - 10\,nA$  have been reported for nc-Si TFTs [25, 32, 38]. There have been attempts to reduce the  $I_{OFF}$  and to explain its origin. Thus far, the focus has been on the bulk properties of the nc-Si layer, for example its conductivity and density of states [25, 32, 38]. However, further research is required to better understand the  $I_{OFF}$  and its mechanisms in nc-Si devices.

#### 1.5 Objectives of the Research

The focus of this research has been on the bottom-gate structure and its outstanding challenges. Earlier, we mentioned that the nc-Si TFT community is looking for two goals: devices with (i) high mobility and (ii) high stability. Thus far, high mobility has only been achieved in top-gate TFTs. Mobilities in the range of tens of  $cm^2/V.s$  are easily obtainable [18, 25, 28, 29]. For bottom-gate TFTs, mobilities are more or less the same as that of  $\alpha$ -Si:H devices, and in the range  $0.1-3 cm^2/V.s$  [26, 27, 32, 35, 39]. This difference in mobility, between top- and bottom-gate devices, is due to the structure of nc-Si shown in Fig. 1.8. Therefore, research efforts have been focused on either of these two configurations, depending on goals and requirements of targeted applications.

Currently, instability of bottom-gate  $\alpha$ -Si:H TFT, as the industrial TFT, is the primary issue hindering implementation of active matrix arrays for OLED displays [14]. Although high mobility TFTs give flexibility in designing pixel circuits, calculations show that mobility is not a critical factor and values of  $\approx 1 \, cm^2/V.s$  are adequate [14, 36]. For this reason, we have chosen the bottom-gate structure and our main goal is to develop bottom-gate nc-Si TFT and investigate its instability mechanisms.

We characterize the two most important TFT components, i.e. nc-Si active layer and  $\alpha$ -SiNx:H gate dielectric. Their quality, particularly at their interface, determines the device stability. We investigate how PECVD parameters affect the crystallinity of nc-Si films, and whether the amorphous incubation layer can be eliminated.

We are also going to identify the causes responsible for high off-current. Here, we will use a simulation tool, Medici [72], along with experimental data to investigate origins of  $I_{OFF}$ , in order to minimize it as far as possible.

#### 1.6 Thesis Organization

In chapter two, we review the basics of TFTs, including their fabrication, operation, and physics. For example, we study how the device operation is influenced by the presence of trap states in the energy gap. We also review sources of instability in TFTs, and introduce widely-accepted models to describe them.

In chapter three, we show the results of our studies on the nc-Si material, and how its crystallinity is affected by PECVD conditions. The focus is on developing a film which is suitable for bottom-gate devices, i.e. crystalline grains grow immediately upon deposition without an amorphous incubation layer. We also characterize several nitride layers to be used as the gate dielectric, in order to study device stability as a function of gate dielectric quality.

In chapter four, we discuss the performance parameters of bottom-gate nc-Si TFTs fabricated in the course of this research. Particularly, our focus will be on the off-current. Its sources will be analyzed by using the Medici numerical simulator, supported by experimental results. Throughout this chapter, we will discuss design considerations and trade-offs in order to obtain a minimum off-current, while not compromising other performance parameters.

Chapter five addresses the stability of nc-Si TFTs. We will evaluate the threshold voltage stability of our devices under different operating conditions. We will also compare their stability with that of  $\alpha$ -Si:H counterpart, and will use the attributes of instability mechanisms to justify the experimental data.

Finally, chapter six summarizes results and contributions of this research, and provides suggestions for further studies on nc-Si TFTs and their applications.

## Chapter 2

## Thin Film Transistors

#### 2.1 Introduction

In this chapter, we discuss the basic concepts of thin film transistors, including their fabrication, operation, and physics, and also mechanisms that contribute to the reliability and stability of TFTs. In the beginning, two widely-used bottom-gate structures are introduced along with their fabrication sequence. We then discuss the electrical operation of TFTs and the current-voltage (I-V) relationships that are used to describe their operation in different regimes, such as linear and saturation as well as when the device is off. We also discuss various mechanisms that are regularly used to explain the device current in the off-state, i.e. drain leakage current or off-current.

Subsequently, the electrical instability of TFTs is reviewed. The instability is related to a shift in the threshold voltage under electrical operation, and is commonly attributed to two mechanisms: defect creation in the channel layer and charge trapping in the gate dielectric. We qualitatively explain how they appear under an applied gate bias along with the widely-accepted models to describe their kinetics. We also address properties and attributes of these instability mechanisms, to be able to distinguish them and to justify our experimental data, later.

#### 2.2 Fabrication of Thin Film Transistors

Figure 2.1 shows cross sections of two processes used in the fabrication of  $\alpha$ -Si:H and nc-Si TFTs. These structures in which gate metal is below the active layer and source/drain contacts are on the top are known as bottom-qate inverted-staggered [40]. The fabrication sequence for the structure in Fig. 2.1 (a) is illustrated in Fig. 2.2. First, a metal layer is deposited, by sputtering, on a substrate and patterned to define the gate area (steps 1 and 2). Then, a trilayer comprising of hydrogenated amorphous silicon nitride ( $\alpha$ -SiNx:H) as the gate dielectric,  $\alpha$ -Si:H or nc-Si as the active layer, and another  $\alpha$ -SiNx:H as the passivation dielectric are deposited in one PECVD cycle (step 3). The passivation nitride is then patterned to expose selected regions of the active layer (step 4). Subsequently,  $n^+$  doped and metal layers are deposited and patterned to make source-drain contacts (steps 5 and 6) [10, 40]. This structure is commonly known as trilayer or etch stop, due to the fact that the passivation nitride protects the active layer, on top of gate area, from being exposed to etchants and, thus, being damaged during etching processes. In this research, the trilayer structure was used in the fabrication of TFTs, as its fabrication sequence has already been developed in our group.

Alternatively, in Fig. 2.1 (b), the  $\alpha$ -SiNx:H gate dielectric and two  $\alpha$ -Si:H layers (undoped active layer and  $n^+$  doped source/drain contacts) are deposited in one PECVD cycle. Subsequently, source/drain metal contacts are deposited and patterned. These contacts are then used as a mask for etching unwanted areas of the  $n^+$  doped layer to separate source and drain terminals. In the end, another  $\alpha$ -SiNx:H is deposited and patterned to protect the top surface of the active layer exposed during the previous etching step [10, 40]. This structure, in which the back side of channel (active) layer, on top of gate area, is etched to separate source-drain regions, is known as back channel etched.

Figure 2.1: Bottom-gate inverted-staggered TFT structures, (a) trilayer and (b) back channel etched. Adapted from [10, 40].

Figure 2.2: Fabrication sequence of the structure shown in Fig. 2.1 (a).

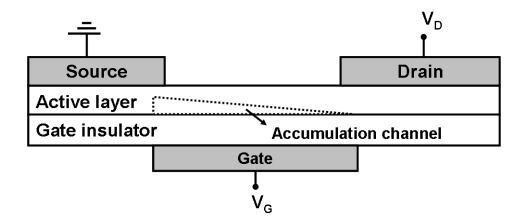

Figure 2.3: Illustration of operation of a bottom-gate TFT when gate and drain biases are applied. Adapted from [13].

# 2.3 Operation and Physics of Thin Film Transistors

In principle, TFTs are very similar to MOSFETs in terms of electrical operation and the same current-voltage (I-V) relationships can be used in describing their operation. The major difference is that we should consider defect and band tail states in the energy gap of the active layer in TFTs. Here, we review their operation, and methods that are commonly used to characterize them and to evaluate their performance characteristics such as threshold voltage, field effect mobility, and etc.

Figure 2.3 shows a cross section of a bottom-gate TFT when gate and drain biases are applied. If we assume that it is an n-type device, applying a positive gate voltage induces electrons near the semiconductor/gate dielectric interface to form the conduction (accumulation) channel shown in Fig. 2.3 [13]. Therefore, a positive gate voltage increases the conductivity between source and drain, and thus the drain current under a positive drain voltage. The magnitude of drain current in TFTs is considerably smaller than that in MOSFETs, due to the fact that mobility of electrons is much smaller in TFTs than that in MOSFETs.

In TFTs, the electron mobility is degraded by the large concentration of band

Figure 2.4: A one-dimensional model showing the motion of electrons that are frequently trapped in and released from band tail states. Adapted from Ref. [11].

tail states acting as temporary traps for conduction electrons. A profile of density of states in the energy gap of  $\alpha$ -Si:H was shown in Fig. 1.5, and a simple one-dimensional model is shown in Fig. 2.4 [11]. Here, an electron may experience frequent trapping/release events into/from various energy levels within the band gap, during its journey in the channel region. In this case, the effective field-effect mobility ( $\mu_{FE}$ ) can be expressed as

$$\mu_{FE} = \mu_0 \frac{\tau_{free}}{\tau_{free} + \tau_{trapped}},\tag{2.1}$$

where  $\mu_0$  is the band mobility of electrons without trapping, and  $\tau_{free}$  and  $\tau_{trapped}$  are the time intervals that electrons are free and trapped, respectively [11]. Indeed, electrons are trapped much of the time in band tail states and they are usually called band tail electrons.

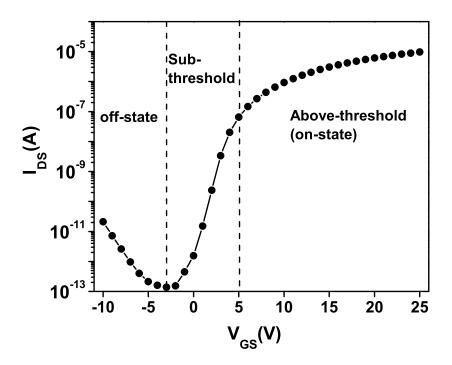

Figure 2.5 shows a typical transfer characteristic of a bottom-gate nc-Si or  $\alpha$ -Si:H TFT. One may distinguish three regions of operation. For small gate voltages around zero, the Fermi level lies in the deep defect states (see Fig. 1.5) and we may assume that energy bands are close to flat-band condition. By increasing the positive gate voltage, band bending close to the gate dielectric interface occurs, or in other words, the Fermi-level moves up through the deep defect states and towards the band tail states [40, 41]. In this case, most of the induced electrons are not free and are trapped in deep defect states; a negligible fraction of them

Figure 2.5: Typical I-V curve of a bottom-gate nc-Si or  $\alpha$ -Si:H TFT.

may occupy band tail states and thus contribute to drain current. This case is the subthreshold region shown in Fig. 2.5. This situation continues until we fill up all deep defect states with electrons, and the concentration of electrons in band tail states exceeds that of trapped electrons in deep states. It happens when the applied gate voltage exceeds a threshold voltage  $(V_T)$  and the Fermi-level now lies in band tail states [40, 41].

This argument implies that  $V_T$  is a function of density of deep defect states  $(N_T)$ . The following relationship has been derived in [10]:

$$V_T = qN_T t_S(E_F - E_i)/C_{gate}, (2.2)$$

where  $E_F - E_i$  is the energy difference between the Fermi level and the intrinsic level at threshold. The  $t_S$  and  $C_{gate}$  are the thickness of the channel layer and the gate capacitance per unit area, respectively. It should be noted that (2.2) has been derived for a simplified case: it has been assumed that  $N_T$  is uniformly distributed in the energy gap [10].

For gate-source voltages  $(V_{GS})$  higher than  $V_T$ , TFTs operate in the above-

threshold regime, i.e. on-state. To simplify their characterization, the same MOS-FET equations can be applied. In the on-state and depending on the drain-source voltage  $(V_{DS})$ , linear and saturation regimes can be defined. In the linear regime when  $V_{DS} \leq V_{GS} - V_T$ , drain-source current  $(I_{DS})$  is nearly linearly proportional to  $V_{DS}$ , and can be written as [13]:

$$I_{DS} = \mu_{FE} C_{gate} \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right],$$

(2.3)

where W and L are the TFT width and length, respectively.

When  $V_{DS} = V_{GS} - V_T$ , the accumulation channel is pinched off near the drain terminal as shown in Fig. 2.3, and drain current saturates and becomes independent of  $V_{DS}$ , ideally. For  $V_{DS} \ge V_{GS} - V_T$ , TFTs operate in saturation regime and  $I_{DS}$  is given by

$$I_{DS} = \mu_{FE} C_{gate} \frac{W}{2L} (V_{GS} - V_T)^2.$$

(2.4)

Therefore, values of  $\mu_{FE}$  and  $V_T$  can be extracted from experimental I-V curves by using (2.4). One can plot the square root of  $I_{DS}$  as a function of  $V_{GS}$  and approximate it with a line, where the line slope is proportional to  $\mu_{FE}$  and xintercept is the  $V_T$  [13].

The third operation region shown in Fig. 2.5 is the off-state when negative gate voltages are applied. In this case,  $I_{DS}$  is called off-current as well as drain leakage current. The mechanisms of current conduction in the off-state have not yet fully established, although several mechanisms have been proposed to justify the experimental results. In the following, those mechanisms are briefly reviewed.

#### 2.3.1 Mechanisms of Drain Leakage Current

The first mechanism is the ohmic conductivity of the active layer [12, 41]. When negative gate voltages are applied, the Fermi level moves downward in defect states and towards the midgap [12]. In other words, band tail electrons are depleted by a negative gate voltage and the effective conductivity of the active layer decreases.

This reduction in conductivity results in a lower drain leakage current. Thus, by applying a larger negative gate voltage, the off-current should decrease.

However, this is not always the case and off-current may increase by increasing the negative gate voltage, as shown in Fig. 2.5. In this case, the off-state conduction is usually attributed to various field-assisted and trap-assisted mechanisms that may occur in the so-called drain depletion region, located in between drain and gate overlap area. For example, the electric field increases the rate of emission of electrons that are trapped in deep defect states into the conduction band by the so-called Poole-Frenkel effect. This emission and release of trapped electrons lead to enhanced conductivity of the active layer and thus to higher drain leakage current [37]. It should be noted that the electric field is directly related to gate and drain voltages. The Poole-Frenkel conduction can be expressed as

$$I_{PF} = I_{PF0} \exp\left(\sqrt{E/E_0}\right), \qquad (2.5)$$

where E is the electric field and  $E_0$  is a coefficient [37]. Therefore, the Poole-Frenkel current increases exponentially with the electric field in the drain depletion region [37].

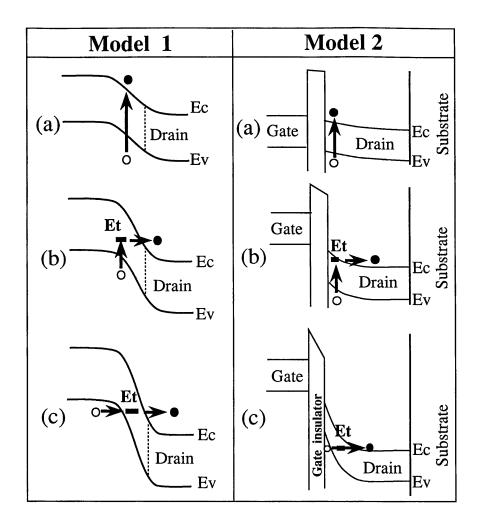

Figure 2.6 shows the band diagrams of two models, labeled as model 1 and model 2, illustrating several mechanisms of leakage current. These two models are essentially the same, their only difference is that model 1 and model 2 are referring to the band diagram in the drain depletion region along a cross section parallel and vertical to the conduction channel, respectively [42]. Thus, their difference is related to the physical location that the leakage current originates from, however, the explanation is the same for two models.

To cover a wide range of applied electric fields, three cases have been considered in Ref. [42]. When the applied electric field is low as in Fig. 2.6 (a), the leakage current is governed by thermal activation of electrons from valence band to conduction band. When the applied electric field is medium, the electron emission may comprise of two steps: first electrons are thermally excited from valence band into a trap state in the band gap, and second they tunnel into the conduction band as

Figure 2.6: The band diagrams for two models illustrating several mechanisms of leakage current, (a) the case of weak electric field, (b) the case of medium electric field, and (c) the case of strong electric field. From Ref. [42].

shown in Fig. 2.6 (b). Here,  $E_t$  is the trap energy. Finally, when the applied electric field is strong, the leakage current is governed by field-enhanced emission and tunneling. In this situation, a large electric field decreases the effective tunneling length and the presence of trap states in the band gap assists the tunneling process [42]. Thus, electrons tunnel from valence to conduction band and contribute to a high off-current. The third mechanism shown in Fig. 2.6 (c) is also known as band-to-band tunneling, and has been used to justify the experimental results of nc-Si and  $\alpha$ -Si:H TFTs [43].

## 2.4 Electrical Instability of Thin Film Transistors

In contrast to c-Si CMOS transistors,  $\alpha$ -Si:H TFTs are not stable under electrical operation. When we turn on a CMOS transistor,  $I_{DS}$  is constant for a given biasing condition. However, in  $\alpha$ -Si:H TFTs, it is observed that  $I_{DS}$  gradually decreases over time. This instability is commonly attributed to two mechanisms: (1) defect state creation in the  $\alpha$ -Si:H active layer and (2) charge trapping in the gate dielectric. These mechanisms cause a shift in the threshold voltage ( $\Delta V_T$ ), and thus  $I_{DS}$  changes according to (2.4), assuming that TFT operates in the saturation regime. In the following, we discuss these instability mechanisms and their attributes. Later, we use those attributes to distinguish the instability mechanisms.

#### 2.4.1 Metastability of Amorphous Silicon

Hydrogenated amorphous silicon ( $\alpha$ -Si:H) is deposited by PECVD at temperatures of less than 300 °C. Due to the low temperature fabrication, it contains large concentration of weak Si-Si bonds as well as dangling bonds. These two kind of bonds are considered as sources of band tail states and deep defect states, respectively. Hydrogen is also available in the material in various forms. It may form Si-H bonds and passivate Si dangling bonds. This reduces the density of defect states. Hydrogen also exists in the form of interstitial atoms and can diffuse within the material and change the electrical properties of  $\alpha$ -Si:H, which is often used to explain the experimental results [11].

When an  $\alpha$ -Si:H TFT is turned on, the concentration of conduction electrons increases in the  $\alpha$ -Si:H channel layer. Conduction carriers are also called band tail carriers as they spend much time in band tail states during frequent trapping and release events that was illustrated in Fig. 2.4. It is hypothesized that band tail carriers interact with weak Si-Si bonds which leads to an energy transfer from carriers to weak bonds. Due to this interaction, weak Si-Si bonds break and new dangling bonds are formed. Consequently, band tail carriers are trapped in the

newly-created defect states and effectively  $I_{DS}$  decreases or  $V_T$  increases, as a higher gate voltage is required to maintain the band tail carrier density and drain current unchanged [11, 44, 45].

Kinetics of carrier-induced defect state creation has been studied, and it has been found that hydrogen plays an important role in the metastability of  $\alpha$ -Si:H. In the most widely accepted model for the carrier-induced defect creation, a hydrogen atom diffuses to the weak Si-Si bond and participates in the process, where upon the breakage of the weak bond, two dangling bonds are created which one of them is passivated by the hydrogen [44, 45]. Hydrogen diffusion has been found to follow a stretched-exponential time dependence and to be dispersive, similar to the carrier transport in  $\alpha$ -Si:H shown in Fig. 2.4. This dispersive motion of hydrogen leads to the stretched-exponential time dependence of carrier-induced creation of defects and, consequently, the shift in threshold voltage [44]. Thus, assuming that defect state creation is the dominant mechanism of the shift in threshold voltage, a relationship has been developed in the form of

$$\Delta V_T = C \left[ 1 - exp \left[ -\left(\frac{t}{\tau}\right)^{\beta} \right] \right]$$

(2.6)

where  $C \approx V_{GS} - V_{T0}$ ,  $V_{GS}$  is the applied gate-source voltage, also called gate bias stress,  $V_{T0}$  is the threshold voltage at time t = 0, and  $\tau$  and  $\beta$  are a time constant and fitting exponent, respectively. The parameter  $\beta$  has been found to be around 0.5 at room temperature [44, 45].

It is well known that hydrogen diffusion in  $\alpha$ -Si:H is temperature-activated, which renders a highly temperature dependent  $\Delta V_T$ . When the device operating temperature increases, the rate of hydrogen diffusion increases, which results in an increase in  $\Delta V_T$ . The temperature dependence is reflected in the parameter  $\tau$  as

$$\tau = \tau_0 \exp\left[\frac{E_A}{k_B T}\right] \tag{2.7}$$

where  $\tau_0$  has been found to be around  $10^{-10} \sec$  and  $E_A = 0.95 \, eV$  is the activation energy [44]. For short stress times, i.e.  $t \le \tau$ , equation (2.6) can be approximated

by

$$\Delta V_T = (V_{GS} - V_{T0}) \left[ \frac{t}{\tau} \right]^{\beta}, \qquad (2.8)$$

and has been used to model the experimental threshold voltage shifts [44, 45].

It is interesting that the shift in threshold voltage is reversible, meaning that generated defects can be annealed and re-passivated by atomic hydrogen present in the material. For example, it is common to put the electrically stressed TFTs in an oven and anneal them at temperatures around  $150\,^{\circ}$ C for several hours, to obtain more or less the initial I-V characteristics. Here, hydrogen motion and diffusion inside  $\alpha$ -Si:H is again the key phenomenon during the defect annealing process [11]. Thus, the kinetics of defect removal can also be formulated by the stretched-exponential time dependence. Assume that we have subjected a TFT to a gate bias stress for some time and generated a defect density of  $N_{T0}$ . If we then remove the gate bias and the TFT is relaxed at an ambient temperature of T, the density of defects over time is given by

$$N_T(t) = N_{T0} \exp\left[-\left(\frac{t}{\tau}\right)^{\beta}\right],\tag{2.9}$$

with similar parameter values as given for (2.7) [11]. As mentioned, defect annealing is usually performed at high temperatures around 150 °C. At room temperature, it may take around a year and, for this reason, it is sometimes stated that defect states are permanently stable at room temperature [11].

#### 2.4.2 Thermalization Energy Concept

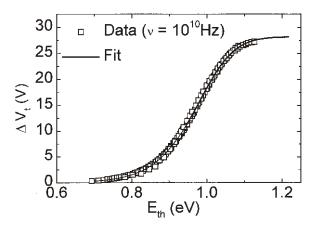

The defect state creation and thus the shift in the threshold voltage are a function of time and temperature. A common practice to compare the stability of different TFTs has been to evaluate their  $\Delta V_T$  over time at different temperatures. Thus, a smaller  $\Delta V_T$  means a more stable TFT. However, recently, a new concept has been developed by Deane et al. [46], in order to describe the instability of TFTs with a deeper physical insight. They introduced a new variable, i.e. thermalization energy, by combining time and temperature variables. The thermalization energy,

defined as  $E_{th} = k_B T Ln(\nu t)$ , means that after time t, stressing at temperature T, all defect creation sites with energy less than  $E_{th}$  would have converted into defects [46].

According to this concept,  $\Delta V_T$  is first measured as a function of time at different temperatures. They are then plotted as a function of thermalization energy. In general, when we plot the data, we obtain several curves associated with each temperature. For example, we get two curves if we perform  $\Delta V_T$  measurements at two temperatures. However, this depends on the value of the parameter  $\nu$  in the  $E_{th}$  definition. Deane et al. [46], and after them several other groups [47, 48], have found that when  $\nu = 10^{10} \, Hz$ , the two curves overlay perfectly, i.e. a single curve is obtained. In other words,  $\nu$  is a fitting parameter to move various curves along the  $E_{th}$  coordinate to overlay them and obtain a single curve. It seems that  $\nu$  is unique to defect state creation, and it has been attributed to the probability that an electron attempts to break weak Si-Si bonds [46, 49]. Therefore, the parameter  $\nu$  was considered as a merit for device stability. In other words, if  $\nu$  is smaller it means that electrons attempt to break weak Si-Si bonds less frequently and thus the rate of defect creation and  $\Delta V_T$  are smaller.

Using the kinetics of defect creation, it was shown that  $\Delta V_T$  and  $E_{th}$  have the following relationship [50]:

$$\Delta V_T = C \left[ 1 - \frac{1}{(1 + exp[(E_{th} - E_A)/k_B T_0])^{\frac{1}{\epsilon}}} \right].$$

(2.10)

Further details and definition of parameters can be found in Ref. [50]. By fitting the experimental data of  $\Delta V_T$  to (2.10), one can extract various parameters, including the energy barrier for defect state creation  $(E_A)$ . It has been found to be  $\approx 1$  eV [47, 48, 50]. A sample curve along with experimental data are shown in Fig. 2.7 [49].

In general, both charge trapping and defect creation mechanisms exist simultaneously. However, experimental results have indicated that at gate biases of less than 25 V, the defect creation is the dominant mechanism with negligible charge

Figure 2.7: Threshold voltage shift of an  $\alpha$ -Si:H TFT as a function of the thermalization energy. From Ref. [49].

trapping in a good quality nitride [45]. However, at higher gate biases, it was observed that charge trapping in the gate dielectric increases and it becomes the dominant mechanism at gate voltages greater than 50 V [45]. In the next section, we briefly review the kinetics of charge trapping.

#### 2.4.3 Charge Trapping in Silicon Nitride Dielectric