# Header Parsing Logic in Network Switches Using Fine and Coarse-Grained Dynamic Reconfiguration Strategies

$\mathbf{b}\mathbf{y}$

Alexander Sonek

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2014

© Alexander Sonek 2014

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Current ASIC only designs which interface with a general purpose processor are fairly restricted as far as their ability to be upgraded after fabrication. The primary intent of the research documented in this thesis is to determine if the inclusion of FPGAs in existing ASIC designs can be considered as an option for alleviating this constraint by analyzing the performance of such a framework as a replacement for the parsing logic in a typical network switch.

This thesis also covers an ancilliary goal of the research which is to compare the various methods used to reconfigure modern FPGAs, including the use of self initiated dynamic partial reconfiguration, in regards to the degree in which they interrupt the operation of the device in which an FPGA is embedded. This portion of the research is also conducted in the context of a network switch and focuses on the ability of the network switch to reconfigure itself dynamically when presented with a new type of network traffic.

### Acknowledgements

I would like to thank, first and foremost Dr. Agnew for providing me with the guidance to see this project through. I would also like to recognize Subbarao Arumilli whose continued assistance in providing both information and hardware resources was also instrumental in its completion. Finally, I do not want to forget Joshua Tan and Peter Gabrovsky who filled in all the remaining gaps in my work with their FPGA expertise.

### Dedication

I would like to dedicate this to all my friends and family who never waivered in their patience or support throughout this whole process.

# **Table of Contents**

| Li | st of | Tables                         | х  |

|----|-------|--------------------------------|----|

| Li | st of | Figures                        | ii |

| Li | st of | Algorithms x                   | iv |

| 1  | Intr  | oduction                       | 1  |

|    | 1.1   | Problem Statement              | 2  |

|    | 1.2   | Thesis Outline                 | 2  |

| 2  | Bac   | ground                         | 4  |

|    | 2.1   | FPGA                           | 4  |

|    |       | 2.1.1 Configuration Memory     | 5  |

|    |       | 2.1.2 Logic Elements           | 6  |

|    |       | 2.1.3 Example                  | 7  |

|    | 2.2   | Network Switch                 | 8  |

| 3  | The   | ory of Operation: Fine Grained | 10 |

|    | 3.1   | BUS and Clock Conversions      | 10 |

|    |       | 3.1.1 BUS Transformations      | 11 |

|    |       | 3.1.2 Signal Transformations   | 13 |

|    | 3.2   | MainBus Interface              | 13 |

|   |      | 3.2.1 MainBus Write to Parser Chain         | 4 |

|---|------|---------------------------------------------|---|

|   |      | 3.2.2 MainBus to DDR2 Ram                   | 4 |

|   |      | 3.2.3 MainBus System Access                 | 5 |

|   | 3.3  | Memory Interface                            | 7 |

|   |      | 3.3.1 DDR2 Controller                       | 7 |

|   |      | 3.3.2 On-Chip BRAM                          | 8 |

|   | 3.4  | Dynamic Parser Configuration Arbitration    | 9 |

|   |      | 3.4.1 ICAP Controller                       | 9 |

|   |      | 3.4.2 Parser Black-Box Wrappers             | 1 |

|   | 3.5  | Parser Chain                                | 2 |

|   |      | 3.5.1 Parser Chain Status                   | 4 |

| 4 | The  | eory of Operation: Coarse Grained 20        | 6 |

|   | 4.1  | Parser Processor                            | 6 |

|   |      | 4.1.1 Parser Core                           | 7 |

|   |      | 4.1.2 Small Parser Core Operation           | 0 |

|   |      | 4.1.3 Large Parser Core Operation           | 1 |

|   | 4.2  | Parser Interconnect Network                 | 3 |

|   | 4.3  | Coarse Parser Programmer                    | 3 |

| 5 | Frai | mework 3                                    | 5 |

|   | 5.1  | Development Board                           | 5 |

|   |      | 5.1.1 USB Driver GUI                        | 5 |

|   | 5.2  | General Project Structure and Coding Scheme | 6 |

|   | 5.3  | Bitstream Generation Flow                   | 6 |

|   | 5.4  | Optimization                                | 7 |

|   | 5.5  | Testing                                     | 9 |

|   |      | 5.5.1 Simulation Setup                      | 0 |

|   |      | 5.5.2 Hardware Probing 4                    | 0 |

|   |      |                                             |   |

| 6 | Spe | Specification Analysis Results                       |    |  |  |  |  |  |  |  |

|---|-----|------------------------------------------------------|----|--|--|--|--|--|--|--|

|   | 6.1 | Speed of Configuration                               | 42 |  |  |  |  |  |  |  |

|   |     | 6.1.1 Coarse Grained                                 | 44 |  |  |  |  |  |  |  |

|   |     | 6.1.2 Fine Grained                                   | 48 |  |  |  |  |  |  |  |

|   | 6.2 | Size of Implementation                               | 49 |  |  |  |  |  |  |  |

|   |     | 6.2.1 Static                                         | 50 |  |  |  |  |  |  |  |

|   |     | 6.2.2 Coarse Grained                                 | 51 |  |  |  |  |  |  |  |

|   |     | 6.2.3 Fine Grained                                   | 53 |  |  |  |  |  |  |  |

|   | 6.3 | Worst-Case Data Path Latency                         | 54 |  |  |  |  |  |  |  |

|   |     | 6.3.1 Static                                         | 55 |  |  |  |  |  |  |  |

|   |     | 6.3.2 Coarse Grained                                 | 56 |  |  |  |  |  |  |  |

|   |     | 6.3.3 Fine Grained                                   | 58 |  |  |  |  |  |  |  |

|   | 6.4 | Packet Loss Based on Configuration Speed             | 59 |  |  |  |  |  |  |  |

| 7 | Rel | ated Work                                            | 64 |  |  |  |  |  |  |  |

|   | 7.1 | Dynamic Reconfiguration of Network Components        | 64 |  |  |  |  |  |  |  |

|   | 7.2 | Dynamic Reconfiguration Using Custom ICAP Controller | 65 |  |  |  |  |  |  |  |

|   | 7.3 | Improvements in the Dynamic Reconfiguration Process  | 66 |  |  |  |  |  |  |  |

|   | 7.4 | Other Forms of Reconfiguration                       | 67 |  |  |  |  |  |  |  |

|   | 7.5 | Coarse Architectures                                 | 68 |  |  |  |  |  |  |  |

|   | 7.6 | Network Processors                                   | 69 |  |  |  |  |  |  |  |

| 8 | Cor | nclusion                                             | 71 |  |  |  |  |  |  |  |

|   | 8.1 | Discussion                                           | 71 |  |  |  |  |  |  |  |

|   | 8.2 | Future Work and Suggested Improvements               | 72 |  |  |  |  |  |  |  |

|   |     | 8.2.1 Coarse Grained                                 | 72 |  |  |  |  |  |  |  |

|   |     | 8.2.2 Fine Grained                                   | 74 |  |  |  |  |  |  |  |

| A | PPE | NDICES                                               | 75 |  |  |  |  |  |  |  |

# viii

| Α  | Additional Results 76 |         |                             |    |  |  |  |  |  |

|----|-----------------------|---------|-----------------------------|----|--|--|--|--|--|

|    | A.1                   | Worst   | Case Delays By Architecture | 76 |  |  |  |  |  |

|    |                       | A.1.1   | Static                      | 76 |  |  |  |  |  |

|    |                       | A.1.2   | Coarse Grained              | 77 |  |  |  |  |  |

|    |                       | A.1.3   | Fine Grained                | 79 |  |  |  |  |  |

| в  | Add                   | litiona | l Framework Details         | 81 |  |  |  |  |  |

| Gl | ossaı                 | y       |                             | 82 |  |  |  |  |  |

| Re | ferei                 | nces    |                             | 87 |  |  |  |  |  |

# List of Tables

| 3.1  | Packet Parser BUS Control Flags                                | 14 |

|------|----------------------------------------------------------------|----|

| 3.2  | MainBus DDR2 Special Read Addresses                            | 15 |

| 3.3  | Read Control Functions                                         | 16 |

| 3.4  | MainBus Interfacing Logic Status Codes                         | 17 |

| 4.1  | Small Parser Core Parameters                                   | 31 |

| 4.2  | Large Parser Core Parameters                                   | 32 |

| 4.3  | Single CLU Operation Truth Table                               | 33 |

| 6.2  | Coarse Grained Partial Reconfiguration Environment (Simulated) | 44 |

| 6.3  | Coarse Switch Bit Input Requirements                           | 44 |

| 6.6  | Fine Grained Partial Reconfiguration Environment (Simulated)   | 48 |

| 6.10 | Protocol Header Sizes by Level                                 | 61 |

| A.1  | Static TRILL Parser Delays: Balanced                           | 76 |

| A.2  | Static TRILL Parser Delays: Synth Optimized                    | 76 |

| A.3  | Static TRILL Parser Delays: Logic Optimized                    | 77 |

| A.4  | Static TRILL Parser Delays: Both Optimized                     | 77 |

| A.5  | Static Lvl2 Parser Delays: Logic Optimized                     | 77 |

| A.6  | Static Lvl2 Parser Delays: Both Optimized                      | 77 |

| A.7  | Worst Delays Through Basic Parser: Balanced                    | 77 |

| A.8  | Worst Delays Through Basic Parser: Logic Optimized             | 78 |

| A.9  | Worst Delays | Through Basic Parser: Synth Optimized     | 78 |

|------|--------------|-------------------------------------------|----|

| A.10 | Worst Delays | Through Basic Parser: Both Optimized      | 78 |

| A.11 | Worst Delays | Through Advanced Parser: Balanced         | 78 |

| A.12 | Worst Delays | Through Advanced Parser: Logic Optimized  | 78 |

| A.13 | Worst Delays | Through Advanced Parser: Synth Optimized  | 79 |

| A.14 | Worst Delays | Through Advanced Parser: Both Optimized   | 79 |

| A.15 | Fine Grained | TRILL Parser Delays: Balanced    7        | 79 |

| A.16 | Fine Grained | TRILL Parser Delays: Synth Optimized    7 | 79 |

| A.17 | Fine Grained | TRILL Parser Delays: Logic Optimized    7 | 79 |

| A.18 | Fine Grained | TRILL Parser Delays: Both Optimized    6  | 30 |

| A.19 | Fine Grained | Lvl2 Parser Delays: Logic Optimized       | 30 |

| A.20 | Fine Grained | Lvl2 Parser Delays: Both Optimized        | 30 |

| B.1  | Low Delay Sy | nthesis Profile                           | 31 |

# List of Figures

| 2.1 | FPGA Example Circuit                                                                       | 7  |

|-----|--------------------------------------------------------------------------------------------|----|

| 3.1 | Larger to Smaller BUS Conversion                                                           | 12 |

| 3.2 | MainBus Write Control Word                                                                 | 14 |

| 3.3 | MainBus DDR2 Read/Write Control Word                                                       | 14 |

| 3.4 | MainBus Read Control Word                                                                  | 15 |

| 3.5 | ICAP Write FSM                                                                             | 20 |

| 3.6 | Basic Parser Chain Layout                                                                  | 23 |

| 3.7 | MMU State Machine                                                                          | 24 |

| 4.1 | Parser Comparator Logic Unit                                                               | 29 |

| 4.2 | Small Parser Core Memory Map                                                               | 30 |

| 4.3 | Large Parser Core Memory Map                                                               | 32 |

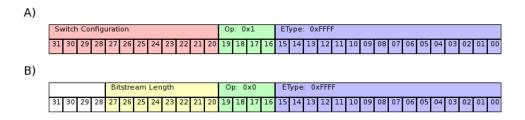

| 4.4 | Utility Config Packet: A) Interconnect Network Configuration, B) Parser bitstream starting | 34 |

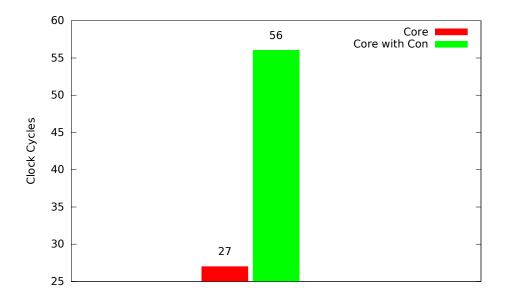

| 6.1 | Simulated Coarse Grained Programming Speeds                                                | 47 |

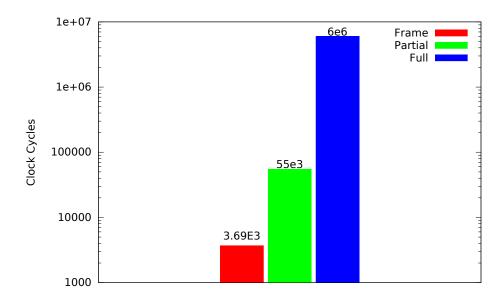

| 6.2 | Simulated Fine Grained Programming Speeds                                                  | 49 |

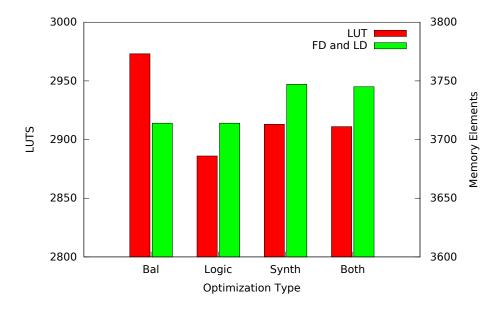

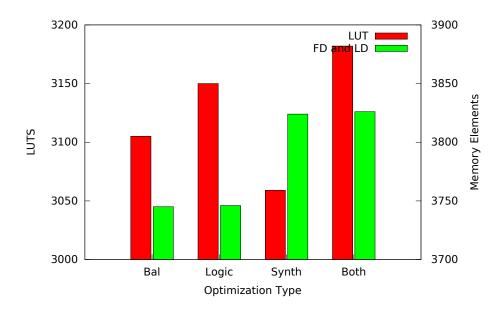

| 6.3 | Static Trill Parser Resource Usage                                                         | 51 |

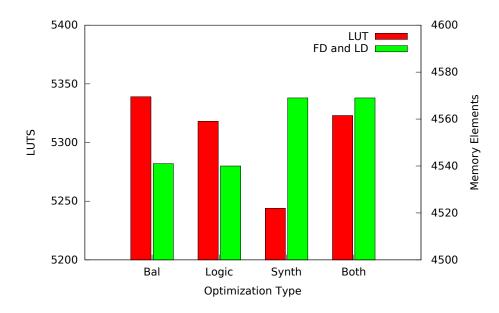

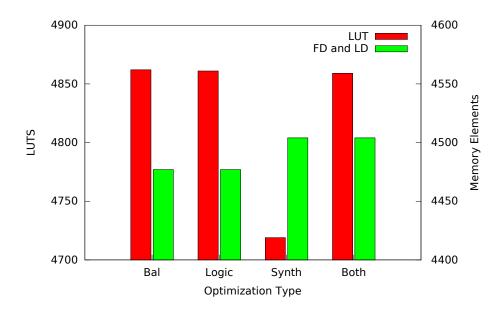

| 6.4 | Advanced Coarse Parser Resource Usage                                                      | 51 |

| 6.5 | Base Coarse Parser Resource Usage                                                          | 53 |

| 6.6 | Fine Grained Trill Parser Resource Usage                                                   | 54 |

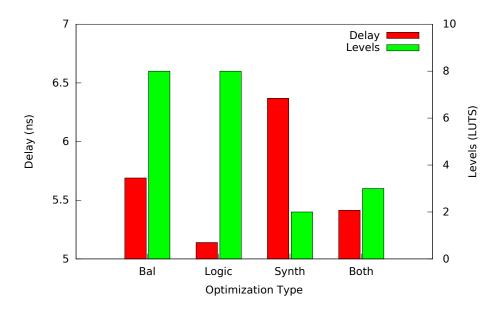

| 6.7  | Static Trill Parser Delay Statistics             | 56 |

|------|--------------------------------------------------|----|

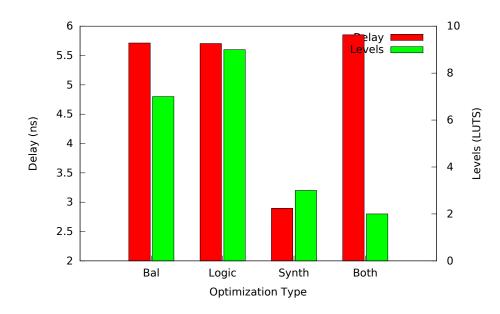

| 6.8  | Coarse Adv Parser Delay Statistics               | 56 |

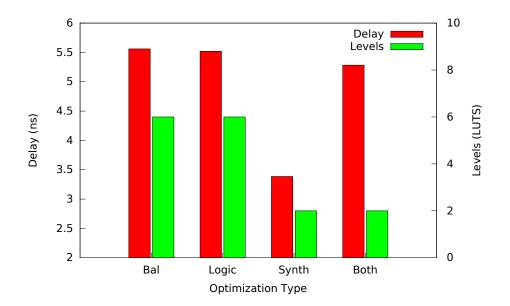

| 6.9  | Coarse Base Parser Delay Statistics              | 57 |

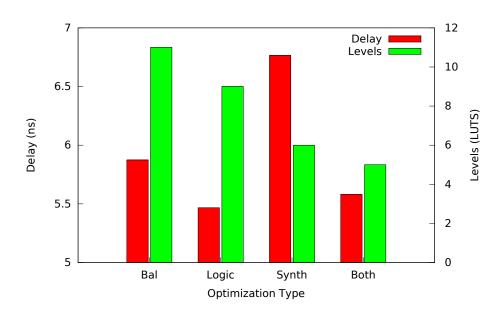

| 6.10 | Fine Grained Trill Parser Delay Statistics       | 58 |

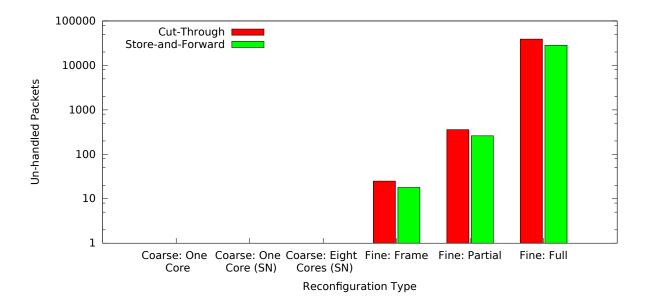

| 6.11 | Expected Un-handled Packets During Configuration | 62 |

| 8.1  | Multiple Context Coarse Parser Processor         | 73 |

# List of Algorithms

| 4.1.1 Partial Parsing State Pseudo code |  |  |  |  |  |  |  |  |  |  | 28 |

|-----------------------------------------|--|--|--|--|--|--|--|--|--|--|----|

| 5.4.1 Logic Optimization Example        |  |  |  |  |  |  |  |  |  |  | 39 |

# Chapter 1

# Introduction

As is the case with designing any other hardware with an interface to a general purpose processor using a strictly ASIC cell-based approach, when developing the hardware for a typical network switch one must keep in mind that the venues for including future upgradability are somewhat limited. The logic implemented in hardware cannot of course be modified after fabrication and any functionality which is implemented in software then suffers the speed penalty of being restricted to sequential instruction interpretation. Along these lines, if an upgrade or lateral change is required for any component critical to the core functionality of the device, such as a parser in a network switch, then the only recourse is to re-fabricate the whole device. Being that device fabrication requires quite a substantial investment of time and money, the question then becomes if there is a feasible way to allow for the future modification of a design's core components without having to expend such a significant amount of resources or sacrificing its ability to meet any speed specifications. The use of Field Programmable Gate Arrays (FPGAs) which offer the parallelization benefits of ASICs combined with the programmability of software and which can run perform operations at a rate somewhere between the two can be argued as one such solution to this problem.

The research outlined has been performed with the intent of gaining a better understanding of some the considerations that must be made in using FPGAs in this capacity. The actual reconfiguration process of FPGAs was investigated at two different levels, fine and coarse-grained, in regards to how well the resulting designs performed under various hardware engineering constraints. The actual logic tested was the parsing logic from a network switch which provided a good test-case for determining the extent to which the configuration process could be automated.

# 1.1 Problem Statement

The intent of the research presented in this thesis is to gauge the feasibility of implementing the parsing functionality found in the port logic of network switches with the ability to dynamically adjust to new types of traffic flow. The structure of the switching fabric within these devices can be seen as being relatively sheltered from changes in the higher level protocol changes because it is only responsible for handling packets once they have been classified and partitioned into internal cells. This stability in design allows for a greater focus on ensuring performance without as much concern for flexibility and as such the switching fabric is generally implemented as an ASIC. The control plane portion of the router is responsible for performing functions such as managing and configuring the overall system. Owing to the infrequent and, in many instances, not easily pre-defined nature of these tasks, a large portion of control plane is often implemented in software. While the required operation from this management aspect of the router hardware may be more susceptible to changes in how network traffic should be handled at higher levels of protocol encapsulation (changes in how routing tables are managed for example), a change in its functionality can usually be easily applied by modifying its instruction flow. In terms of weighing these trade-offs in flexibility and performance, the parsing logic, which must operate at speeds best suited for ASIC implementation but with the same instability in specifications reserved for software implementations, poses somewhat of a problem to the designer.

## **1.2** Thesis Outline

Chapter two attempts to bring the reader up to speed regarding the major concepts surrounding the research performed in this paper. It specifically covers topics on the operation of FPGAs and network switches relevant to the understanding of how the latter could be augmented with the former. The chapter wraps up with an example of how a simple Boolean statement would be implemented in a hardware look-up table which is pertinent to both grasping the underlying idea of FPGA operation and to one of the optimization techniques examined in the analysis section.

Chapters three and four collectively introduce the major components of the two reconfigurable parser architectures proposed in this research. Chapter two covers the components specific to the fine-grained re-configurable parser chain along with the supporting logic which is common to both. Chapter three finishes up by only detailing the theory of operation of the components related to the coarse-grained reconfigurable parser logic. Reading the material provided in these chapters mainly allows for a basic understanding of how it is intended that each of the dynamic parser chains fulfill its roles as a replacement for its ASIC counterpart. In going over this information it should also become clear what type of supporting logic is recommended for both debugging and programming the core logic.

Chapter five steps through the specifics of the development environment used to develop and test the proposed designs in both software simulations and when already transferred to the FPGA fabric. This chapter can be used as a basic set of guidelines for how to set up future experiments in the same field of inquest. It specifically goes through properly structuring the source code for dynamically reconfigurable designs, running the vendor provided synthesis software properly to achieve bitstreams which the FPGA hardware supports as reconfigurable, the types of optimizations which were found to achieve positive results with reconfigurable designs and an assortment of testing strategies which proved useful for these types of designs. The details of the development board used in the project are also covered in this area of the thesis but only in brief where needed to illustrate the methodology.

Chapter six discusses the methods used to analyze both the designs in the context of some common hardware engineering constraints; the results of these analyses are then discussed in terms of which of the design may be more suitable in an actual implementation. The chapter is organized by the specifications examined: speed of configuration, physical resource usage, worst-case path delay. The analysis in each case also goes over the effects of applying a number of basic optimization techniques and how they compare to those from the un-optimized tests. It concludes with a section detailing the impact of the speed of configuration constraint on the operation of an abstract network switch model created specifically for the research.

Chapter seven provides a literature review of work performed by other researches in areas which overlap with this project. Wherever relevant, the methodologies described in these works are compared to the methodologies used to separately create the two types of reconfigurable parser chains. The chapter is organized by the areas of research covered: dynamic reconfiguration of specifically network components, reconfiguration of various other circuits using the ICAP port built into the FPGA fabric, attempts at improving the efficiency of the reconfiguration process using partition based designs, other forms of partial reconfiguration (e.g. differential partial reconfiguration), dynamic reconfiguration of designs built using coarse elements and finally the use of network specific processors.

# Chapter 2

# Background

## 2.1 FPGA

While envisioned much earlier the first commercially viable Field Programmable Gate Array (FPGA) was released in 1985 with the founding of Xilinx. Not surprisingly in the relatively long time it has been around, nearly 30 years now, this technology has seen many improvements introduced to its original design in both the form of upgraded capacity and speed as well additional features such as embedded blocks of memory. Throughout its many iterations, however, the design of the FPGA has changed very little in regards to its core theory of operation which is to allow for an overall reconfigurable design using an array of configurable logic blocks interconnected by a network of switchable junctions.

FPGAs can be categorized into two major categories based on whether or not they can be reconfigured after their initial configuration which in turns relies on how their configuration is actually stored. In those that can be reconfigured the configuration state is generally stored in SRAM while in the ones that can only be configured once this data may be stored in read only flash or across a series of anti-fuses [1].

In both cases the purpose of the configuration is to not only modify the function performed at various logic sites within the design but to also to dictate how these logic sites interconnect to create the overall function output of the design. The mechanism by which the programming of the devices within each of these categories with the configuration state induces a change in their logic elements is fundamentally different, however. When it comes to SRAM based devices, the underlying core logic element which is modified during configuration is the memory of a LUT (Look Up Table), whereas with the devices that only support a single configuration this element is the switch inputs of a MUX (Multiplexer). The intent of the rest of this section is to promote a better understanding of the implications of including a reconfigurable FPGA within an existing ASIC design in the context of the one used within this research. It first covers the basic operation of the major components within such an FPGA and then attempts to demonstrate how they function as a whole to output a logic function in an example where a simple gate described function is translated to its rudimentary FPGA equivalent.

### 2.1.1 Configuration Memory

In the original series of FPGAs the configuration memory was loaded into the device serially via a slightly modified dynamic phase shift register [2] which had enough stages to span all the configurable points of all the logic elements and interconnections present. The configuration data would be shifted in until the initial bit had reached the final stage of the shift register at which point additional hold logic connected at each stage would be set to feedback the stage's output back into its input. With the hold logic enabled, each stage would thus retain its value and as such the logic elements and interconnection points connected to these stages would be considered programmed.

The concept of streaming the bitstream in sequentially would be expounded on in later models in that the bitstream would be shifted in through series of registers, one for every row of logic elements. Once the bitstream was completely loaded into these memories it would then be shifted in parallel from each storage location horizontally to the configuration memories of the logic elements [3, 4].

To support partial reconfiguration of the devices as well as other features such as CRC checking of the incoming bitstream, however, the idea of strictly shifting in the bitstream was abandoned in favour of one that also includes a routing mechanism. Essentially, in the newest devices such as the one used in this research, bitstreams and other types of data are sent in broken up into chunks and appended to multiple packets containing command and addressing information. The command information contained in these header packets could, for example, let the device know that a stream of data is being sent in to configure a portion of the device and the address data then would be used to send the chunks of the stream to an entry point into a certain portion of the configuration memory. Finally, once the chunks reach this entry point they are then shifted in to make up the actual configuration memory [5].

#### 2.1.2 Logic Elements

If the FPGA as a whole is looked at in its most basic terms as a means to output the results from one or more logical functions, the logic elements can be seen as the individual stages of the functions as chained together by the interconnects. Physically, they are placed on the device in a two dimensional array and are generally partitioned into small groups to form larger logic blocks.

While certain aspects of the circuitry in the logic elements themselves may be tweaked to allow for specializations in performing a certain subset of operations, it will always contain a set amount of LUTs and, in later devices, memory elements per device family. The individuals LUTS can be programmed to perform a number of different logical functions with an input count ranging up to the physical pin count of the component and can be combined together via one or more levels of MUXes to output functions of even greater complexity. The outputs of the function or functions performed can then be multiplexed directly to the output of the logic element to form combinatorial logic, to the memory elements to form sequential logic or to, in certain cases, components dedicated to speeding up arithmetic operations.

#### 2.1.3 Example

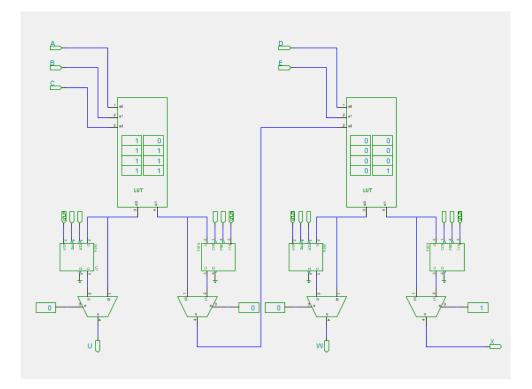

Figure 2.1: FPGA Example Circuit

The intent of this section is to demonstrate how all the pieces of an FPGA work together to produce the output of a logical function. The architecture used in the example as shown in Figure 2.1 is very basic, with LBs (Logic Blocks) composed of a single LUT and two memory elements. The interconnect network is not displayed, however, in the actual implementation it would be responsible for routing in signals to all the inputs and outputs of the two LBs.

The LUT itself is similar in structure to the ones used in the architecture of the FPGA device used in this research. It has three inputs, two outputs and, internally, is comprised of two two input, one output LUTs. The first two inputs to the component are connected in the same order to both sets of inputs of its internal LUTs while the third is connected to a MUX. The MUX allows the component to either output two separate two input functions from each of its outputs or one three input function from just its first output.

The actual function output in this demonstration is shown in Equation 2.1.1 where A, B, C, D and E are direct inputs to the two LBs of Figure 2.1 and F (Equation 2.1.2) is the logical output of the LB on the left as switched into the input of the LB on the right. The bars within each LUT represent the internal memories of the two constituent LUTs and how they are filled up with the truth tables required to perform each portion of the example function.

$$X = D \cdot E \cdot F \tag{2.1.1}$$

$$F = A + B + C \tag{2.1.2}$$

### 2.2 Network Switch

A network switch can be loosely described as a device which is used to transparently join together multiple network segments or groups of networked systems [6].

Traffic passing into the most basic example of a network switch is routed to its proper destination using the protocol described in the data link layer of the OSI communication model, meaning that a path is created between the sender and receiver based on their hardware addresses as sent with the data itself. In this sense the switch can associate one or more end-point hardware addresses with each of its ports and then use this mapping to determine which of these ports an incoming frame of data should be sent to. Generally, address learning, an operation defined as part of the transparent bridging method, is used to create this association whereby the port an address should be bound to is learned by extracting the source address of an inbound frame of data and then stored in a one to one mapping.

More complex switches support routing based on protocols described in higher layers of the OSI model and as such have to extract additional information from the data frame other than from the outermost header. In switch architectures like the one from which this research is derived from, the parsing of multiple levels of encapsulated data is supported by a chain of pipe-lined packet parsers each responsible for pulling out routing information from a single level. As a copy of the frame passes through the chain, each packet parser determines if it is able to interpret the data passing through it by checking for certain values within a set offset from where it started receiving the stream. If these values are found then additional fields within this offset are stored and then remaining data outside this portion is passed to the next parser to allow it to work on the next level in the same way. Essentially this parsing mechanism is the same as the one exploited in pipe-lined network processors [7] except hard coded in ASIC hardware.

Switches can also be broadly classified as belonging to one of two categories based on the point at which they attempt to start forwarding a packet after receiving it. Switches in the first group, or store-and-forward switches, generally will first buffer in an incoming packet in its entirety and run it through a CRC check before starting the forwarding process. Cut-through switches, on the other hand, will hold off on the forwarding only long enough to receive the pertinent portions of the encapsulated headers before they start doing the same. Switches in the latter group may still perform an error check on the packet once all of its contents arrive, but strictly for record keeping purposes as by this time it would be too late to drop it if a malformation were to be found. This additional level of distinction in switch functionality is integral in modelling the expected delay through the device [8], an abstraction of which is used to quantify the impact of applying the ideas proposed in this research.

# Chapter 3

# **Theory of Operation: Fine Grained**

In the most general terms the designs created for the fine grained test-case can be described as consisting of two consecutive levels of parsing logic extracted from a network switch and inserted into a framework which provides the functionality to simulate sending a packet through the parser chain, initiate a reconfiguration of the second parser stage upon the arrival of a specific packet type and finally monitor the parser stages by taking snapshots of their status outputs. This section provides an overview of the key operational units of the fine grained design.

# **3.1 BUS and Clock Conversions**

The design as it stands spans across four different clock domains as required by the logic for the MainBus, the parser chain, the interface to the DDR2 RAM, the PLL synchronization clock for the DDR2 controller and the internal FPGA reconfiguration port. The clock frequencies required by these logic areas are the 48 MHz,200 MHz,100MHz,200MHz and 100 MHz respectively. The logic in the design has to at one point interface with one or more of the following buses: the 32-bit MainBus, the 64-bit parser chain, the 256-bit DDR2 RAM controller input and the 32-bit internal FPGA reconfiguration port input. As such various strategies were employed within the design to ensure that when data is transferred between these various domains that it is kept at the correct level for the appropriate interval and/or aggregated or segmented to achieve the correct width.

#### 3.1.1 BUS Transformations

Dual-clock FIFOs are used as the basis for all the multi-bit or BUS transformation schemes used in the design.

In situations where a transfer of data is required between two buses which are of the same width but originate from different clock domains, such as when packet data is transferred from the slower MainBus to the faster packet parser chain bus, the mediating logic is based solely on a subset of status outputs from the interceding FIFO. As long as the FULL output pin of the FIFO stays low, the sending component in one clock domain is presented with an endpoint which is ready to receive and, as long as the EMPTY output is low, the receiving component in another is likewise presented with an endpoint which is ready to send. Since the FULL and EMPTY outputs are synchronized to the clock domains containing the sending and receiving components respectively but also dependent on conditions from the opposite sides, the FIFO then effectively becomes not only a means to transfer data between these two domains but also a point of unified protocol translation between the contained devices. In other words, even though the sending component may be sending in control bits in parallel with the data, the only way it knows if the receiving component is no longer ready to receive is if the FIFO shows its full.

In situations where a smaller bus has to be expanded to a larger bus the speed conversion scheme described above is used but in an expanded form. One or more modulus operations are also included in the conversion process based on how many times the bus needs to be up-converted. For example, in converting a 32 bit bus to a 128 bit bus, the arriving 32 bit data is first stored in either the top or bottom word slot of a 64 bit register based on a modulus two operation. After two writes in this manner, the register is full and so its contents are transferred to a 64-bit FIFO (the largest single size included in the vendor provided libraries), causing the FIFO's EMPTY output to go low at the next clock cycle of the receiving component's clock domain. At the receiving side, as soon as EMPTY is seen as low, the same modulus two operation is used to then write two sequential 64-bit values to the upper and lower double-word slots of a 128-bit register and as soon as this register is full its contents are then transferred to the receiving component.

Figure 3.1: Larger to Smaller BUS Conversion

If a larger to smaller bus conversion is required then, again, the same speed conversion is used but in a slightly modified form. In this case, multiple FIFOs of the width of the smaller receiving bus are placed so that their combined input width is equal to the size of the larger bus. At every write cycle from the larger bus, all the FIFOs are written to in parallel with set segments of this value which causes their EMPTY outputs to all go low at the same time. As soon as logic in the receiving side detects that the FIFOs are no longer empty it then starts reading from each FIFO output individually in a cyclic fashion until they are seen as empty again. At each read then the data is transferred to the component on the receiving end and in this regard the data is being transferred from the larger bus to the smaller bus in a round-robin manner.

#### **3.1.2** Signal Transformations

For the most part the components in each clock domain speak to those in other domains exclusively through intermediary FIFOs (discussed in the BUS Transformation section), however, when conditional logic absolutely has to be translated on its own, individual memory elements are employed. If a signal from a slower clock region needs to be sent to a logic operating in a faster one then the signal is passed through a series of memory elements and its value is read by the faster logic only as long as it has only propagated through the first memory element only. If on the other hand a signal from a faster operating region has to be sent to a slower one then it is run through two series of memory elements, one on the fast side and one on the slow side. The sequence on the fast side is long enough to where at least one will show high at the rising edge of the slower clock no matter where the original signal fell within the slower period and the sequence in the slower side is used as in the slower to faster conversion to ensure that only one of the faster memory element outputs is detected by the slower logic per pulse.

## **3.2** MainBus Interface

The development board was provided with, among other example sources, two Verilog modules which together can be used without modification to allow a design implemented in any of the FPGAs to communicate over the MainBus. The transaction demonstrated by these sources involves having a master endpoint, in the case of this project a PC connected to the board via USB, first write an address to the bus while raising a read or write flag and an FPGA endpoint then either writing data back to the bus or writing data provided by the master endpoint to an internal register. For purposes of this design, this interfacing logic is used in a significantly expanded form to accommodate a protocol which allows for read/write access to status registers from various sections of the design logic, the parser status BRAMs and the DDR2 RAM. Furthermore, while the specification for this bus allows for more than one of the FPGAs to be active and responding to requests from the master endpoint, this feature is unused in this project as only one FPGA chip is currently required in the overall design.

The intent of this section is to provide an overview of the MainBus protocol developed for this project. For its duration any references made to interactions with the MainBus should be taken as meaning that the master endpoint involved is a PC communicating with the board over its USB interface and that accordingly any data written to the bus by the FPGA is intended for this destination.

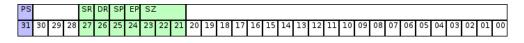

### 3.2.1 MainBus Write to Parser Chain

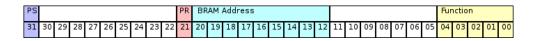

Figure 3.2: MainBus Write Control Word

The current design treats all write requests from the MainBus in which the PS flag in the address word is set low as requests to write packet frame data to the parser chain. The fields in the green coloured area of Figure 3.2 correlate to the signals of the parser bus protocol discussed in the Parser Chain section of the current chapter. Each 32 bit segment of the packet frame is transmitted to the packet parser bus in parallel with a copy of all these signals using the same clock domain conversion scheme used throughout the design. A controller module at the point of entry into the parser chain translates the control flag frame into the individual signals recognized on the parser chain bus. The controller then transmits the packet and the control signals as if it was a parser itself as long as the bus conversion FIFOs containing the packet segments and signal frames are not empty.

| Name                | Operation                          |

|---------------------|------------------------------------|

| SR                  | Sender is ready to transmit data   |

| DR                  | Receiver is ready to receive data  |

| $\operatorname{SP}$ | Start of the packet is being sent  |

| $\mathbf{EP}$       | End of the Packet is being sent    |

| SZ                  | Size in bytes of last transmission |

Table 3.1: Packet Parser BUS Control Flags

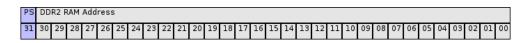

### 3.2.2 MainBus to DDR2 Ram

Figure 3.3: MainBus DDR2 Read/Write Control Word

Figure 3.3 shows the format of the address word which is expected by the design during a transaction between the MainBus and the DDR2 RAM memory. This event is triggered

by setting the PS (Path Select) flag within the address word high during either a read or write operation through the bus. As also shown in the illustration, the remainder of the address word is then checked for the physical address in the DDR2 RAM upon which the transfer should be based.

If a write operation is initiated by the MainBus, such as when the partial bitstreams for the parsers are being uploaded to the development board, then the data provided is written to the DDR2 RAM using the process described in the DDR2 Controller portion of the Memory Interface section in this chapter. Four such write operations have to be made to sequential addresses in the DDR2 memory before any data is actually written to the RAM module and then an additional four have to be made before the amount of data written to the memory is the same as one burst write.

If a DDR2 RAM read operation is performed then the data pulled from the egress FIFOs of the DDR2 controller is automatically stored in a series of four FIFOs for later consumption by the smaller bus using the round robin bus transformation scheme described in the BUS and Clock Conversion section also found in this chapter. The data now residing within these FIFOs can then be read onto the actual MainBus by reading from specific addresses which are reserved specifically for this purpose and which cannot be read from directly. To read back all the data returned by one read request these addresses have to be read in the correct order twice for a total of eight reads or 256 bits of data. These special addresses as well as the returned portion of data they represent are listed in table 3.2.

| Address (0x) | Data Portion (bit offset) |

|--------------|---------------------------|

| EFFFFFFFF    | 127:96                    |

| EFFFFFFE     | 95:64                     |

| EFFFFFFD     | 63:32                     |

| EFFFFFFC     | 31:0                      |

Table 3.2: MainBus DDR2 Special Read Addresses

#### 3.2.3 MainBus System Access

Figure 3.4: MainBus Read Control Word

When the system sees the PS flag low during a read then the address word format shown in Figure 3.4 can be used to dump information regarding the current state of operation of the design to the MainBus. Table 3.3 can be referred to for an overview of what type of information would be returned based on the code provided in the Function field.

The PR (Parser Request) flag and BRAM Address fields are used in conjunction with the NSPI operations to access the info dumps made by the parsers as described in the Parser Chain section of this chapter. The NSPI\_REQRES command can be issued with the PR flag set to high to trigger a read request from the BRAM associated with the second parser stage or to low to trigger the same request from the BRAM storing info from the first parser stage. In either case then the BRAM Address field is used with this same command provide the direct offset within the BRAM selected from where to retrieve the info data from. After the NSPI\_REQRES command is issued the info data is not yet presented to the MainBus as the BRAM interface is 64 bits wide. To actually place the data on the bus the NSPI\_READRES commands must be used to access both the upper and lower words of the info data from temporary 64-bit register.

| Name            | Code $(0x)$ | Description                                             |

|-----------------|-------------|---------------------------------------------------------|

| FIFO_STATUS     | 00          | Get State of operation of the MainBus interfacing logic |

| FIFO_LASTDATA   | 01          | Get Last packet written to the parser chain             |

| FIFO_VERSION    | 02          | Get Current version of the design                       |

| NSPI_REQRES     | 03          | Start a parser info dump read request                   |

| NSPI_READRES_HI | 04          | Get upper word of parser info dump                      |

| NSPI_READRES_LO | 05          | Get lower word of parser info dump                      |

| ICAP_LAST       | 06          | Get last word written to the ICAP                       |

Table 3.3: Read Control Functions

The FIFO\_STATUS function is used to query the state of the protocol logic itself and return its value to the MainBus in the form of a 32 bit hex value. Table 3.4 lists all of FIFO\_STATUS state codes and their meanings.

| State Code (0x) | Description                                                 |

|-----------------|-------------------------------------------------------------|

| DA7A2EC1        | Last packet portion successfully passed to the parser chain |

| DA7AFA2F        | Last packet portion dropped owing to block in parser chain  |

| DA7AB10C        | Last packet portion dropped for any other reason            |

| 9E7AD2E5        | Last parser info dump request successfully made             |

| ABADC0DE        | Unrecognized operation requested from logic                 |

Table 3.4: MainBus Interfacing Logic Status Codes

## **3.3** Memory Interface

While the large sizes of the generated partial bitstreams already necessitated the use of external memory, it was decided that the on-device BRAM memory would still be used for capturing the info output of the parsers to allow for the overall simplification of the design DDR2 memory was chosen as the external memory type as a module was already available on hand of sufficient size.

This section describes the interfaces created to access both these memory resources.

### 3.3.1 DDR2 Controller

In its most basic mode of operation, the DDR2 controller core requires that the data being written to it is provided in 256 bit chunks per write cycle as it itself writes 128 bits of data to the actual physical RAM at both the rising and falling edges of the clock signal. Masking, however, is allowed which means that one or more 8 bit wide subsections of the 256 bit wide write data can be set to be ignored per write. Any sequential logic directly interacting with the controller core must operate at a clock frequency as generated by a PLL (Phase Lock Loop) within the core itself, meaning that it resides within its own clock domain.

The protocol to write or read to the controller core is fairly straightforward even though quite a few inputs are required. A write is initiated by first setting both the data write enable and address write enable inputs high and then keeping the data write enable high for another clock cycle while bringing the address write enable low. During the first clock cycle mentioned the first 128 bits of the input data should be provided along with the associated masking bits and starting address while on the second clock cycle the second 128 bits should be given along with any needed masking bits but without any address. A read request is signalled by first setting the address enable and control type (to signify this is a read transaction) high and then on the same clock cycle providing an address.

The logic handling the MainBus to DDR2 memory data transaction consists of essentially the bus up-conversion scheme covered in the BUS Transformation section, the protocol for the DDR2 controller just discussed and an additional FIFO for passing addresses and control information. The address and control bits FIFO is both written to and then read from at the same time as the 64 bit FIFO storing the data which essentially allows the data, address and control bits to be en-queued while still enforcing their association. As in any other logic handling a bus transformation in this design, the logic between the core controller and the FIFOs starts reading from these components as soon as their EMPTY outputs both show low, at which point it checks for the type of transaction required by what it pulls off of the address and control FIFO.

If the command pulled off of the address and control FIFO is a write request then the logic, as expected, up-converts the incoming data to 128 bits but then must process it through two additional steps before it is ready to be sent to the core controller. As the controller core is expecting 256 bits of data and only half of that is available at this point, the same 128 bit data is provided twice to the controller in one write and another modulus two operation is then used to mask either first 128 bits or the second. This allows the logic to spread out a write request across four clock cycles instead of the regular two when it is coupled with a modulus 8 operation to restrict the address where the data is being written to.

If, on the other hand, the command pulled off the address and control FIFO is a read request then addresses are pulled from the the same FIFO and used in the core controller read protocol until the EMPTY flag is raised. The width of the data per address returned is also 256 bits and it is stored layered in two 64 bit egress FIFOs as soon as the core controller raises its data ready flag. Any component requesting data from the RAM then is notified that the data is ready by when these output FIFOs no longer show that they are empty.

#### 3.3.2 On-Chip BRAM

Interfacing with the BRAM on the FPGA chip can be handled at varying levels of abstraction depending on the amount of control needed over the functionality and resource usage of the resulting component on fabric. For the purpose of this design, the highest level was used as the on-chip RAM is only used to store debugging information and does not figure into the resource requirements of the parser chain. As such, the MMU logic which is responsible for passing the output from the parsers to this memory only has to raise the write-ready signal on the rising clock edge to pass the parser info output to these RAMS.

## **3.4** Dynamic Parser Configuration Arbitration

To explore the use of self-initiated partial reconfiguration as a configuration option in the design a logic framework was created which both autonomously handles the reconfiguration transaction and reroutes traffic based on the configuration status of each of the parsing stages. This area of the design also contains constructs required for the partially reconfigurable design flow as well as those which allow the static portions to continue to function as intended no matter the configuration status of the parsers.

### 3.4.1 ICAP Controller

Initiating a transaction with the ICAP (Internal Configuration Access Port) requires following a fairly basic protocol which is simplified even further if only write functionality or partial reconfiguration is required as is the case with this design. Effectively, the process involves tying down a control input to indicate that the functionality required from the port will always be a write and then driving the clock enable input to active low whenever data is to be written to the FPGA, driving it high if there is an interruption in the data streaming in and then finally driving the clock enable high whenever the input data has finished streaming in. The data itself may be either input at a width of 8,16 or 32 bits depending on a parameter passed to ICAP module and finally care must be take to make sure it is byte-swapped [9].

The whole transaction for configuring the FPGA through the ICAP should technically be treated as a one sided affair, however, during configuration the output port normally used for reads will also automatically output the configuration status of the FPGA. This feature is used for debugging purposes in the project to monitor when the FPGA has reported that the configuration process has started and if it has detected that the configuration process has ended successfully or otherwise.

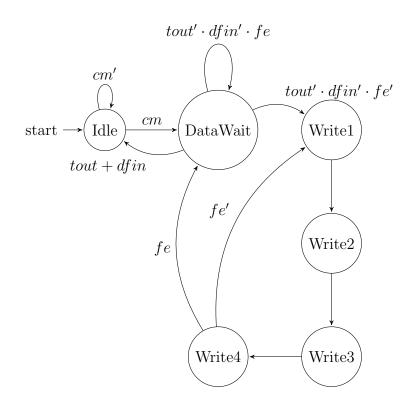

Figure 3.5: ICAP Write FSM

The first major complication which arises in regards to the configuration process with this design is ensuring that it is only triggered at the right time. The decision as to whether to program a parser stage occurs during the processing of a packet in the stage directly preceding it. This earlier stage will notify the controller of the types of packets passing through it by providing it with their EtherType fields. The controller will then in turn first check whether the next stage has already been configured to handle this type and if not will then run the field through an internal CAM memory to see if the new parser type is supported. If the CAM does not return a match then the packet is not supported and the configuration of the next stage will not take place; if there is a match then the configuration process will start and the address returned by the CAM will be translated to an offset within the RAM from where to start pulling the configuration data from.

The second significant complication which presents itself within this process is making sure that the incoming data is converted to a format acceptable by the ICAP port. As is the case with any other read request it is presented with, the DDR2 controller returns the configuration data in chunks of 256 bits at a clock rate dictated by its internal PLL. The ICAP, however, requires that this data is handed off to it at its maximum supported clock rate and in segments of 32 bits. To accommodate this discrepancy in both width and speed, when passing the configuration data between these two components the Round-Robin FIFO approach is used as discussed in the Bus Transformation section with a depth of four.

#### **3.4.2** Parser Black-Box Wrappers

One of the key requirements of successfully implementing a partially reconfigurable design is ensuring that all modules which are to reside within the same reconfigurable region expose a uniform and buffered IO to the rest of the logic in the design. This is accomplished by first routing the static portion of the design with black-box modules instantiated in the place of any reconfigurable logic and then separately routing the modules which are to reside in these areas, making sure that every one has the exact same buffered input and output ports. The black-box modules are simply modules which have been emptied of all logic except for the input and output ports and in this sense can be seen as place holders for any of the reconfigurable logic which may be placed inside of them.

For this design an additional wrapper level module was created to surround the required black-box modules and act as a multiplexer for the data passing through, an on/off indicator to let the rest of the logic know whether the region is configured or not and finally as a trigger to configure the next parser stage. Essentially if the inner black-box region, a black-box placeholder for a parser, is not configured or in the process of being configured then any packets arriving at the boundaries of the outer wrapper are rerouted to bypass the parser completely and the rest of the static logic is told to ignore any of its info status outputs. The trigger functionality within the outer wrapper can be seen as a packet pre-parser which notifies the ICAP controller of the packet types that pass through it so the controller can make the decision as to whether the following parser stage should be configured.

The trigger functionality of the outer wrapper is essentially a packet parser stripped of everything but its EtherType detection functionality and augmented with the ability to both suggest a configuration for the next parser stage and to store the configuration type for its parser. At the correct offsets within the packet the pre-parser will take a snapshot of the packet's EtherType within a register and then drive a wire shared with the ICAP Controller high to indicate that this configuration type is ready to be considered as a candidate for configuring the next stage. As covered in the ICAP Controller section, the ICAP Controller will then check with the EtherType stored by the trigger of the next stage to see whether the configuration process should be started. The configuration type of a stage is stored in the form of a registered EtherType and is empty (all signals in the bus are low) if the parser contained within the wrapper is un-configured.

# 3.5 Parser Chain

To allow for the possibility of eventually testing the design within the actual data plane architecture of the network switch it was pulled from, the outer wrapper for both the parsers was designed to present the same bus and protocol as was expected by the original interfaced components. As such the outer wrapper includes a variable length info status bus with a wire to indicate that the info is ready, two 64 bit buses for transmitting packets to and from the parser, a send/receive ready input/output for the previous stage and a send/receive ready output/input for the next stage. The protocol used between the component which are connected with this setup is fairly basic and involves really only checking whether both the sender is ready to send and the receiver is ready to receive before sending the data at each clock cycle. Additionally, a start and end of packet signal are also interchanged to simplify the calculations the receiving parser has to do to calculate the offset of the data within the packet which it is currently receiving. The protocol does support a supplementary extension in the form of an error in transmission signal but, as it is unused in the switch architecture from which this project is derived, the associated pins on wrapper are currently always left open.

Figure 3.6: Basic Parser Chain Layout

The intent of the multiple parser stage setup used both in the data plane of the source switch as well as in this design is to provide a compartmentalized parsing engine where in each stage handles just one level of packet encapsulation before stripping it off and passing the remainder of the packet to the next stage. Whether a parser stage supports extracting meaningful data from the level of encapsulation it receives is based on whether key fields within the header such as the EtherType match the type it is configured for. These field also determine whether the layer of encapsulation should be stripped off before passing the packet to the next stage and in this sense the packets can be just forwarded along unaltered if they are not supported.

In the original switch architecture, the level 2 parser is used in conjunction with several others to handle the extraction of all the pertinent data link layer fields from the Ethernet frame. It is mainly responsible for extracting the source and destination MAC addresses for forwarding purposes. Once it extracts these values, it passes the remainder of the Ethernet frame header along with the payload to the other data link layer parsers down the chain which in turn determine if the header is embedded with any additional fields related to VLAN and SNAP functionality. In the research presented, none of these extra features were tested and as such only this initial level 2 parser was required to represent the processing the packet would go through at its level.

#### 3.5.1 Parser Chain Status

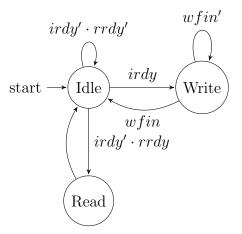

Figure 3.7: MMU State Machine

Each parser effectively outputs its status through a series of info buses shortly after it receives a packet and has had time to process it. To take advantage of this feature, a basic MMU (Memory Management Unit) was created which sequentially dumps the output of the info bus for each packet received to the next free location on one of two dedicated BRAM (Block RAM) memories on the FPGA. After a series of unique packets have been sent through the parser chain, the same MMU can be used to access each of the BRAMs at varying offsets. In this sense, the point at which the switch was able to start processing a new packet type in a packet stream is determined by comparing the data sent in to the data registered at each offset by the parser being reconfigured as well as any other in the chain.

While the width of the info bus on the outer parser wrapper must always be the same as necessitated by it being a reconfigurable module, the actual widths of the info buses of the parsers contained within the wrapper may vary and so the MMU was designed to be flexible in the actual amount of data it writes to allow for more efficient use of the on chip memory and to speed up the process when possible. Referring to the FSM in Figure 3.7, when a parser indicates to the MMU that info is ready with the irdy signal it also passes a width value during the transition between the Idle and Write states. During this same transition the MMU divides the value by the bus width of the BRAM instances used in the design, 64, and then compares the new value against an up counter in the Write state to determine whether to continue writing or not as represented in the FSM by the wfin signal. During the write state the info value is right shifted by 64 and its lowest double word is stored at the memory address shown in the up counter. Finally, during the transition from the the Write state back to the Idle state the last value of the up-counter is stored as the new address offset from which to start writing the next packet dump. The MMU can run two such processes concurrently for each of the parsers in the chain.

The read back of these values which is initiated by the NSPLREQRES MainBus initiated operation discussed in Section 3.2.3 can only occur if the MMU is currently not in a Write state and has lower priority if the MMU gets both requests at the same time. Only one clock cycle is required to return the value requested after which the MMU flags the data is ready and the MainBus interfacing logic stores it for later access by additional commands.

## Chapter 4

# Theory of Operation: Coarse Grained

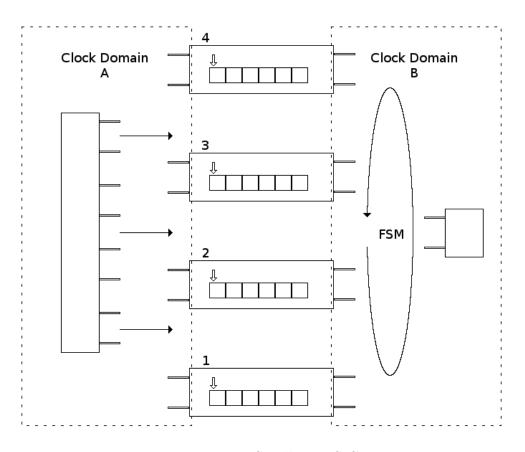

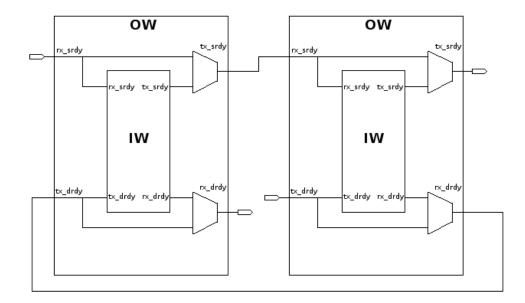

The coarse grained test-case is built using the same framework as used in the fine grained one and differs only in the implementation of the parsers and the interceding buses. This chapter covers only the abstracted functionality of the operational units which have been changed between the designs.

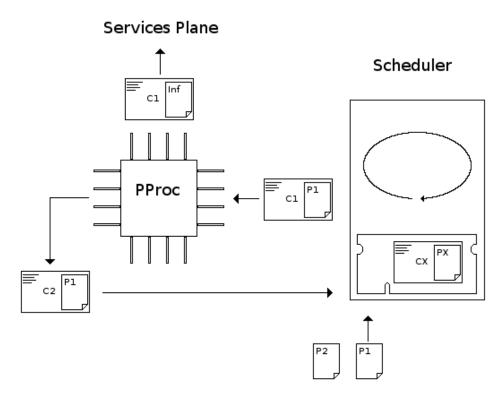

## 4.1 Parser Processor

While both the fine grained and coarse grained architectures are built on top of FPGA technology and are therefore configured at the LUT level, in regards to the reconfiguration process of the parser chain itself, the parser processors are considered the base unit of configuration in the latter implementation. Throughout most of the parsing process the actual operation being performed on the packet data can be generalized as being either a conditional or unconditional extraction of data from varying offsets within the stream. As such the coarse grained processor has been designed as a general purpose compare and extract engine which can be programmed to perform this operation against multiple values both stored and found.

Beyond the parsing state, a parsing element only has two other modes of operation, idle and passing the extracted payload to the next stage, both of which entail standard processes largely independent from the parsing one. This fact was exploited in the processor to decrease the size of the programming memory required by hard coding these states and extracting the one responsible for parsing as a module which is referred to as the core of the parser from this point on. In this sense the processor logic consists of a dynamic state machine, the parsing state of which can be extended to include additional sub-states depending on the amount of parsing cores inserted.

#### 4.1.1 Parser Core

Currently, two different sized parsing core elements have been designed for this research, a smaller one which can be programmed to have the equivalent parsing capability of both a level 2 and TRILL parser in the original architecture of the switch and a larger one which can be configured to function as half of a level 3 parser as well as the two parsing levels already mentioned. As soon as it receives notification to enter the parsing state, each parser core can be seen as running through a process which always starts with a check for the type of packet passing in, then continues through a variable amount of comparisons and finally finishes after passing on info extracted at certain offsets. The actual determination of details such as at what overall offset each of these steps should take place and if the packet parsing should continue if a comparison fails a constraint is handled by a set of flags stored in 128 bits of internal configuration memory. The only major differences between the two core sizes, in terms of this flow, lie in the amount and flexibility of the comparisons which can be performed (the initial data type check is also considered a comparison in this sense) and the formatting of the flags within the memory.

The pseudo code in 4.1.1 outlines the general flow of a core's parsing process and how it is shaped by the flags stored in the parsing element's configuration memory. The IF statement starting on line 4.1.1.10 specifically shows an abstraction of one possible setup of the comparisons step discussed earlier. When the counter initialized on line 4.1.1.3 reaches the first compare count stored in the configuration memory, the configured comparison type is triggered between two fields. If the comparison fails then the error flag is set, the parsing procedure is stopped and the core notifies the rest of the parser logic to pass the remainder of the un-extracted packet to the next parser in the chain. The results of the comparison can be masked to show as always passing if the extraction of the info from the packet is desired unconditionally.

Algorithm 4.1.1 Partial Parsing State Pseudo code

```

1: err \leftarrow false

\triangleright error encountered

2: fr \leftarrow \mathbf{false}

\triangleright finished returning info

3: pctr \leftarrow 0

\triangleright parser counter

4: c1r \leftarrow 1

\triangleright flags that the parser should care about the outcome of this comparison

5: while \neg packet end \land \neg fr \land \neg err do

if ¬sender ready then

6:

continue

7:

end if

8:

pctr \leftarrow pctr + 1

9:

if compare 1 count \wedge compare 1 failed \wedge c1r then

10:

err \leftarrow true

11:

end if

12:

if end of info count then

13:

PASSINFO(Info)

14:

fr \leftarrow \mathbf{true}

end if

15:

16: end while

```

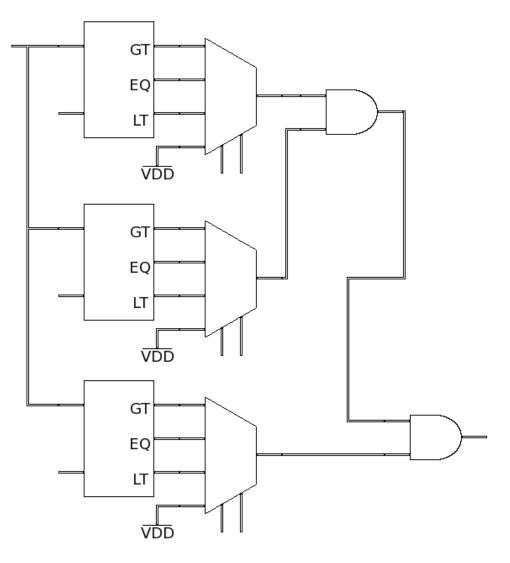

In the case of the smaller parser core the comparison type can only be an equality during the initial type check and the first and second fields can only be of type extracted and stored respectively. With the larger parser the comparison type can be set to an equality or either of the strict inequalities (less than or greater than) and can involve multiple fields both stored in the configuration memory and those extracted. Furthermore, whereas the smaller parser can only perform one comparison at a time the larger parser can perform a range of between one to three comparisons simultaneously via an embedded chain of programmable (configuration memory space shared with the core) hardware comparators illustrated in 4.1.

Beyond the on state in which the parsing states are embedded the parser core has two other states of operation, off and being programmed. Both of these states can be triggered at any time by supervisor input pins and both are, by design, preemptive of any parsing functionality. When the core is in the off state, it cannot be triggered into starting the parsing process by the ready input flag from another core sending data to it and as such will prevent the core from consuming any of the packet until it has been fully configured. When the core is in the programming state it treats the data coming in as configuration packets (see 4.3), meaning that it will store all data coming in at this time in its configuration memory. After all the configuration data has been received, the core will then go through a basic initialization sequence, entailing of mainly the expansion of certain received variables, and then transition to the off or on state depending on the status of the supervisor pins..

Figure 4.1: Parser Comparator Logic Unit

The on state of the core is also transitioned to by way of the input supervisor pins and consists of both an active and idle parsing sub-state. The active sub-state consists of the process described in pseudo code covered earlier and is, as mentioned earlier, triggered by an external core. Stored state variables in the configuration memory determine what mode of operation the parser logic external to the core should go to in both the case where parsing process exits with packet data remaining and the case when it exits because the packet ended early. Currently in the former type of exit the external logic is always set to move to passing the data on to the next parser and in the latter it is set to go idle, but this extensibility is included in the design to allow for future research into mapping efficiency versus granularity.

#### 4.1.2 Small Parser Core Operation

| 32  | EthCount    | EthShift    |       | EthWidth |          | EtherType   |                   |                   |

|-----|-------------|-------------|-------|----------|----------|-------------|-------------------|-------------------|

|     | 31 30 29 28 | 27 26 25 24 | 23 22 | 21 20 19 | 18 17 16 | 15 14 13 12 | 11 10 09 08 07 06 | 05 04 03 02 01 00 |

| 64  | RE1Count    | RE1Shift    |       | RE1Width | I        | RS1Count    | RS1Shift          | RS1Width          |

|     | 31 30 29 28 | 27 26 25 24 | 23 22 | 21 20 19 | 18 17 16 | 15 14 13 12 | 11 10 09 08 07 06 | 05 04 03 02 01 00 |

| 96  | RE2Count    | RE2Shift    |       | RE2Width | I        | RS2Count    | RS2Shift          | RS2Width          |

|     | 31 30 29 28 | 27 26 25 24 | 23 22 | 21 20 19 | 18 17 16 | 15 14 13 12 | 11 10 09 08 07 06 | 05 04 03 02 01 00 |

| 128 | EPState     | ENState     | Res   |          |          | PID         | RES IG TotalC     | ount              |

|     | 31 30 29 28 | 27 26 25 24 | 23 22 | 21 20 19 | 18 17 16 | 15 14 13 12 | 11 10 09 08 07 06 | 05 04 03 02 01 00 |

Figure 4.2: Small Parser Core Memory Map

The primary function of the small parser core is to simply pull out one or two consecutive groups of fields from a packet, apply basic formatting to the extracted data and then send it up for consideration by higher functionality in the network switch. The core can either be configured to pull out this data unconditionally or based on whether it detects that a field extracted at a certain offset matches a stored value. This check is mainly intended to serve as the EtherType check during the level two or TRILL (can be considered level 2.5) parsing of data sent over Ethernet. If the core is set to extract info unconditionally then it will always return the checked value on a separate bus from its info bus at the same time it returns the info, but if the core is set to extract conditionally then it will only return the checked value and the info on their respective buses if the checked value matches the stored value. The level two parser uses the unconditional setup while the TRILL parser uses the conditional setup of this parser class.

Figure 4.2 illustrates how the small parser core interprets its configuration memory. The fields prepended with **Eth** are responsible for determining where to look for the the data type check and the **EtherType** field itself is the value against which this check should be performed. As the data actually returned may be greater than a 64 bits, start and end

locations have to be provided to take in account for these larger return types for both the first and second info groups designated as **R1** and **R2**. The significance of the rest of the parameters responsible for driving this core are explained in table 4.1.

| Name       | Use                                                                         |

|------------|-----------------------------------------------------------------------------|

| EtherType  | Initial data field value to run check against                               |

| Width      | Amount of bits to extract for a given field in a specified data chunk       |

| Shift      | Offset of data to be extracted from the end of a specified data chunk       |

| Count      | The data chunk to check for a given field                                   |

| TotalCount | Total amount of chunks to parse before passing the packet                   |

| IG         | Whether to conditionally or unconditionally extract info                    |

| PID        | Parser ID to match against during programming                               |

| ENState    | State enumeration to visit if packet is not finished after parsing          |

| EPState    | State enumeration to visit if packet is finished before parsing is complete |

Table 4.1: Small Parser Core Parameters

#### 4.1.3 Large Parser Core Operation

In the larger core the ability to pull out more than one group of fields has been sacrificed. along with the ability to dynamically set the end states and finally the resolution of some of the other fields, for the ability to perform additional checks against the incoming packet. This core can programmed to pull out two additional fields beyond the initial value check field and to store two more fields in memory all for the purpose of performing one additional more complex check. The second check is driven by the comparator logic unit shown in figure 4.1 which can be programmed to perform one to three checks against the first of these values pulled with the other three. This additional check is included for the ability to ensure that the Header Length field in IP packets is between two values and that it is less than the Packet Length field. As in the original parser architecture if any of these checks fails then the parsing core releases the packet to the remainder of the logic for forwarding to the next parser. The first check is used in context of IP packets to check for the correct version so for example to ensure that an IPv4 level 3 parser can handle a packet, the EtherType field is set to 0x4. After these two check the parser can only perform an extraction of info and as such cannot act as a full level three parser as additional fields related to packets fragmentation still need to be handled.

| 32  | RSW EC      | EthS | Shift |     |      |    | Eth  | Wid | th  |     |      |    | Eth  | nerTy | ype |     |      |    |      |       |     |      |    |    |     |      |    |    |

|-----|-------------|------|-------|-----|------|----|------|-----|-----|-----|------|----|------|-------|-----|-----|------|----|------|-------|-----|------|----|----|-----|------|----|----|

|     | 31 30 29 28 | 27 2 | 26 25 | 24  | 23   | 22 | 21   | 20  | 19  | 18  | 17   | 16 | 15   | 14    | 13  | 12  | 11   | 10 | 09   | 08    | 07  | 06   | 05 | 04 | 03  | 02   | 01 | 00 |

| 64  | V1Width     | REC  | ount  | RE  | 1Shi | ft |      |     |     | RE1 | Vidt | h  |      |       |     | RSC | Coun | t  | RSS  | Shift |     |      |    |    | RSI | Nidt | h  |    |

|     | 31 30 29 28 | 27 2 | 26 25 | 24  | 23   | 22 | 21   | 20  | 19  | 18  | 17   | 16 | 15   | 14    | 13  | 12  | 11   | 10 | 09   | 08    | 07  | 06   | 05 | 04 | 03  | 02   | 01 | 00 |

| 96  | SetValue1   |      | V2    | Cor | int  | V2 | 2Shi | ft  |     |     |      | V  | 2Wic | ith   |     |     |      | VI | .Cou | int   | V   | 1Shi | ft |    |     |      | V1 | W  |

|     | 31 30 29 28 | 27 2 | 26 25 | 24  | 23   | 22 | 21   | 20  | 19  | 18  | 17   | 16 | 15   | 14    | 13  | 12  | 11   | 10 | 09   | 08    | 07  | 06   | 05 | 04 | 03  | 02   | 01 | 00 |

| 128 | PID         | IG ( | CLUOp |     |      |    |      | Set | Val | ue2 |      |    |      |       |     |     |      |    | Se   | tVal  | uel |      |    |    |     |      |    |    |

|     | 31 30 29 28 | 27 2 | 26 25 | 24  | 23   | 22 | 21   | 20  | 19  | 18  | 17   | 16 | 15   | 14    | 13  | 12  | 11   | 10 | 09   | 08    | 07  | 06   | 05 | 04 | 03  | 02   | 01 | 00 |

Figure 4.3: Large Parser Core Memory Map

Figure 4.3 illustrates how the large parser core interprets its configuration memory. The fields prefixed with Eth and R are responsible for finding the first check and the return values respectively and serve the same function as in the small parser core. The fields starting with V1 are required to find the first value in the packet against which all the remaining values will be checked, both found (V2) and stored (SetValue1,SetValue2). The purpose of the rest of the parameters responsible for driving this core are outlined in table 4.2.

| Name      | Use                                                                   |

|-----------|-----------------------------------------------------------------------|

| EtherType | Initial data field value to run check against                         |

| Width     | Amount of bits to extract for a given field in a specified data chunk |

| Shift     | Offset of data to be extracted from the end of a specified data chunk |

| Count     | The data chunk to check for a given field                             |

| IG        | First check mask                                                      |

| PID       | Parser ID to match against during programming                         |